Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

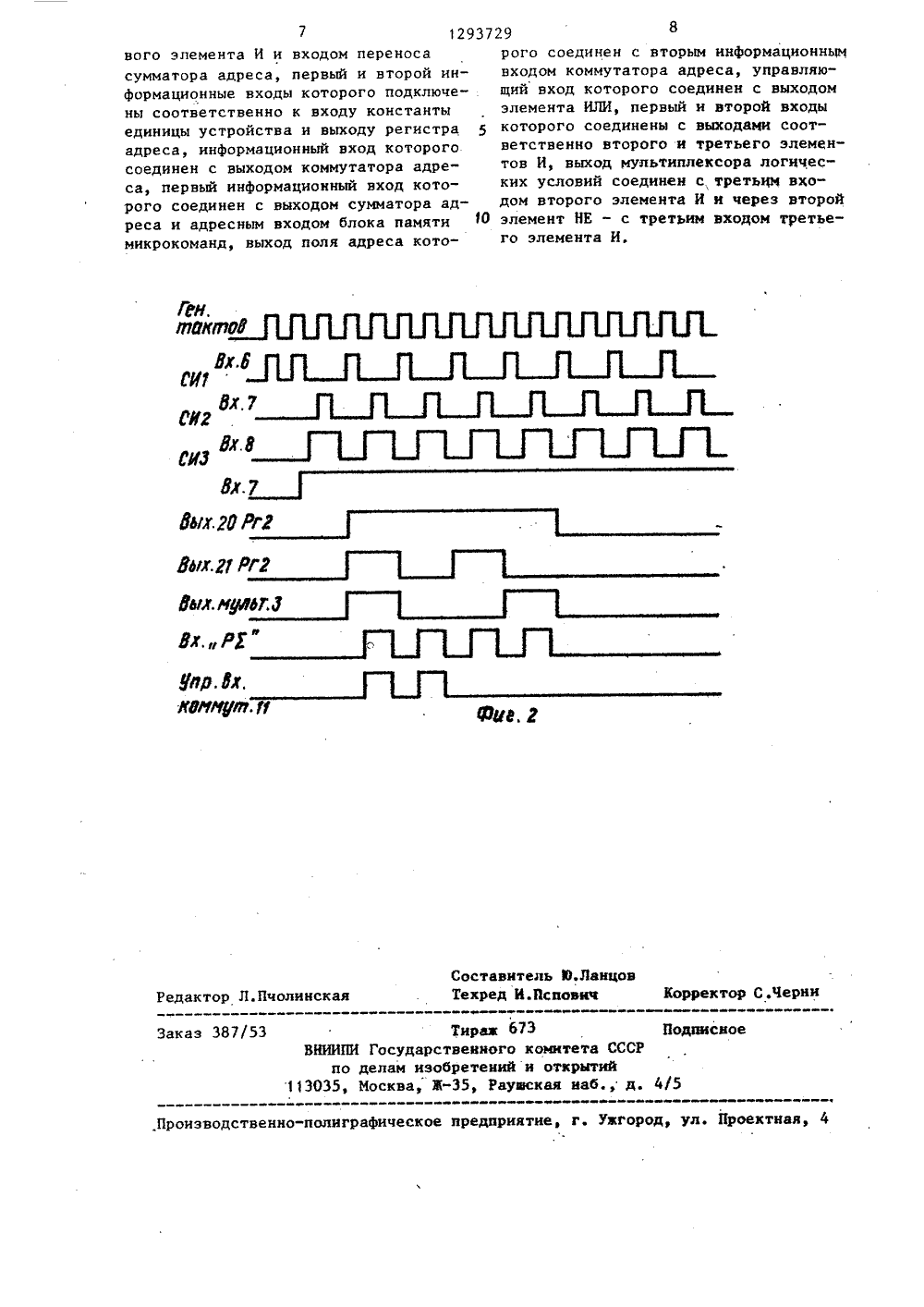

СОВЕТСКИ А 1 РЕСПУБЛИК В 4 С 06 Г 9 ГОСУД ДРС ПО ДЕЛА АНИЕ ИЗОБРЕТЕН Н АВТОРСКОМУ СВИДЕТЕЛЬ 50882/24-24(54) МИ УПРАВЛЕ (57) Из программ эффекти в вычис ЭВМ, нр тем, а В Т икроолеевано ример в их сисмикро(21) З 7 (22) 04 (46) 28 (72) А. А.В.Пан (53) 68 (56) Ма ципы ор Машинос ЕННЫЙ КОМИТЕТ ССЗОБРЕтЕНИй И ОТНРЦТ РОПРОГРАММНОЕ УСТРОИИЯ бретение относится к ному управлению и на но может быть исполь ительной технике, на построении управляющ акже самостоятельных программных автоматов. Цель изобретения - повышение быстродействия,Устройство содержит блок 1 памятимикрокоманд, регистр 2 микрокоманд,мультиплексор 3 логических условий,блок 4 анализа логических условий,содержащий два элемента НЕ 14, 15,три элемента И 16, 17, 18 и элементИЛИ 19, сумматор 9 адреса, регистрадреса и коммутатор 11 адреса. Введение признака типа перехода в формамикрокоманды, блока анализа логических условий, сумматора адреса и коммутатора адреса позволили не закладывать в микропрограмму специальныеуправляющие микрокоманды, что позволило достигнуть цели изобретения,2 ил.1293729 на информационный вход коммутатора11, но не проходит на выход последнего,В момент запуска устройство синхронизации (не показано) вырабатывает только серию первых тактовых сигналов СИ 1, поступающих на вход 6устройства, соединенный с входом Срегистра 2 микрокоманд. Передним 10 фронтом тактового сигнала СИ 1 содержимое блока 1 памяти переписываетсяв регистр 2 микрокоманд и поступаетна выход 12 устройства для исполнения. Сигнал СИЗ, нырабатынаемый уст ройством синхронизации, равен в данный момент "0".Пусть микрокоманда, выбранная спервой линейки блока 1 памяти и переписанная по переднему фронту СИ 1 в 20 регистр микрокоманд, т.е. выполняемая микрокоманда, неуслонная, Тогдасостояние выхода 20 регистра 2 микрокоманд равно 0. Независимо от состояния выхода мультиплексора 3 усло вий и выхода 21 регистра 2 микрокоманд на входе Р переноса сумматора 9и на управляющем входе коммутатора11 присутствуют сигналы, т.е. напервом и втором выходах блока 4 - ЗО сигналы "0". Изобретение относится к микропрограммному управлению и может быть использован в вычислительной технике, например в ЗВИ, при построении управляющих систем, а также самостоятельных микропрограммных автоматон с микрокомандами, адресные и операционные части которых соизмеримы по разрядности.Цель изобретения - поньпдение быстродействия.На фиг. 1 представлена функциональная схема микропрограммного устройства управления; на фиг.2 - временные диаграммы его функционирования.Устройство содержит блок 1 памяти микрокоманд, регистр 2 микрокоманд, мультиплексор 3 логических условнй, блок 4 анализа логических условий, вход 5 сброса, первый 6, второй 7, и третий 8 синхровходы, сумматор 9 адреса, регистр 10 адреса, коммутатор 11 адреса, выход 12 и группу 13 входов логических условий.Блок анализа логических условий содержит дна элемента НЕ 14 и 15, три элемента Я 16-18 и элемент ИЛИ 19.1(роме того, регистр 2 мнкрокоманд имеет выход 20 признака типа перехода и выход 2 1 признака типа микрокоманды.Устройстно работает следующим образом.П 1.и поступлении сигнала начального запуска по входу 5 устройства регистр 10 адреса устанавливается н исходное нулевое состояние, поступающего на группу входов А сумматора 9, следовательно, на выходе сумматора 9 устанавливается выходное состояние равное единице (поскольку на младшем разряде группы входов В - "1", а на входе Р - "0"), так как на выходе элемента И 16 присутствует сигнал "0" (на обоих входах этого момента - сигналы "0" н данный момент). На унранляющем входе коммутатора 11 также присутствует сигнал "0", и, следовательно, выход коммутатора 11 через свой первый информационный вход подключен к выходу сумматора 9, выходное состояние которого равно единице. Данное выходное состояние сумматора 9 поступает на вход блока 1 памяти. В результате на. выходе блока 1 памяти устанавливается содержимое первой его линейки, поступающее с выхода блока 1 памяти на вход 0 регистра 2 микрокоманд н При снятии сигнала начального запуска с входа 5 устройтво синхронизации начинает вырабатывать (послепрохождения сигнала СИ 1) сигнал СИЗ,35 с поступлением которого н этот моментсостояние выходов блока 4 не изменя.ется.С поступлением сигнала СИ 2, состояние выхода сумматора 9 (единица)40 переписывается (передним Фронтом СИ 2)через коммутатор 11 н регистр 10 адреса, т.е. на выходе регистра 10 адреса устанавливается единичное выходное состояние, которое поступает на45 группу входов А сумматора 9. На ныходе последнего устанавливается состояние равное двум (единица с группывходов А плюс единица с младшего разряда группы входов В),50 В результате по .выходному состоянию сумматора 9 н блоке 1 памяти выбирается вторая линейка, содержимоекоторой поступает с выхода блокапамяти на вход 0 регистра 2 микроко 55 манд и на соответствующий информационный вход коммутатора 11, Однако навыходе коммутатора 11 это состояниевыхода блока 1 памяти пройти не может, так как на управляющем входекоммутатора 11 имеется сигнал "О",а по первому входу поступает значениевыходного сумматора 9.С поступлением следующего тактового сигнала СИ 1 выходное состояние 5блока 1 памяти переписывается (по переднему фронту СИ 1) в регистр 2 микрокоманд и поступает на выход 12 устройства для исполнения, Следовательно, в этом случае (при выполнении неусловной микрокоманды) осуществляетсяестественный (по "+1") способ адресации, а длительность машинного цикла(микрокоманды) равна двум тактам:СИ 1 и СИ 2. 15Рассмотрим работу устройства дляслучая, когда выполняемая микрокоманда, т.е. микрокоманда, выбранная вблоке 1 памяти (например, с 1-й линейки) и переписанная по переднемуфронту СИ 1 в регистр 2 микрокоманд,является условной,Тогда состояние выхода 20 регистра2 микрокоманд равно "1". Это выходноесостояние выхода 20 регистра 2 поступает на соответствующий вход блока 4,На вход А мультиплексора 3 условийпоступает код условия, заложенный ввыполняемой условной микрокоманде. Навыходе 21 регистра 2 микрокоманд может быть сигнал "О" или "1" (в зависимости от того, что было заложенов данной микрокоманде при микропрограммировании),В зависимости от выполнения (не 35выполнения) условия, а так же состояния выхоДа 20 регистра 2 микрокомандв устройстве возможны две ситуации:состояние выхода мультиплексора 3условий и выхода 20 регистра 2 микро 40команд, а следовательно, состояниевходов блока 4 равнозначны или неравнозначны. В каждой из указанных ситуаций формирование адреса следующеймикрокоманды на выполнясмой условноймикрокоманде осуществляется по сво 45ему,Рассмотрим работу устройства в каждой иэ указанных ситуаций.Пусть состояние входов блока 4 равнозначно, т.е. на обоих входахиприсутствует сигнал 1 ипи 0Состояние выхода сумматора 9 р авно единице ( так к ак условлено, что выполняемая условная микрокоманда выбрана с первой линейки блока 1 памяти) . С поступлением сигнала СИЗ на один и э входов элемента И 1 6 на выходе последнего устанавливается сиг 1нал 1 , т ак к ак на втором входе эле - ,мента И 1 6 также имеется сигнал " 1 "с выхода 2 О регистра 2 микр ок ома нд .Сигнал 1 с выхода элемента И1 6 п оступает на первые входы элементовИ 1 7 , 1 8 и на вход Р переноса сумма тора 9, увеличивая содержимое по следне г о ( был о равно 1 ) н а единицу ,т . е . состояние выхода сумматора 9становится равным 2 , По данному вы-.ходн ому состоянию сумматора 9 в блоке 1 памяти выбирается вторая линейк а , содержимое которой поступает н авход П регистра 2 микрокоманд и насоответствующий информационный входкоммутатора 1 1 . На управляющем входекоммутатора 1 1 при наличии сигналаСИЗ присутствует сигнал " 1 " , так к акна выходе элемента ИЛИ 1 9 - сигнал1 при равнозначных состояниях входов блока 4 . Действительно , если со стояние выходов мультиплексора 3 ивыхода 2 1 регистра 2 микр окоманд р авнозначно и равно О, то при наличии сигнала СИЗ на выходе элементаИ 17 устанавливается сигнал "1", апри единичном выходном состоянии входов блока 4 единичное состояние устанавливается (при наличии сигналаСИЗ) на,выходе элемента И 18. Следовательно, в любом из состояний равнозначности входов блока 4 на выходеэлемента ИЛИ 19 и, следрвательно,на управляющем входе коммутатора 11сигнал "1". Выходное состояние блока1 памяти (содержимое 2-й линейки .его)поступает через коммутатор 11 навход В регистра 10 адреса и с поступлением второго тактового сигналаСИ 2 переписывается в регистр 10 адреса (по переднему фронту тактовогосигнала СИ 2).Это выходное состояние регистра10 адреса поступает на группу входовА сумматора 9. Иа выходе сумматора 9устанавливается состояние, равное содержимому выхода регистра 10 (содер- .жимое 2-й линейки блока 1 памяти),увеличенному на 2. Такое состояние .сохраняется на выходе сумматора 9 доокончания сигнала СИЗ,Со снятием СИЗ выходное состояние сумматора 9 уменьаается на единицу (т.к, на входе Р его устанавливается сигнал "0"), т.е. становится равным содержимому второй линейки блока 1 памяти плюс единица. Это выходное соссостояние сумматора 9 и представляет собой адрес следующей микрокоманды5 12937 для данного случая (случай равнозначных входных состояний входов блока 4), Следовательно, во второй линейке блока 1 памяти должен быть закодиро; ван адрес на единицу меньше действи 5 тельного адреса следующей микрокоманды микропрограммы. И по сформированному таким образом адресу в блоке памяти выбирается соответствующая линейка, содержимое которой по переднему фронту СИ 1 записывается в регистр 2 микрокоманд и поступает на информационный выход 12 устройства для выполнения.Рассмотрим работу устройства для случая неравнозначного состояния входов блока 4.Пусть выполняемая условная микро- команда выбрана с 1-й линейки блока 1 памяти и по переднему фронту СИ 1 переписана в регистр 2 микрокоманд. Тогда исходное выходное состояние сумматора равно единице.С поступлением сигнала СИЗ на выходе элемента И 16 устанавливается сигнал "1" (т.к. на обоих входах злемента И 1 6 присутствуют сигналы 1, ) . Сигнал " 1 " с выхода элемента И 1 6 поступает на первые входы элементов И 1 7 и 1 8 и н а вход Р переноса сумматора 9 .На выходе последнего ус танавливается состояние , равное двум ( было равно единице + единица с входа Р ) . Данное выходное состояние (дв а) сум" матор а 9 поступает на вход блока 1 памяти и н а соответствующий информацио н ный вход коммутатора 1 1, на упра" вляющем входе которого присутствует сигнал О . Дейс твител ь но , при любоь неравнозначном выходном состоянии40 входов блока 4 на выходе элемента ЮЩ 19 присутствует сигнал "О", так как на выходах элементов И 17 и 18 в этом случае также присутствуют сигналы ОСледовательно, выходное состояние сумматора 9 поступает через коммутатор 11 на вход П регистра 10 адреса и по переднему Фронту тактового сигнала СИ 2 переписывается в него. На группу входов А сумматора 9 поступает состояние равное двум, а на выходе сумматора до момента окончания сигнала СИЗ устанавливается состояние равное четырем.После снятия сигнала СИЗ на выходе сумматора 9 устанавливается состояние, равное трем (было равно че 29тырем минус единица со входа Р). Это выходное состояние сумматора 9 (три) и является адресом следующей микро- команды,.т.е. адрес следующей микро- команды равен адресу выполняемой (единица) плюс два.Так формируется адрес следующей микрокоманды в случае неравнозначных состояний входов блока 4. По сформированному таким образом адресу в блоке 1 памяти выбирается соответствующая (в данном случае третья) линейка и содержимое ее по переднему фронту тактового сигнала СИ 1 записывается в регистр 2 адреса для выполнения. Дальнейшая работа устройства определяется тем, является выбранная микрокоманда условной или неусловной.Формула и з о б р е т е н и яМикропрограммное устройство управления, содержащее блок памяти микро- команд, регистр микрокоманд, мультиплексор логических условий и регистр адреса, причем выходы поля микроопераций и поля анализа логических условий регистра микрокоманд подключены соответственно к выходу устройства и управляющему входу мультиплексора логических условий, группа информационных входов которого подключена к группе входов логических условий устройства, информационный вход регистра микрокоманд соединен с выходом всех полей блока памяти микрокоманд, синхровход регистра микрокоманд и синхровход регистра адреса подключены соответственно к первому и .второму синхровходам устройства, вход сброса регистра адреса подключен к входу сброса устройства, о т л и - ч а ю щ е е с я тем, что, с целью повышения быстродействия, оно содержит коммутатор адреса, сумматор адреса и блок анализа логический условий, содержащий три элемента И, два элемента НЕ и элемент ИЛИ, причем третий синхровход устройства подключен к первоМу входу первого элемента И, второй вход которого соединен с выходом признака типа перехода регистра микрокоманд, выхоц признака типа микрокоманды которого соединен с первым входом второго элемента И и через первый элемент НЕ подключен к первому входу третьего элемента И, второй вход которого соединен с вторым входом второго элемента И, выходом пер7 1293729 8ного элемента И и входом переноса рого соединен с вторым информационным сумматора адреса, первый и второй ин- входом коммутатора адреса, управляю" формационные входы которого подключе- . щий вход которого соединен с выходом ны соответственно к входу константы элемента ИЛИ, первый и второй входы единицы устройства н выходу регистра 5 которого соединены с выходами соотадреса, информационный вход которого ветственно второго и третьего элеменсоединен с выходом коммутатора адре- тов И, выход мультиплексора логичесса, первый информационный вход кото- ких условий соединен с, третьцм вхорого соединен с выходом сумматора ад- дом второго элемента И и через второй реса и адресным входом блока памяти 10 элемент НЕ - с третьим входом третьемикрокоманд, выход поля адреса кото- го элемента И,ГОН.ЮЮЮ Ьи Г 7 РГР КаР.РХ.ЯОМС Р Составитель В,ЛаицовТехред И.йспович Корректор С .Черни Редактор Л.Пчолинская Подписное Заказ 387/53 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 Юх Е СИдХ. 7 СЮ СЮ 3 Тирам 673 ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 13035, Москва, Ж, Рауаская иаб., д. 4/5

СмотретьЗаявка

3750882, 04.06.1984

ПРЕДПРИЯТИЕ ПЯ А-1736

КАТАШЕВ АЛЕКСАНДР ВАСИЛЬЕВИЧ, МИХАЦКИЙ АЛЬБЕРТ ТИМОФЕЕВИЧ, ПАНГА АЙВАР ВИЛЬФРИДОВИЧ, ПЕТРАКОВ ВЛАДИМИР НИКОЛАЕВИЧ, ЦВЕТКОВ ЯН ЯНОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 28.02.1987

Код ссылки

<a href="https://patents.su/5-1293729-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство для дифференцирования и умножения

Следующий патент: Устройство микропрограммного управления

Случайный патент: Сварочная горелка