Процессор быстрого преобразования фурье

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

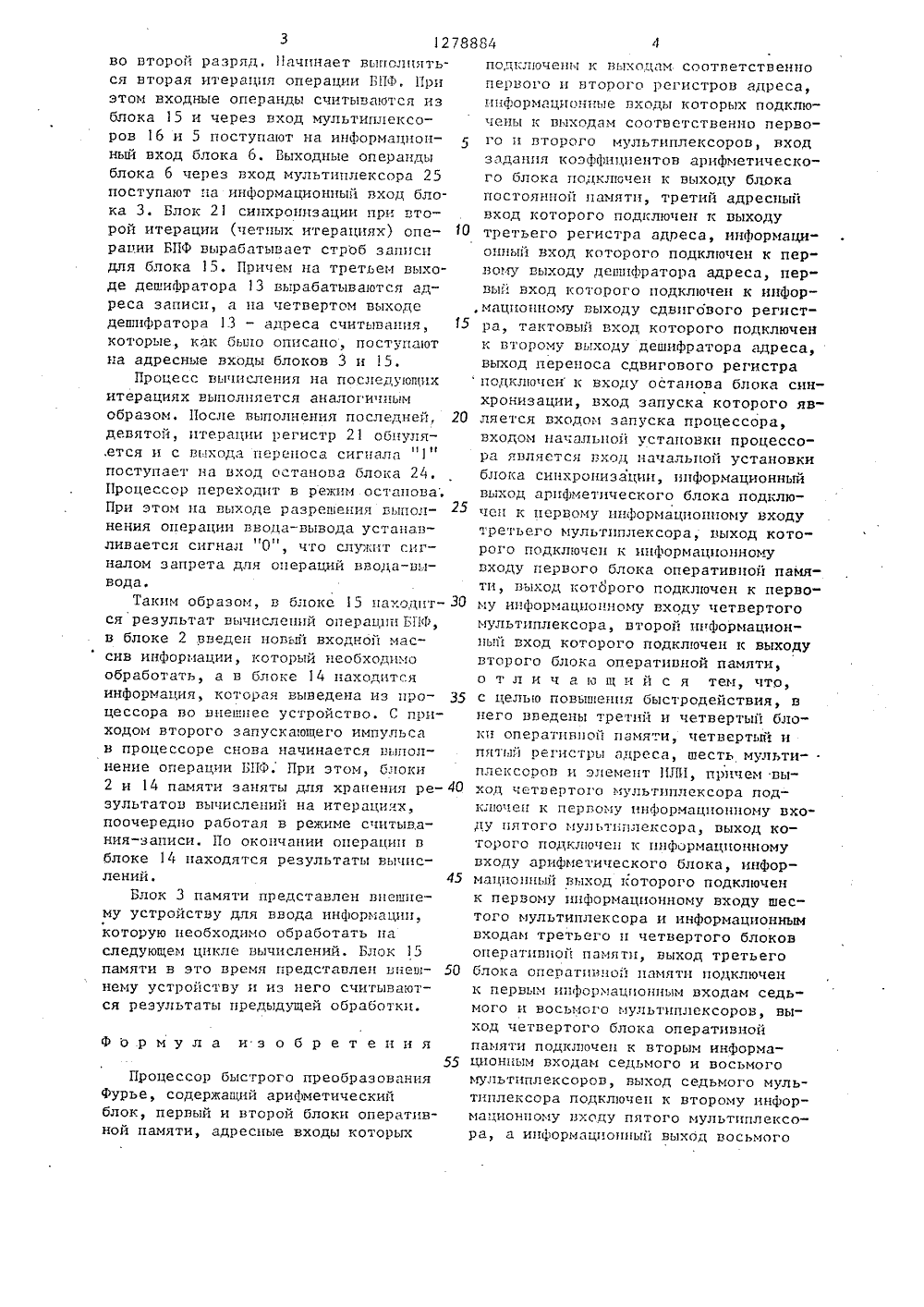

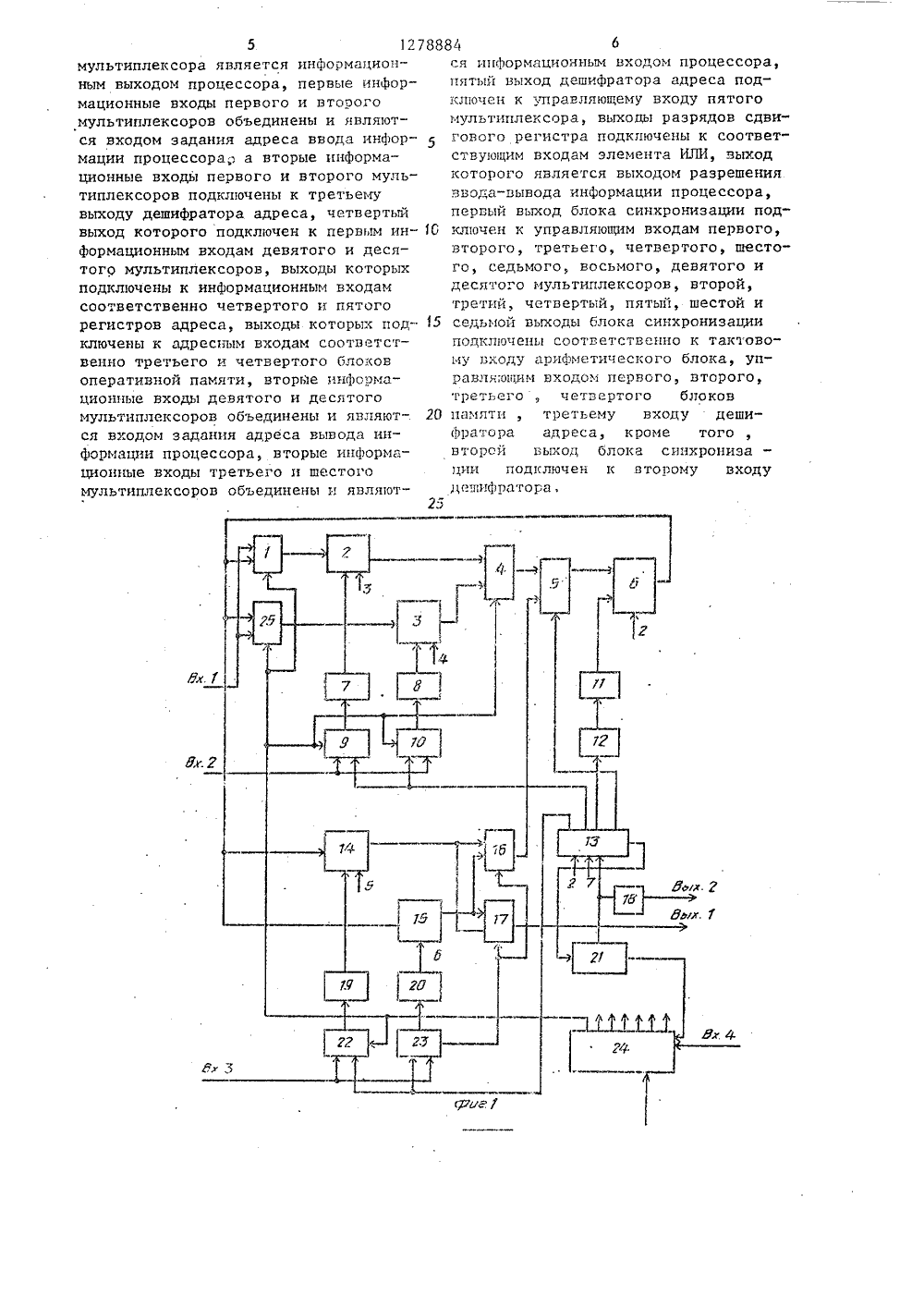

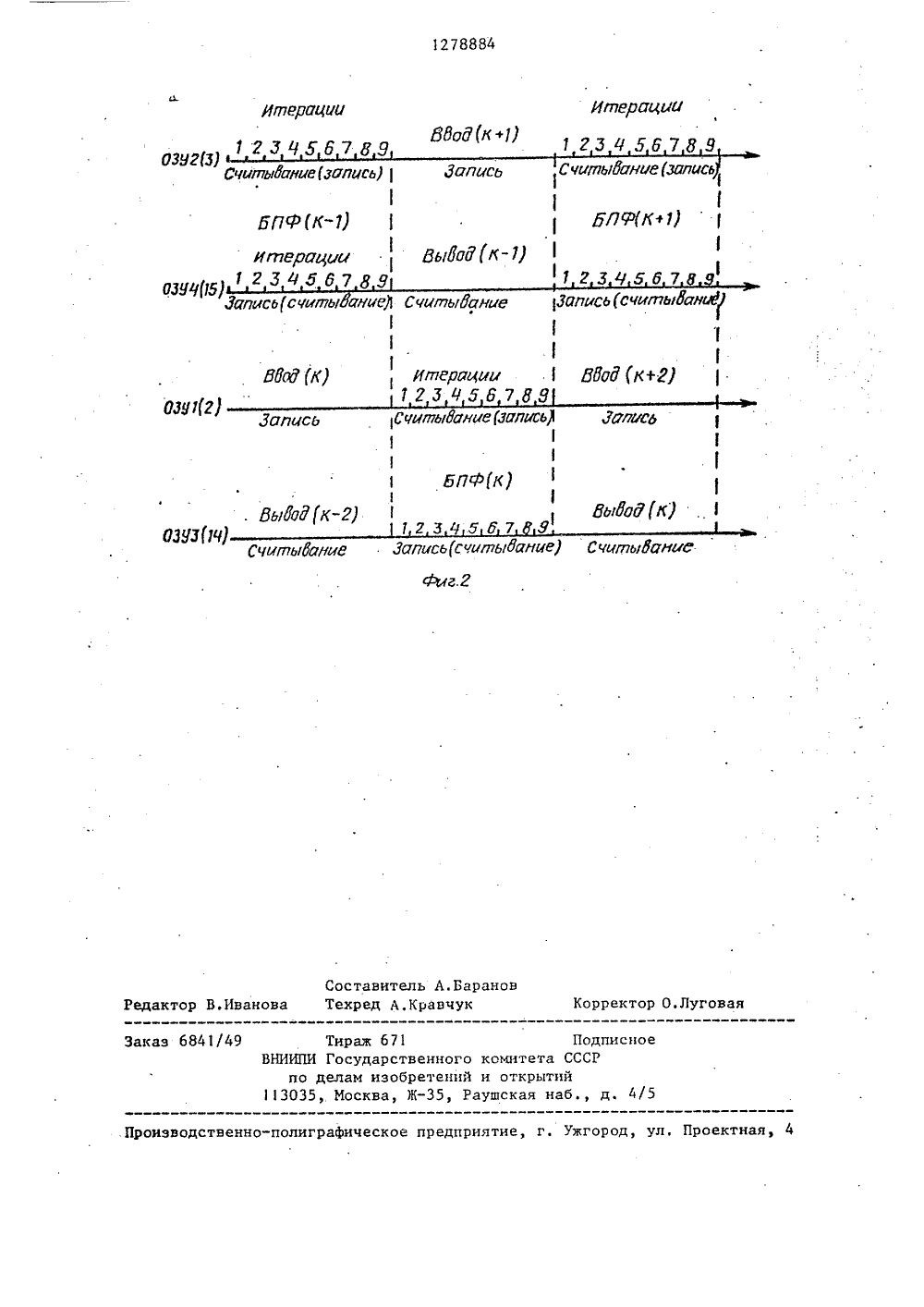

/33 1)4 С 06Г (ъ. 01 ВТСРСИОМ ешени зова кого о анализа, где н ь обработку с и масш повь с СССР 198. ССР1982. БРАЗОВА,ти,типл дешиФ говый от к вычислить исполь про СО 103 СОВЕТСНИХСО 1.1 ИАЛИСТИЧЕСНИХРЕСПУБЛИН ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ ИДЕТЕЛЬСТВ У(54) ПРОЦЕССОР БЫСТРОГО ПРЕЮНИЯ ФУРЬЕ(57) Изобретение относитсятельной технике и может бы задач гармоничесеобходимо произгналов в реальном . ель изобретения - ствия процессора. остигается тем, ыре блока опера- постоянной памя" блок, десять мульегистров адреса, элемент ИЛИ, сдвисинхронизации и зи между узлами табе времени, Ц ппение быстродей авленная цель д и содержит чет ой памяти, блок ариФметический ексоров, пять р ратор адреса, регистр, блок етствующие свя ссора. 2 ил.Изобретение отоси.ся к нычислцтельнай технике и мажет быть цспопьзоиацо прц решении задач гармонического ааИэза где необходимо производить отработку сигнала н реальноммас 1 Табе времениЦелью изобретения является повьшеение Сыстродействця процессора.На фиг прецставлепа функциональная схема процессора; иа Фиг,2 - временная дцаграмеа рабаты процессора,для Ы =- 512 точек,Процессор БПФ садерлт мультиплексор 1, блоки 2 и 3 оперативной памяти, гтултстиплексары 4 и 5, арифетичес Гий блок 6, ре.истр. 7 и Л адресаГмультцйлексоры 9 и 1 О, блок 11 поста 5 ппеа 1 11 а 5 сц с ретист) 1 2,адресабттак 13 дешис 1)ратора адреса, б.таки 14апГ 1 рат пнцсэ) 11 аг 15 т 1у Геь 1 иплек 20сары 16 1 1/ эттеаЕю 1 УП 1 18, регистрс9 и 20 адреса(итерацианнсш) сднцговыс рег Отэ 2мультттпле 1 осары 2 и 3, Спок 24 сЕИЕхронизацсц и 1 удвтцПЛЕЕГСО) 25.Рассмотрим рабату процессора наПнцшнро Обт)абатхц Массива тсЕЕГНай5 2 1 ОтСЕ,Й сСХОЦЕЕОМ СОСТОЯНИИ ВСЕ РЕГИСТРЫ.Обнуэте 1 ы, на первом выходе блока 2430устанавливается уровень "1", приэтом в мультцтпексарах 1;,9,10,16,17522 23 и 25 будут открыл ы дпя праха)кден 151 информацИЕ первые вхадь 1, Нап 5 там выходе,7 Ессецс)т)атаэа 13 уста 10ссвитая уровеньи при этом в мультиплексоре 5 будет открыт первыйвход, Ца выходе разрешения операцийввода-вывода установится уровень 040чта является сЕгалоы запрета вьпэалнения этцх операций для внешних уст 1)ойств.С приходам залускающега импульсана нхад.запусс:а блока 24, блок 2445синхронизации начинает вырабатыватьТИКГГ)с)НЕ СИГИ" св,ЛЯ НСЕХ Устт)О)сств,Прц этом н первый разряд регистра 21сдви 1 а уст анат)5 ив нет ся 1 и па нсехаде разрсшеЕия льеталиеЕгтя аперацицвнода-вывода устанавливается сцг 1 ал50с)с ссчта ря 31)ешает ннсш 1 м устрайстНЬ)М ВЫПОЛ 1 ЕНИЕ ОПЕ)Гсдпй )Лада-ВЫНОДаИасгя 1 н чцсеп, ка 1 орый неабхад:,ма Обрабататтс, поступает на вход працсссора и далее черсз вход мультиплексора551 - на вход блока. 2. 1 а адресный вход;блока 2 чер"з вход му)ыиппексара 9и рсгистр 7 поступают адреса, катарые вырабатывает внешнее устройствосинхронно с входной информацией иподает на первый адресный вход процессора. Одновременно с вводом инФормации в процессоре выполняетсяоперация обработки информации (операция БПФ), При этом дешифратор 13 вы"рабатынает на третьем выходе адресаоперандов, по которым производитсясчитынание информации из блока 3.Через вход мультиплексора 10 адресапоступают на регистр 8 и далее - наадресный вход блока 3. Информация свыхода блока 3 через входы мультиплексоров 4 и 5 поступает на инфоргеационный вход блока 6. На первомвыходе дешифратора 13 Формируютсяадреса весовых коэффициентов, которые записывая)тся в регистр 12,С выхода блокасчитываются весовые коэффициенты, которые синхронно с. входными операндами поступаютна вход задания коэффициентов блока6. В блоке 6 выпалеяются базовые операции алгоритман БПГ 1). Результаты высцСПЕНИй С ВЫХада бЛОКа 6 ПОСтуПаЮтна нхады блоков 14 и 15, При выполнении первой итерации БПФ (1 ечетныхитерациях) блок синхронизации вырабатывает строб записи для блока 15.Па четвертом выходе дешифратора13 вырабатываются адреса, по которымпроизводится запись результатов базовой операции в блок 15. Опи поступают на адресный вход блока 15 черезнход мультиплексора 22 и регистр 30.Одновременно с операциями ввода информации и обработки в процессоре выполняется операция вывода информации,которая была абраСотана на предьедуцег цикле вычислений. При этом внешнее устройство выставляет на второйадресный вход процессора адреса, покоторым необходимо считать инфармаЕеео. Через вход мультиплексора 22адреса поступают на регистр 19 и далее па адресный вход блока 14, Изблока 14 считывается информация, которая через вход мультиплексора 17поступает ца инфорыациангьт 51 выходпроцессора и далее во внешнее устройство. После выполнения первой итерации на выходе дешифратара 13 устанав.пинается уровень0и при этом вмультипгексаре 5 открывается второйнхад. На втором выходе дешифратора13 формируется сигнал, по которомупроисходит сдвиг "1" в регистре 215 10 15 25 30 35 40 50 во второй разряд, 1 ачинает выполняться нтарая итерация операции БПФ. Приэтом входные операнды считываютсл изблока 15 и через вход мультиплексоров 16 и 5 поступают на информациопный вход блока 6. Выходные операндыблока 6 через вход мультиплексора 25поступают па информационный вход блока 3. Блок 21 синхронизации при второй итерации (четных итерациях) операции БПФ нырабатывает строб записидля блока 15. Причем на третьем выходе дешифратора 3 вырабатываются адреса записи, а на четвертом выходедешифратора 13 - адреса считывания,которые, как аыло описана, поступаютна адресные входы блоков 3 и 15.Процесс вычисления на последующихитерациях ныполняется аналогичнымобразом, После выполнения последней,денятай, итерации регистр 21 обнуля,ется и с выхода переноса сигнала "1поступает на вход астанана блока 24.Процессор переходит в режим астанава.При этом на выходе разрешения выполнения операции ввода-вывода устанавливается сигнал0 , чта служит сигналом запрета для операций ввода-вывода,Таким образом, в блоке 15 находится результат вычислений операцпп БП 1,в блоке 2 введен новый входной массив информации, который необходимообработать, а в блоке 14 находитсяинформация, катарал выведена из процессора на внешнее устройство. С приходом второго запускающего импульсав процессоре сиона начинается выполнение операции БПФ. При этом, блоки2 и 14 памяти заняты для хранения результатон вычислений на итерациях,поочередно работая в режиме считывания-записи, По окончании аперацип вблоке 14 находятся результаты вычислений,Блок 3 памяти представлен внешнему устройству для ввода информации,которую необходима обработать наследующем цикле вычислений. Блок 15памяти в это нремл представлен ьнешнему устройству и из него считываются результаты предыдущей обработки,Формула и з обретения Процессор быстрого преобразования Фурье, содержащий арифметический блок, перный и второй блоки оперативной памяти, адресные входы которых падкпочены к выхацам соответственнопервого и второго регистров адреса,информационные входы которых подключены к ныхадам соответственно первого и второго мультттексорон, входзадания коэффициентов арифметического блока подключен к выходу блокапасталнпой памяти, третий адресныйвход которого подключен к выходутретьего регистра адреса, информационный вход которого подключен к первому выходу дешифратора адреса, первый вход которого подключен к ипфор,мационному гыходу сднигового регистра, тактовый вход которого подключенк второму выходу дешифратора адреса,выход перепаса сдвигового регистра подключенк входу остапова блока синхронизации, вход запуска которого явллется входам запуска процессора,входом начальной установки процессора лнллетсл вход начальной установкиблока синхронизации, инФормационныйвыход арифметического блока подключен к первому информационпому входутретьего мультиплексора, выход которого подключен к информационномувходу первого блока оперативнои памяти, выход которого подключен к первому информационному входу четвертогомультиплексора, второй информационный вход которого подключен к выходувторого блока оперативной памяти,о т л и ч а ю щ и й с я тем, что,с целью повышения быстродействия, ннего введены третий и четвертый блоки оперативной памяти, четнертыи иплтый регистры адреса, шесть мультиплексоров и элемент ИЛИ, причем ныхад четвертага мультиплексора подключен к первому инфармацпанному нходу плтага мультиплексора, выход которого подкюпочел к информационномувходу арифметического блока, информацнонныи выход которого подключен к первому ипфармацианному входу шестого мультиплексора и информационнымвходам третьего и четвертого блоковоперативной памлти, выход третьегоблока оперативной памяти подключенк первым информационным входам седьмого и восьмого мультиплексоров, выход четвертого блока оперативнойпамлти подключен к вторым информацианпым входам седьмого и восьмого мультиплексоров, выход седьмого мультиплексора подключен к второму информационному входу плтого мультиплексора, а информационный выход восьмого5 127 мультиплексора является информационным выходом процессора, первые информационные входы первого и второго мультиплексоров объединены и являются входом задания адреса ввода информации процессора а вторые информационные входы первого и второго мультиплексоров подключены к третьему выходу дешифратора адреса, четвертый выход которого подключен к первым информационным входам девятого и десятого мультиплексоров, выходы которых подключены к информационным входам соответственно четвертого и пятого регистров адреса, выходы которых подключены к адресным входам соответственно третьего и четвертого блоков оперативной памяти, вторь 1 е информационные входы девятого и десятого мультиплексоров объединены и являются входом задания адреса вывода инФормации процессора, вторые информационные входы третьего и шестого мультиплексоров объединены и являют 8884 бся информационным входом процессора,пятый выход дешифратора адреса подключен к управляющему входу пятогомультиплексора, выходы разрядов сдви 5 гового регистра подключены к соответствующим входам элемента ИЛИ, выходкоторого является выходом разрешенияввода-вывода информации процессора,первый выход блока синхронизации подЮ ключен к управляющим входам первого,второго, третьего, четвертого, шестого, седьмого, восьмого, девятого идесятого мультиплексоров, второй,третий четвертый, пятый, шестой и15 седьмой выходы блока синхронизацииподключены соответственно к тактово"му входу арифметического блока, управляющим входом первого, второго,третьего , четвертого блоков20 иамлти , третьему входу дешиФратора адреса, кроме тоговторой выход блока синхрониэации подключен к второму входудешифратора,251278884 Итерацьа Ищерацци фдад к+1)ОЗУ 2 Щ1 г 1 В 7 г 9 8 ф 1 1 гд Ю В 7 г 9Счищы 5 ание 1 Запись)Запись СчижЫ 5 анцЕ(ЗаписьБ/7 Ф К)БПМК+ 1ИгиеРаЦии ВыЫ 1 К). ЮыЫ(к) ЕыРоУ К) .ОЗУ 309)1 2 3 с/ 5 б 7 ЯСчищы 5 ание Запись(счипыдание) Считыбание ЮЫ к) Составитель АьБаранов Техред А,Кравчук Редактор В.Иванова Корректор ОьЛуговая Тираж 671 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д, 4/5

СмотретьЗаявка

3874334, 23.12.1984

ПРЕДПРИЯТИЕ ПЯ В-2962

ШАНЬГИН ВЛАДИМИР АЛЕКСЕЕВИЧ, ПЕРЬКОВ ПАВЕЛ ПАВЛОВИЧ, МЕЛЬНИК ВЛАДИМИР ЕГОРОВИЧ

МПК / Метки

МПК: G06F 17/14

Метки: быстрого, преобразования, процессор, фурье

Опубликовано: 23.12.1986

Код ссылки

<a href="https://patents.su/5-1278884-processor-bystrogo-preobrazovaniya-fure.html" target="_blank" rel="follow" title="База патентов СССР">Процессор быстрого преобразования фурье</a>

Предыдущий патент: Устройство для формирования адресов процессора усеченного быстрого преобразования фурье

Следующий патент: Псевдостохастический анализатор спектра

Случайный патент: Система запуска двигателя внутреннего сгорания