Преобразователь двоично-десятичных чисел в двоичные

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1262733

Авторы: Золотовский, Коробков

Текст

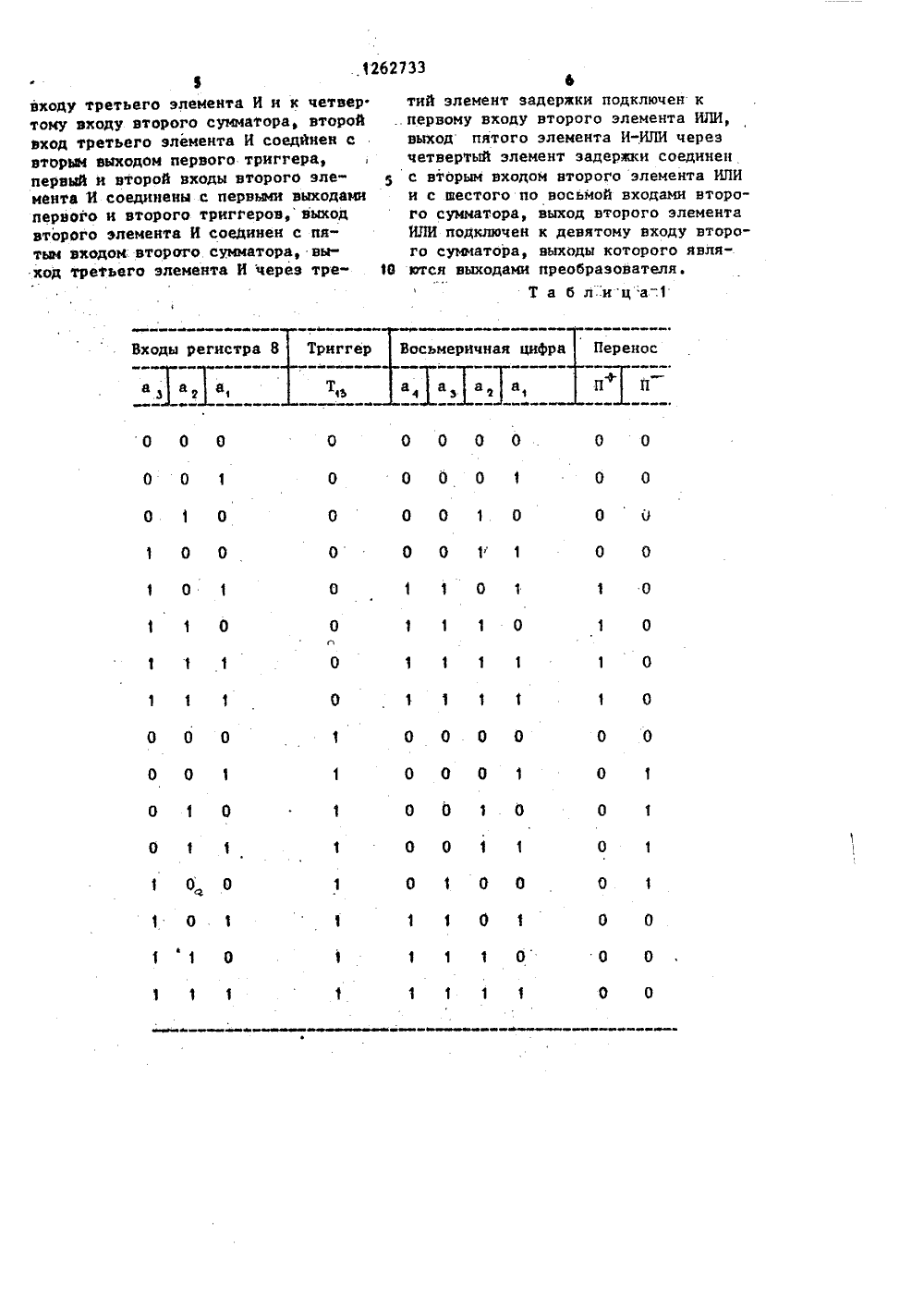

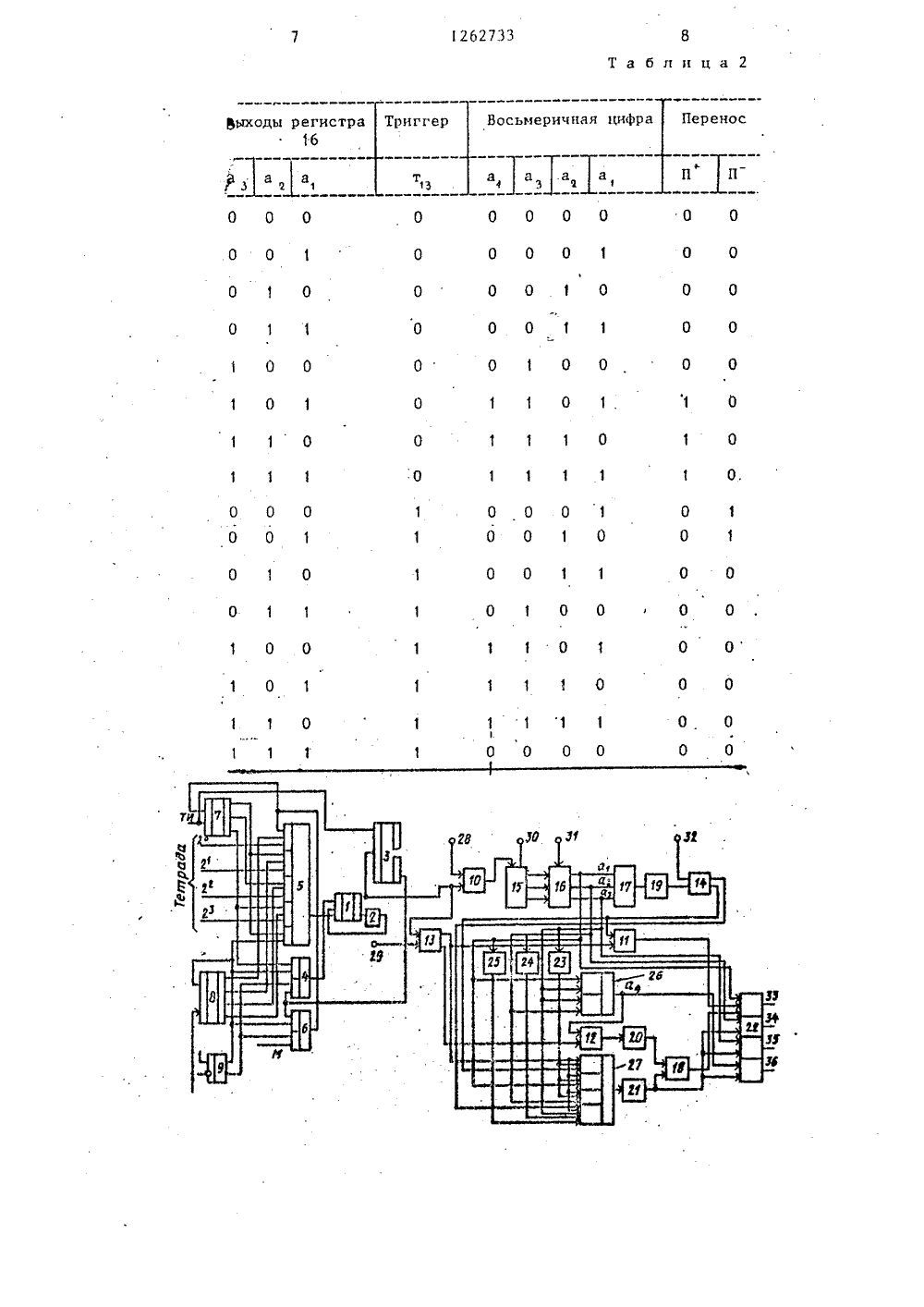

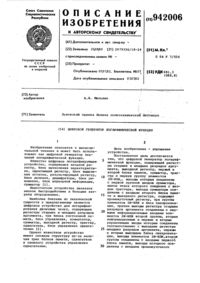

(51)4 Н 03 и 1/12 ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ 369"9 м еОПВОЛНИК ИЗОВ ЕтенияН АВТОРСКОМУ ИЗИДЕТЕЛЬСТВУ(71) Таганрогский радиотехнический институт им, В.Д.Калмыкова (72) В.Е,Золотовский и Р.В,Коробков(53) 681,325(088.8)(56) Авторское свидетельство СССР М 742924, кл. С 06 Р 5/02, 1978.(57) Изобретение относится к области вычислительной техники и может быть использовано в специализированныхи универсальных вычислительных устройствах, Цель изобретения - расширение класса решаемых задач эа счетнозможности преобразования в восьмеричный избыточный код, Укаэаннаяцель достигается за счет дополнительного введения в преобразовательсумматора, двух регистров, двухтриггеров, трех элементов задержки,двух элементов И-ИЛИ, двух элементовИЛИ, трех элементов И и трех элемен"тон НЕ. Изобретение янляется дополнительным к ант. св. В 742924, 1 ил,Изобретение относится к вычислительной технике, может быть использо-вано в специализированных и универсальных вычислительных устройствахи является усовершенствованием устройства цо авт. св. 9 742924.Цель изобретения - расширениекласса решаемых задач за счет воэможности преобразования в восьмеричный избыточный кОдеНа чертеже представлена схемапредлагаемого преобразователя,Схема содержит первый сумматор 1,элемент 2 задержки, сдвиговый регистр 3, элементы И-ИЛИ 4-6, трехраэрядный регистр 7 сдвига, четырехраэрядный регистр 8, сдвига, одцовибратор 9, элементы И 10-12, триггеры13 и 14, регистры 15 и 16, элементыИЛИ 17 и 18, элементы 19"21 задержки, второй сумматор 22, элементыН. 23-25, элементы И-КШ 26 и 27,входы 28-32, выходы 33-36 преобразователя.Выход суммы сумматора 1 преобразователя двоично-десятичных чиселв двоичные соединен с входом элемента И 10 и 0"входом триггера 13. Второй вход элемента И и С-вход триггера 13 соединены с входами 28 и 29устройства соответственно, ВыходЭлемента И 10 соединен с информационНым входом трехразрядного регистра15. Вход управления сдвигом в регист.ре 15 соединен с входом 30 устройства, Выходы разрядов регистра 15соединяются с входами трехраэряднагорегистра 16. Вход управления записью регистра 16 соединен с входом31 устройства. Выходы разрядов регистра 16 через элемент ИЛИ 17 иэлемент 19 задержки соединены с8-входом КБ-триггера 14. Е-входтриггера 14 соединен с входом 32устройства.Первый (младший), второй и третийразряды регистра 16 соединены свходами первого, второго и третьегоразрядов четырехраэрядцого сумматора 22 и входами элементов НЕ 23-25.С выходов регистра 16 считываютсятри младших разряда(а , а и а )1неоткорректированной восьмеричйой 5 цифры. Четвертый старший разряд ееа формируется в элементе И-ИЛИ 26по алгоритму; а 4 а а Чаэ 3 а,.С выхода элемента И-ЙЛИ 26 апоступает ца вход четвертого раз ряда сумматора 22. Конъюнкция единичных выходов триггеров 13 и 14,сформированнаяэлементом И 11, поступает на второй вход младшего разряда сумматора 22. В элементе И 15 12 и элементе И-ИЛИ 27 формируютсясоответственно положительцыц перенос+П = Т а20,П = Т,Т,Р а ча фа,йТЧТ,а а Чгде Т,Тц, Т,и Т - единичныйи инверсныйвыходы триг геров 13и 14.Сформированные переносы задерживаются в элементах 20 и 21 задержкина три такта (на один восьмеричный 30 разряд) и через элемент ИЛИ 18 посту"лают на третий вход младшего разрядасумматора 22, Отрицательный переносиэ элемента 21 задержки поступаетна вторые входы второго, третьегои четвертого разрядов сумматора 22.Выходы разрядов 22 являются выходами33-36 устройства.Устройство работает следующимобразом.40 В преобразователе Формируетсядополнительный двоичный код масштабированнай величины младшими разрядами вперед. С помощью дополнительных элементов он преобразуется визбыточный восьмеричный код, В последнем используется основцое ивспомогательное кодирование. В.основном коде восьмеричные цифрыпредставляются следующим образом:1262 33 10 15 В преобразователь двоично-десятичные цифры поступают последовательно. После поступления каждой цифры ца вход 29 в такте, отведенном для передачи знака, подается сигнал записи, поступающий ца П-вход триггера 13, поэтому в триггер запишется знак преобразуемого числа еще до завершения преобразования. После завершения преобразования на вход 28 поступает сигнал разрешения выдачи восьмеричного кода длительностью в один цикл, По этому сигналу эле-. мент И 10 открывается це меняясь. 1( моменту прихода триады, следущей эа первой, отличной от нуля,триггер 14 переходит в единичноесостояние. Алгоритм Формированиявосьмеричной цифры неменяется. Очередная восьмеричная цифра складывается с переносом П или 11 в сумматоре 22. Если преобразуемое числоее имеет знак "-", сумма цифры ипереноса увеличивается ца единицу 25младшего разряда, формируемую элементом И 11, В результате Формирование восьмеричной,цифры на выходах3. 36 (Б , Б , Б , Б ) и двоичныикод числа поступает на вход регистра 3015, на вход управления сдвигом кото"рого поступает непрерывная тактоваясерия,В первом, второи и третьем тактахцикла в регистр 15 запишутся тримладших разряда двоичного числа,которые затем по сигналу зиписи,поступающему на вход 31, перепишутся в регистр 16. В дальнейшем в регистр 16 записывается 4-6 разрядыдвоичного числа, которые опять перепишутся в регистр 16, и так далее.В результате на выходах регистра 16Формируется последовательно-парал.лельный код, в котором триады передаются последовательно друг за другом, а разряды каждой триады " парал"лельно. Время передачи одной, триадысоставляет три такта. Если младшиетриады числа нулевые, триггер 12;,по входу 32) остается в нуле, а ,щФю,П =П =О,С выходов сумматоров считываетсявосьмеричный воль 0000. Пусть в регистр 16 поступила первая триада,отличная от нуля. Благодаря трехтактному элементу 19 задержки триггер 14 перейдет в единичное состояниелишь к приходу следующей триады,На выходах регистра 6 и элемента И-ИЛИ 26 будет формироваться восьмеричная цифра, ца выходах элементов И 2 и И-ИЛИ 27 - переносы в соответствии с табл, 1.При поступлении на входы сумматора 22 первой восьмеричной цифры, отличной от нуля, переносы 11 " Пна входах сумматора 22 отсутствуют и цифра проходит на входы устройства происходит в соответствии с табл. 2. формула изобретения Преобразователь двоично-десятичных чисел в двоичные по авт, св, Ф 742924, о т л и ч а ю щ и й с я тем, что, с целью расширения класса решаемых задач за счет воэможности преобразования в восьмеричный избыточный код, в него введены сумматор, два регистра, два триггера, три элемента задержки, два элемента И-ИЛИ, два элемента ИЛИ, три элемента И, три элемента НЕ, причем выход суимы первого сумматора соединен с первыми входами первого триггера и первого элемента И, вторые входы которых соединены соответственно с ицфориационныи входом и входом разрешеция выдачи восьмеричного кода преобразователя, выход первого элемента И подключен к информационному входу первого регистра, вход управления сдвигом которого соединен с тактовым входои преобразователя, выходы разрядов первого регистра соединены с соответствующими информационными входами второго регистра, выходы которого через первый элемент ИЛИ подключены к входу второго элемента задержки, выходом соединенного с первым входом второго триггера, второй вход которого подключен к установочному входу преобразователя, выходы второго регистра соединены с первым, вторым и третьим входами второго сумматора, входами первого, второго и третьего элеиентов НЕ, с соответствующими входами четвертого и пятого элементовИ-ИЛИ, выходы первого, второго и третьего элементов НЕ подключены к входам пятого элемента И-ИЛИ, выход четвертого элемента. И"ИЛИ поДключен к первому1262733тий элемент задержки подключен к . первому входу второго элемента ИЛИ,выход пятого элемента И-ИЛИ черезчетвертый элемент задержки соединенс вторым входом второго элемента ИПИи с шестого по восьмой входами второго сумматора, выход второго элементаИЛИ подключен к девятому входу второго сумматора, выходы которого явля ются выходами преобразователя.Т а б л.иц а-.1 Входы регистра 8 Триггер Восьмеричная цифра Перенос а аз а а, П Й О О 0 О О О О 1 0 О О О О 0 О 0 0 0 О 1 О 0 О0 О н О 1 1 1 О О О 0 ОО 1 О О 1 1 О О 1 О1 О фвходу третьего элемента И и к четвер.тому входу второго сумматора, второйвход третьего элемента И соедйнен свторым выходом первого триггера,первый и второй входы второго элемента И соединены с первыми выходамипервого и второго триггеров, выходвторого элемента И соединен с пятым входом второго сумматора, выход третьего элемента И через тре 0 0 0 О О 1 О 1 О 1 О О 1 0 1 1 О1 0 0 1" 11 О1 1 О1 1 1 1О 0 0 ОО О 00 0 1 О0 О 1 1О 1 О 01 1 О 11 1 О1 1 1 1 1 О 1 0 1 О 0 О О 1 0 1 0 1 О 1 О О О О О О1 1 0 1 1 1 5 ьподы регистра16 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 Та блица 2 Триггер Восьмеричная цифра 0 1 О 00 0

СмотретьЗаявка

3801461, 09.10.1984

ТАГАНРОГСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. Д. КАЛМЫКОВА

ЗОЛОТОВСКИЙ ВИКТОР ЕВДОКИМОВИЧ, КОРОБКОВ РОАЛЬД ВАЛЕНТИНОВИЧ

МПК / Метки

МПК: H03M 7/12

Метки: двоично-десятичных, двоичные, чисел

Опубликовано: 07.10.1986

Код ссылки

<a href="https://patents.su/5-1262733-preobrazovatel-dvoichno-desyatichnykh-chisel-v-dvoichnye.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь двоично-десятичных чисел в двоичные</a>

Предыдущий патент: Преобразователь последовательного кода в параллельный

Следующий патент: Автоматический приемник сигналов тревоги

Случайный патент: Однотактное цифровое арифметическое устройство