Цифровой генератор логарифмической функции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 942006

Автор: Мельник

Текст

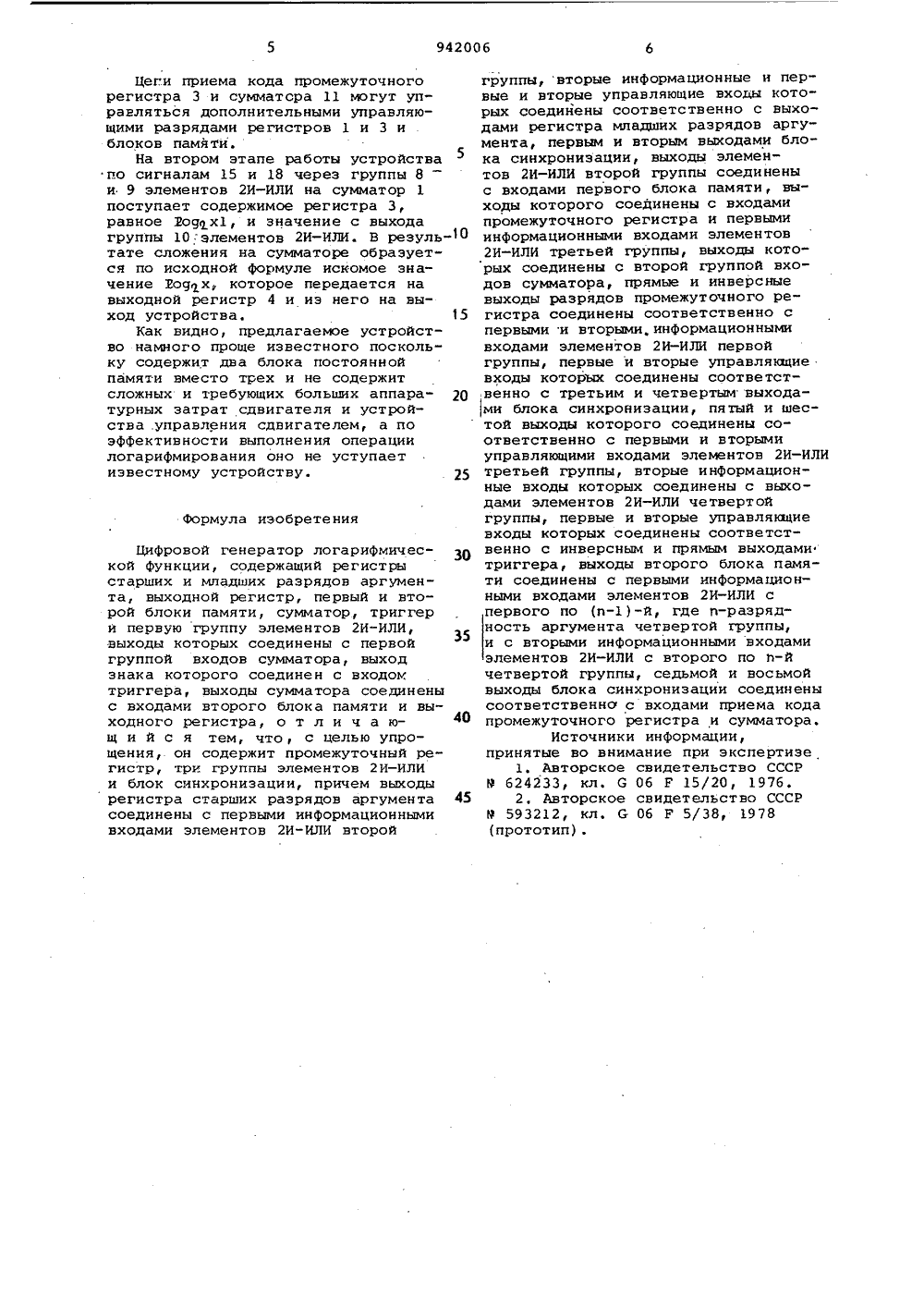

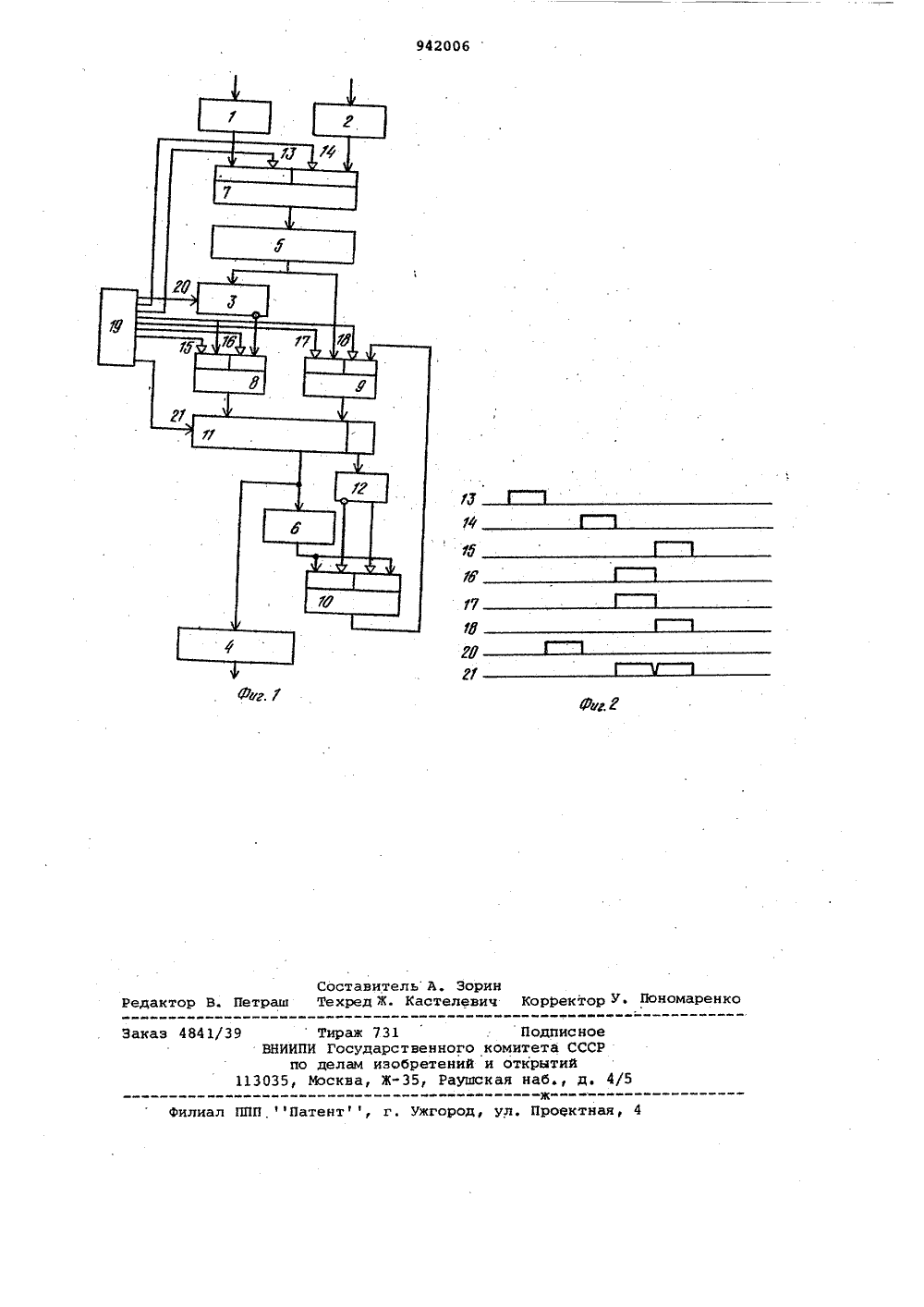

ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциалистическихРеспублик. 942006(23) Приоритет Государственный комитет СССР но делам изобретений и открытий(088. 8) Дата опубликования описания 070782(72) Авторизобретения А.А. Мельник Львовский ордена Ленина политехнический ййститут,(71) Заявитель(54) ЦИФРОВОЙ ГЕНЕРАТОР ЛОГАРИФМИЧЕСКОЙ ФУНКЦИИ Изобретение относится к вычислительной технике и может быть использовано как цифровой генератор значений логарифмической функции.Известно цифровое логарифмирующееустройстно, содержащее входной регистр, блок вычисления характеристики, сдвигающий регистр, блок выделения остатка, результирующий регистр,блок деления, дешифраторы, блок умножения, блок априорной информации,сумматор (1),Недостатком устройства являетсянизкое быстродействие и большие затраты оборудования.. Наиболее близким по техническойсущности к предлагаемому являетсяцифровое устройство для логарифми- .рования двоичных чисел, содержащеерегистры старших и младших разрядоваргумента, три блока постоянной памяти, блок управления, ксммутатор,сумматор, выходной регистр, триггер,сдвигатель, блок управления сднигателем (2),Однако известное устройствоимеет сложную структуру из-за наличия трех блоков памяти, сдвигателяи сложного устройстна управлениясдвигателем,Цель изобретения - упрощение . устройства.Поставленная цель достигаетсятем, что цифровой генератор логарифмической функции, содержащий регистры старших и младших разрядов аргумента, выходной регистр, первый и второй блоки памяти, сумматор, триггер и первую группу элементов2 И-ИЛИ выходы которых соединены с первой группой входов сумматора, выход знака которого соединен с входом триггера, выходы сумматорасоединены с входами второго блока памяти и выходного регистра, содержит промежуточный регистр, три группы элементов 2 И-ИЛИ и блок синхронизации, причем выходы регистра старших разрядов аргумента соединены с первыми информационными входами элементов 2 И-ИЛИ нторой группы, вторые информационные и первые и вторые управляющие входы которых соединены соответственно с выходами регистра 25 младшихразрядов аргумента, первьии вторым выходами блока синхронизации, выхОды элементов 2 И-ИЛИ,второй группы соединены с входами первого блока памяти, выходы которого сое динены с входами промежуточногорегистра и первыми информационными входами элементов 2 И-ИЛИ третьей группы, выходы которых соединены с второй группой входов сумматора, прямые и инверсные выходы разрядов промежуточного регистра соединены соответственно с первыми и вторыми информационными входами элементов 2 И-ИЛИ первой группы, первые и вторые управляющие входы которых соединены соответственно с третьим и четвертым выходами блока синхрониза;ции, пятый и шестой выходы которого соединены соответственно с первыми и вторыми управляющими входами элементов 2 И-ИЛИ третьей группы, вторые информационные входы которых соединены С выходами элементов 2 И-ИЛИ четвертой группы, первые и вторые управляющие входы которых соединены соответственно с инверсным и пряьым выходами триггера, выходы второго блока памяти соединены с первыми информационными входами элементов 2 И-ИЛИ с первого по (п)-й, где и - разрядность аргумента четвертой группы, и с вторыми информационными входами элементов 2 И-ИЛИ с второго по и-й четвертой группы, седьмой и восьмой выходы блока синхронизации соединены соответственно с входами приема кода промежуточного регистра и сумматора.На Фиг.1 представлена блок-схема генератора; на фиг.2 - вариант временной диаграммы работы блока синхронизации. цифровой генератор логарифмирующей функции содержит регистры 1 и 2старших и младших разрядов аргумента, регистр 3 промежуточный, выходной регистр 4, блоки 5 и 6 памяти, группы 7"10 элементов 2 И-ИЛИ, сумматор 11 и триггер 12, управляющие входы 13-18 групп элементов 2 И-ИЛИ, блок 19 синхронизации, входы 20 и 21 приема кода промежуточного регистра и сумматора.Блок 19 синхронизации может быть реализован с помощью генератора импульсов и элементов задержки (фиг, 2)Устройство производит вычисление двоичного логарифма от нормализованного аргумента х(сх ( 1) на основе соотношенийХодк = Ходзь(х 1 + х 2)= йод,1 х 1 + Ход(1 + - )хйхй.хЮХод --- = Уод 1 х 2- Ходх 1, где Х 1 - число, образованное и/2старшими разрядами аргумента;х 2 - число, образованное п/2младшими разрядами аргумента;п - число разрядов аргумента. Устройство работает следующим об-разом.На первом этапе работы устройства значение х 1 из регистра 1 старшихразрядов аргумента поступает черезгруппу 7 элементов 2 И-ИЛИ по сигналу, поступающему по управляющему входу 13 на блок 5 памяти, в которомхранится таблица логарифмов числах 1. Число же х 2 приводится к диапа 10 зону изменения х 1 и тем самым длявычисления его логарифма используется та же таблица, Это вытекает изследующего соотношения:152 од 1 х 2 = 2 од 1 х 2 2=8 о)Х"2 +Ход 2 = 2 одх 2,где х 2 = х 22,Из блока 5 снимается значениеХодх 1 и поступает на промежуточныйрегистр 3. Значение регистра 2 младших разрядов аргумента поступает наблок 5 памяти через группу 7 элементов 2 И-ИЛИ по сигналу, поступающемупо управляющему входу 14, и из блока5 снимается значение 2 одх 2. Посигналам, поступающим по управляющимвходам 16 и 17, инверсное содержимоерегистра 3(-Зодз 1 х 1) и значение свыходов блока 5, равное ьинтиссе2 од 1 х 2, проходят через группы 8 и 9элементов 2 И-ИЛИ на сумматор 11. Навыходе сумматора 11 формируется,согласно формуле, значение Ход. - ,мантисса которого передается на входблока б памяти, где хранится таблицапромежуточных преобразователей. Этотблок осуществляет табличное преобра-.зование значения мантиссы 2 одз 1 - вх 1Х 1соотнетстнуюнее значение нзЧЗ (Зн 1Ф х 1140Х 1где д - такое целое число, что.и.22 фн -2 + 1.х 1Число д равно значению в " , т.е. рав 45 но сдвигучисла х 2 относительно числах 1, плюс знак сумматора, значениекоторого при сложении мантисс(-Ход 1 х 1) и Родх 2 запоминаетсяна триггере 12 промежуточного результата. Значение с выхода блока бпамяти проходит через группу 10элементов 2 И-ИЛИ или со сдвигом наи/2 разрядов, если содержимое триггера 12 равно нулю, или со сдвигомина 2 + 1 РазРядов, если содержимоетриггера 12 равно единице. Такимобразом, на выходе группы 10 элементов 2 И-ИЛИ иэ значенияФх 260 2 одз) (1 + 2 - ) получаем значениех 1х 2Ход,1(1 + в ), что справедливо ввидуЦеги приема кода промежуточного регистра 3 и сумматора 11 могут управляться дополнительными управляющими разрядами регистров 1 и 3 и блоков памяти.На втором этапе работы устройства по сигналам 15 и 18 через группы 8 и 9 элементов 2 И-ИЛИ на сумматор 1 поступает содержимое регистра 3, равное Родх 1, и значение с выхода группы 10 элементов 2 И-ИЛИ. В результате сложения на сумматоре образуется по исходной формуле искомое значение 2 о 91 х, которое передается на выходной регистр 4 и из него на выход устройства. 15Как видно, предлагаемое устройство намного проще известного поскольку содержит два блока постоянной памяти вместо трех и не содержит сложных и требующих больших аппара турных затрат сдвигателя и устройства .управления сдвигателем, а по эффективности выполнения операции логарифмирования оно не уступает известному устройству. 25Формула изобретенияЦифровой генератор логарифмической функции, содержащий регистры старших и младших разрядов аргумента, выходной регистр, первый и второй блоки памяти, сумматор, триггер и первую группу элементов 2 И-ИЛИ, выходы которых соединены с первой группой входов сумматора, выход знака которого соединен с входом триггера, выходы сумматора соединены с входами второго блока памяти и выходного регистра, о т л и ч а ю 40 щ и й с я тем, что, с целью упрощения, он содержит промежуточный регистр, три группы элементов 2 И-ИЛИ и блок синхронизации, причем выходы регистра старших разрядов аргумента 45 соединены с первыми информационными входами элементов 2 И-ИЛИ второй группы, вторые информационные и первые и вторые управляющие входы которых соединены соответственно с выходами регистра младших разрядов аргумента, первым и вторым выходами блока синхронизации, выходы элементов 2 И-ИЛИ второй группы соединеныс входами первого блока памяти, выходы которого соединены с входамипромежуточного регистра и первымиинформационными входами элементов2 И-ИЛИ третьей группы, выходы которых соединены с второй группой входов сумматора, прямые и инверсныевыходы разрядов промежуточного регистра соединены соответственно спервыми и вторыми. информационнымивходами элементов 2 И-ИЛИ первойгруппы, первые и вторые управлякщиевходы которых соединены соответственно с третьим и четвертым выходами блока синхронизации, пятый и шестой выходы которого соединены соответственно с первыми и вторымиуправляющими входами элементов 2 И-ИЛИтретьей группы, вторые информационные входы которых соединены с выходами элементов 2 И-ИЛИ четвертойгруппы, первые и вторые управляющиевходы которых соединены соответственно с инверсным и прямым выходамитриггера, выходы второго блока памяти соединены с первыми информационными входами элементов 2 И-ИЛИ спервого по (п)-й, где и-разрядность аргумента четвертой группы,и с вторыми информационными входамиэлементов 2 И-ИЛИ с второго по и-йчетвертой группы, седьмой и восьмойвыходы блока синхронизации соединенысоответственно с входами приема кодапромежуточного регистра и сумматора.Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРР 624233, кл. С 06 Р 15/20, 1976.2. Авторское свидетельство СССРР 593212, кл. О 06 Р 5/38, 1978942006 7 оставитель А. Зоринехред Ж. Кастелевич Корректор У. Пономаренк 5 113035 лиал ППП Патент, г, Уж од, ул, Проектная,дактор В. Петрказ 4841/39Тираж 731 ИПИ Государстве по делам изобреМосква, Ж,Подписноеитета СССРткрытий наб., д,ого комний иаушска

СмотретьЗаявка

2979336, 25.08.1980

ЛЬВОВСКИЙ ОРДЕНА ЛЕНИНА ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

МЕЛЬНИК АНАТОЛИЙ АЛЕКСЕЕВИЧ

МПК / Метки

МПК: G06F 7/556

Метки: генератор, логарифмической, функции, цифровой

Опубликовано: 07.07.1982

Код ссылки

<a href="https://patents.su/4-942006-cifrovojj-generator-logarifmicheskojj-funkcii.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой генератор логарифмической функции</a>

Предыдущий патент: Устройство для извлечения квадратного корня

Следующий патент: Устройство для вычисления обратных функций

Случайный патент: Комбинированный движитель транспортного средства