Преобразователь последовательного кода в параллельный

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1262732

Автор: Скорняков

Текст

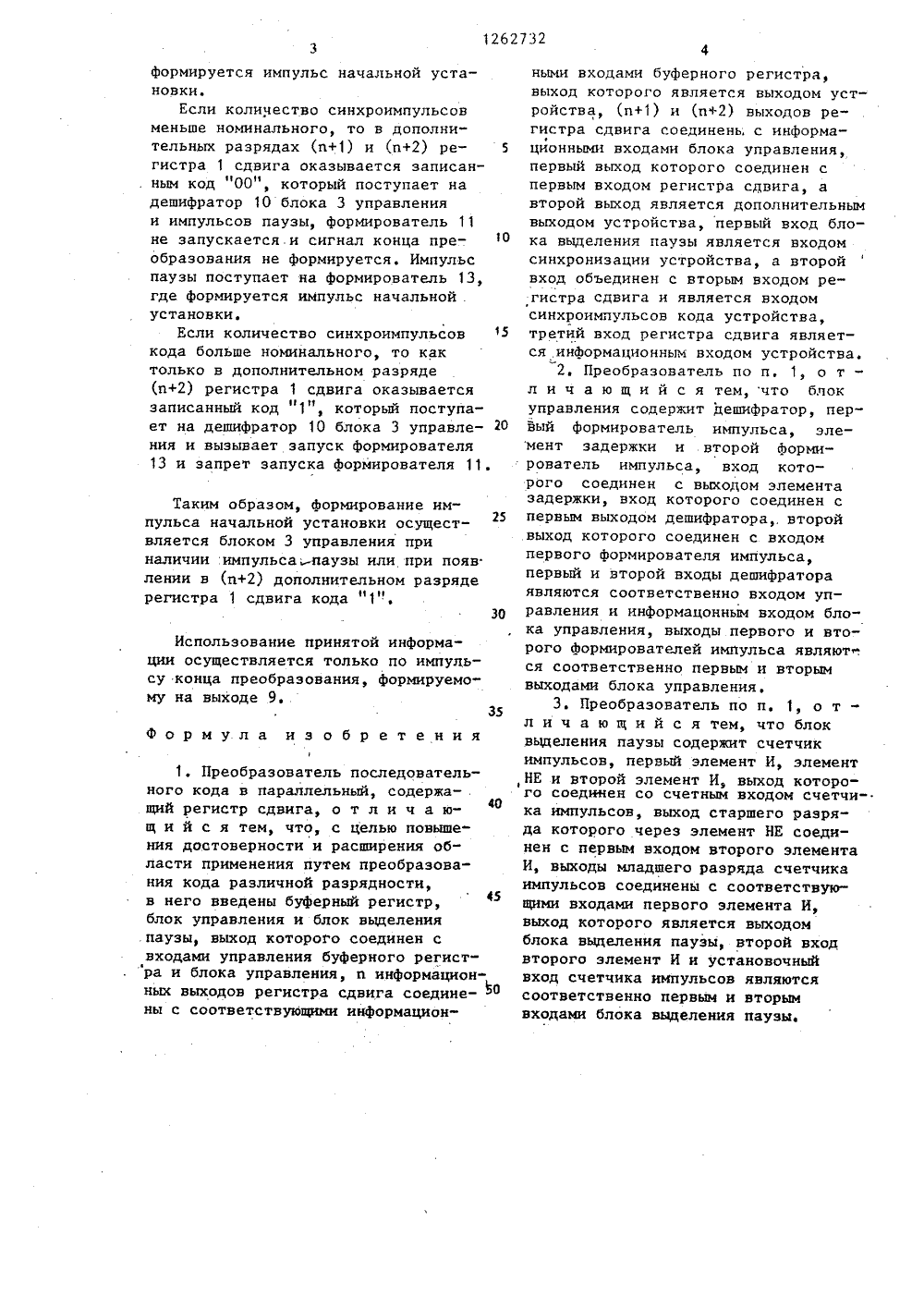

СОЮЗ СОВЕТСНИХСОЦИАЛ ИСТИЧЕСНИХРЕСПУБЛИК 12627 1)4 Н 03 М 7/О ОПИСА(56) Авторское9 851396, кл, САвторское свМ 1081639, кл. юл. Уов8) льство СС /04, 1976 ство СССР 5/04, 198 видет06 Рдетел06 Р 3 В ГОСУДАРСТВЕННЫЙ КОМИТЕТ ССС ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫ Н А ВТОРСНОМУ СВИДЕТЕЛЬСТ(54) ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНЪИ(57) Изобретениеотносится к вычислительной технике, а именно к устройствам преобразования информации,и может быть использовано в системах передачи данных по цифровымканалам. Устройство позволяет нетолько определять сбои в приеме информации по каналу и выявлять словопри приеме которого произошел сбой,но и при переходе с канала на каналпри асинхронной передаче информациивыявлять недостоверные слова и исключать их из дальнейшего использования. Кроме того, устройство обесп чивает работу с разливочной разрядностью последовательного и параллельного кодовВсе перечисленное расширяет функциональные возможности устройства и повышает достоверность обрабатываемой информации. Преобразователь последовательного кода в параллельный содержит регистр сдвига, буферный регистр, блок управле-. ния и блок вьщеления паузы. Первый и второй входы блока выделения паузы являются соответственно входом синхронизации и входом синхроимпульсов кода устройства. Третий вход регистра сдвига является информационным входом устройства. Выход буферного регистра и второй выход блока управления являются соответственно выходом устройства и дополнительным выходом. Блок управления состоит из дешифратора, элемента задержки и двух формирователей импульса. Блок выделения паузы состоит из счетчика импульсов, двух элементов И и элемента НЕ, 2 з.п. ф-лы, 3 ил.Изобретение относится к вычислительной технике и может быть использовано в системах передачи данныхпо цифровым каналам.Целью изобретения является повышение достоверности преобразуемойинформации и расширение областиприменения путем преобразованиякода различной разрядности,На фиг. 1 представлена Функциональная схема устройства; на Фиг, 2функциональная схема блока управле-.ния; на фиг. 3 - функциональнаясхема блока выделения паузы.Преобразователь последовательного кода в параллельный содержитрегистр 1 сдвига, буферный регистр2, блок 3 управления, блок 4 выделения паузы, первый вход которого является входом 5 синхронизации устройства, а второй вход - входом6 синхроимпульсов кода устройства.Выход буферного регистра 2 являетсявыходом 7 устройства, Третий входрегистра 1 сдвига является информационным входом 8 устройства, Второй выход блока 3 управления является. дополнительным выходом 9 устройства,Блок 3 управления содержит дешифратор 10, первый формирователь 11импульса, элемент 12 задержки и второй формирователь 13 импульса.Блок 4 выделения паузы содержитсчетчик 14 импульсов, первый элементИ 15, элемент НЕ 16 и второй элементИ 17,Устройство работает следующим образом.На первый вход блока 4 выделения паузы с входа 5 поступают опорные синхроимпульсы с частотой, близкой к частоте синхроимпульсов кода, по.ступающих с входа б. Счетчик 14 просчитывает синхроимпульсы, прошедшие через элемент И 17, и периодически обнуляется синхроимпульсами кода. Если синхроимпульсы кода отсутствуют, что соответствует паузе приема последовательного кода, то счетчик 14 считает опорные синхроимпульсы на выходе элемента И 17, т,е. последова. тельно формирует разряды двоичного кода, которые поступают на элементы И 15 и элемент НЕ 16 и последовательно формируют импульс паузы и сигнал запрета счета. Сигнал запрета счета поступает на элемент И 17 и запреща"В связи с этим возникает три слу 35чая работы устройства для преобразования последовательного кода в параллельный: число импульсов кодаравно номинальному (и = И); число40импульсов кода меньше номинального(и ( М); число импульсов кода больше номинального (и ) К),Если количество синхроимпульсовкода равно номинальному, то в допол-,15нительных разрядах (и+1) и (и+2)регистра 1 сдвига оказывается за,писанным коц "10", который поступает на дешифратор 10 состояния дополнительных разрядов блока 3 управления, импульсом паузы запускаетсяФормирователь 11 и формируется им 50пульс, говорящий об окончании приемаи о достоверности принятой информации. Импульс паузы задерживаетсяэлементом 12 задержки на время, не-.у обходимое для уверенной перезаписиинформации из регистра 1 сдвигав буферный регистр 2, и поступаетна Формирователь 13 импульса, где 5 10 15 20 25 ЗО ет йрохождение опорных синхроимпульсов на счетчик 14.Если синхроимпульсы кода есть,что соответствует приему последовательного кода, то счетчик 14 периоди.чески обнуляется с частотой следования синхроимпульсов кода, близкойк частоте следования опорных синхроимпульсов, и импульсы паузы неформируются, Импульсом паузы производится перезапись разрядов информации из регистра 1 сдвига в буферныйрегистр 2.Импульс начальной установки свыхода блока 3 управления поступаетна вход начальной установки регистра1 сдвига и производит его начальнуюустановку, т,е. в младший разряд регистра 1 сдвига записывается " 1",а во все остальные (2 - п + 2) разряды - "0",По мере поступления последовательного кода и синхроимпульсов на сдвиговый регистр 1 осуществляется прием информации по входу 8,При смене канала в многоканальных системах передачи информациипоследовательным кодом количествосинхроимпульсов кода между двумясоседними импульсами паузы можетизменяться в интервале от 1 до 2 Ипри номинальной разрядности последовательного кода и = И,1262732 формируется импульс начальной установки.Если количество синхроимпульсов меньше номинального, то в дополни" тельных разрядах (и+1) и п+2) ре гистра 1 сдвига оказывается записанным код "00", который поступает на дешифратор 10 блока 3 управления и импульсов паузы, формирователь 11 не запускается и сигнал конца преобразования не формируется. Импульс паузы поступает на формирователь 13, где формируется импульс начальной . установки.Если количество синхроимпульсов 15 кода больше номинального, то как только в дополнительном разряде (и+2) регистра 1 сдвига оказывается записанный код "1", который поступает на дешифратор 10 блока 3 управле ния и вызывает запуск формирователя 13 и запрет запуска формирователя 11,25 первым выходом дешифратора,. второй 30 Использование принятой информации осуществляется только по импульсу конца преобразования, формируемому на выходе 9.35 1, Преобразователь последовательного кода в параллельный, содержа- .щий регистр сдвига, о т л и ч а ющ и й с я тем, что, с целью повышения достоверности и расширения области применения путем преобразования кода различной разрядности,в него введены буферный регистр,блок управления и блок выделения.паузы, выход которого соединен свходами управления буферного регистра и блока управления, и информационных выходов регистра сдвига соедине- оны с соответствующими информационТаким образом, формирование импульса начальной установки осуществляется блоком 3 управления при наличии импульса паузы или при появ ленин в (и+2) дополнительном разряде регистра 1 сдвига кода " 1",Формула изобретения ными входами буферного регистра, выход которого является выходом устройства, (и+1) и (и+2) выходов регистра сдвига соединень. с информаФционными входами блока управления, первый выход которого соединен с первым входом регистра сдвига, а второй выход является дополнительным выходом устройства, первый вход блока выделения паузы является входом синхронизации устройства, а второй вход объединен с вторым входом регистра сдвига и является входом синхроимпульсов кода устройства, третий вход регистра сдвига является .информационным входом устройства.2, Преобразователь по п, 1, о т - л и ч а ю щ и й с я тем, что блок управления содержит дешифратор, первый формирователь импульса, элемент задержки и второй формирователь импульса, вход которого соединен с выходом элемента задержки, вход которого соединен с выход которого соединен с входомпервого формирователя импульса,первый и второй входы дешифратораявляются соответственно входом управления и информацонным входом блока управления, выходы первого и второго формирователей импульса являют". ся соответственно первым и вторым выходами блока управления.3. Преобразователь по п. 1, о т -л и ч а ю щ и й с я тем, что блоквыделения паузы содержит счетчик импульсов, первый элемент И, элемент,НЕ и второй элемент И, выход которого соединен со счетным входом счетчика импульсов, выход старшего разряда которого через элемент НЕ соединен с первым входом второго элементаИ, выходы младшего разряда счетчика импульсов соединены с соответствующими входами первого элемента И,выход которого является выходомблока выделения паузы, второй входвторого элемент И и установочныйвход счетчика импульсов являютсясоответственно первым и вторымвходами блока выделения паузы.1262732 ыГ 4 Составитель Б.ХоТехред В.Кадар ректор Т.Кол тор АЛандор акаэ 5447/ дписн 5 Производственно-полиграфическое предприятие, г.ужгород, ул.Проектна Тираж ВНИИПИ Государств по делам изоб 113035, Москва, Жзбного комитета СССР тений и открытий 5, Раушская наб.,

СмотретьЗаявка

3882694, 09.04.1985

ПРЕДПРИЯТИЕ ПЯ А-7162

СКОРНЯКОВ АНДРЕЙ БОРИСОВИЧ

МПК / Метки

МПК: H03M 7/00

Метки: кода, параллельный, последовательного

Опубликовано: 07.10.1986

Код ссылки

<a href="https://patents.su/4-1262732-preobrazovatel-posledovatelnogo-koda-v-parallelnyjj.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь последовательного кода в параллельный</a>

Предыдущий патент: Преобразователь код-временной интервал

Следующий патент: Преобразователь двоично-десятичных чисел в двоичные

Случайный патент: Питатель