Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

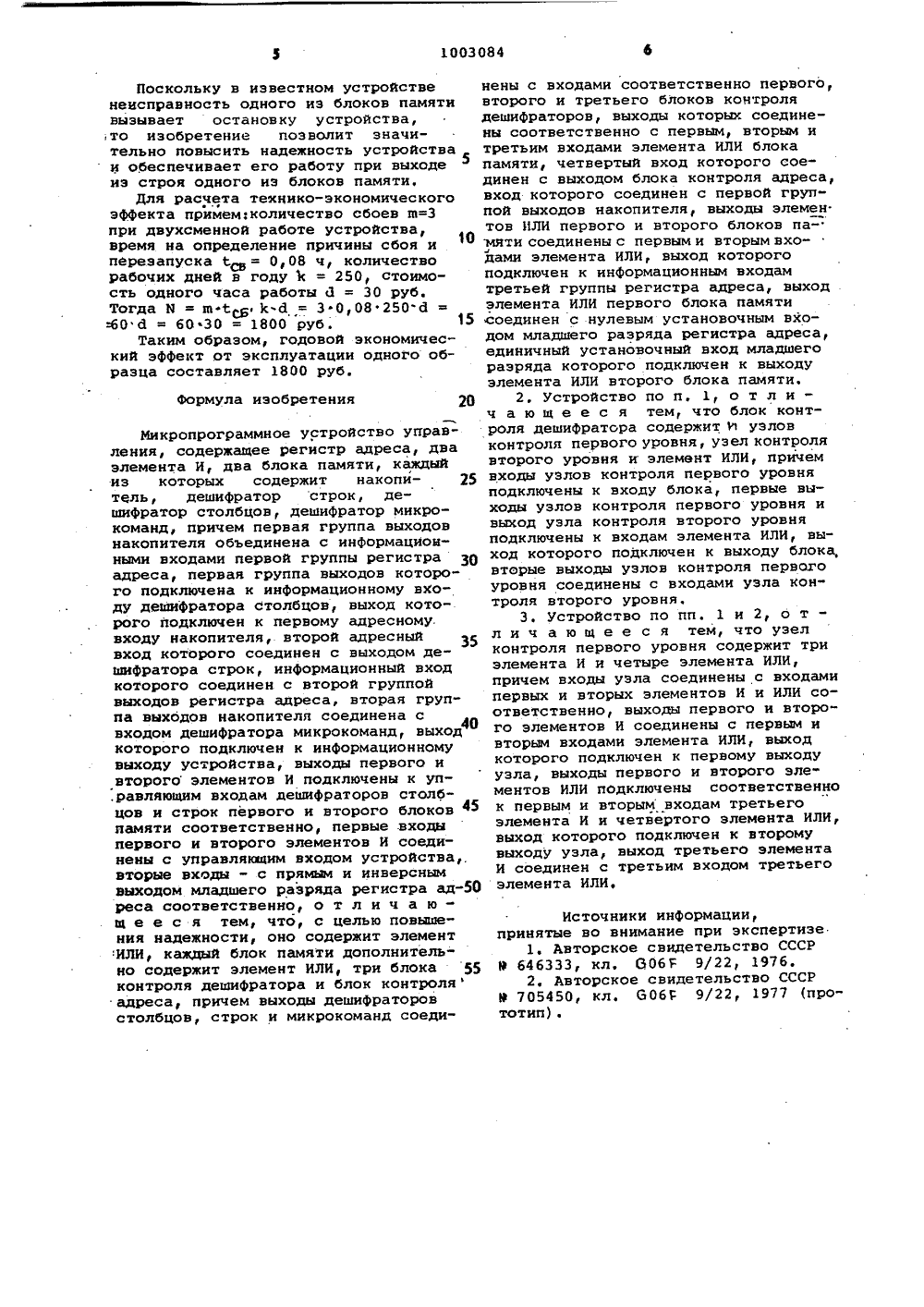

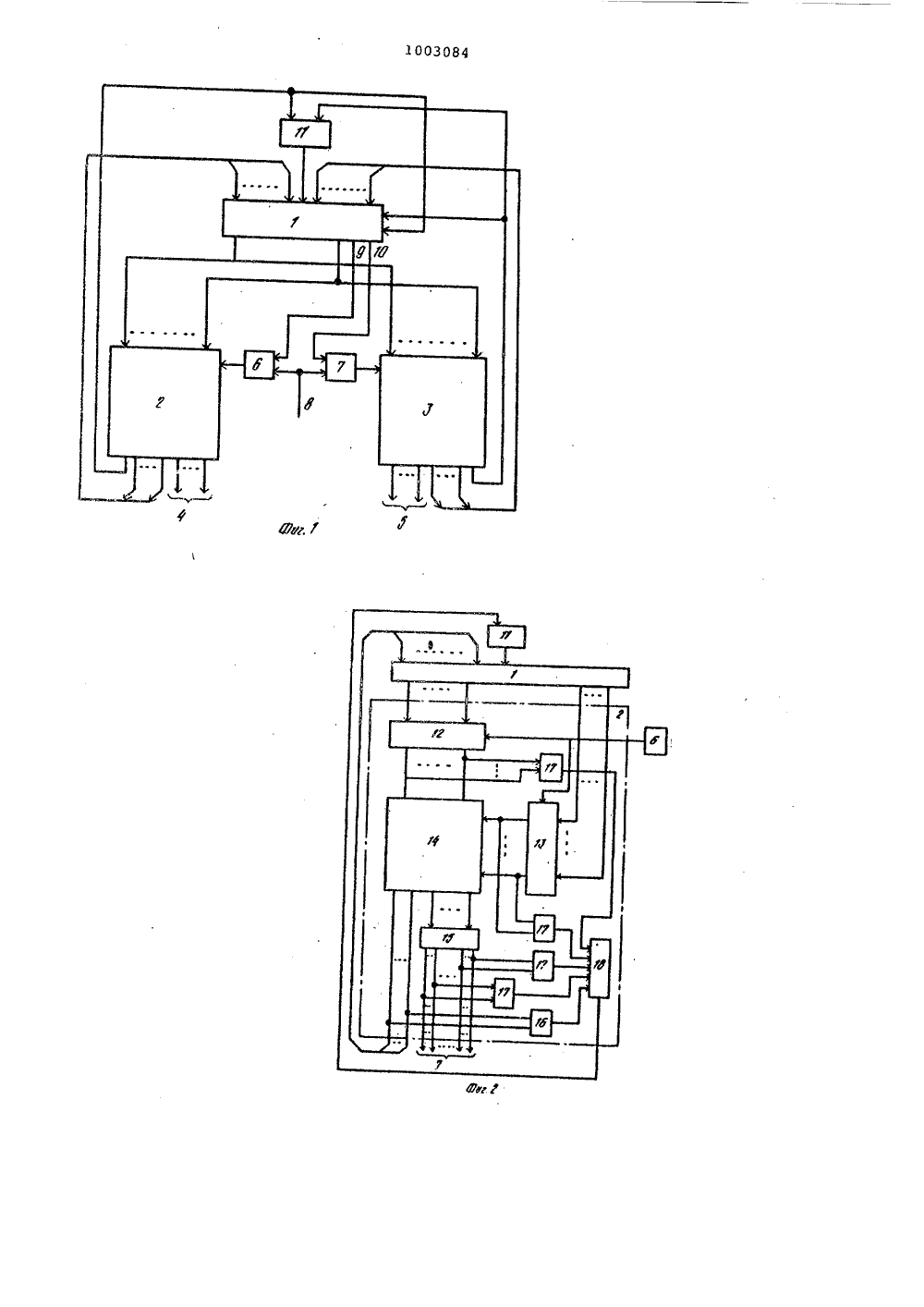

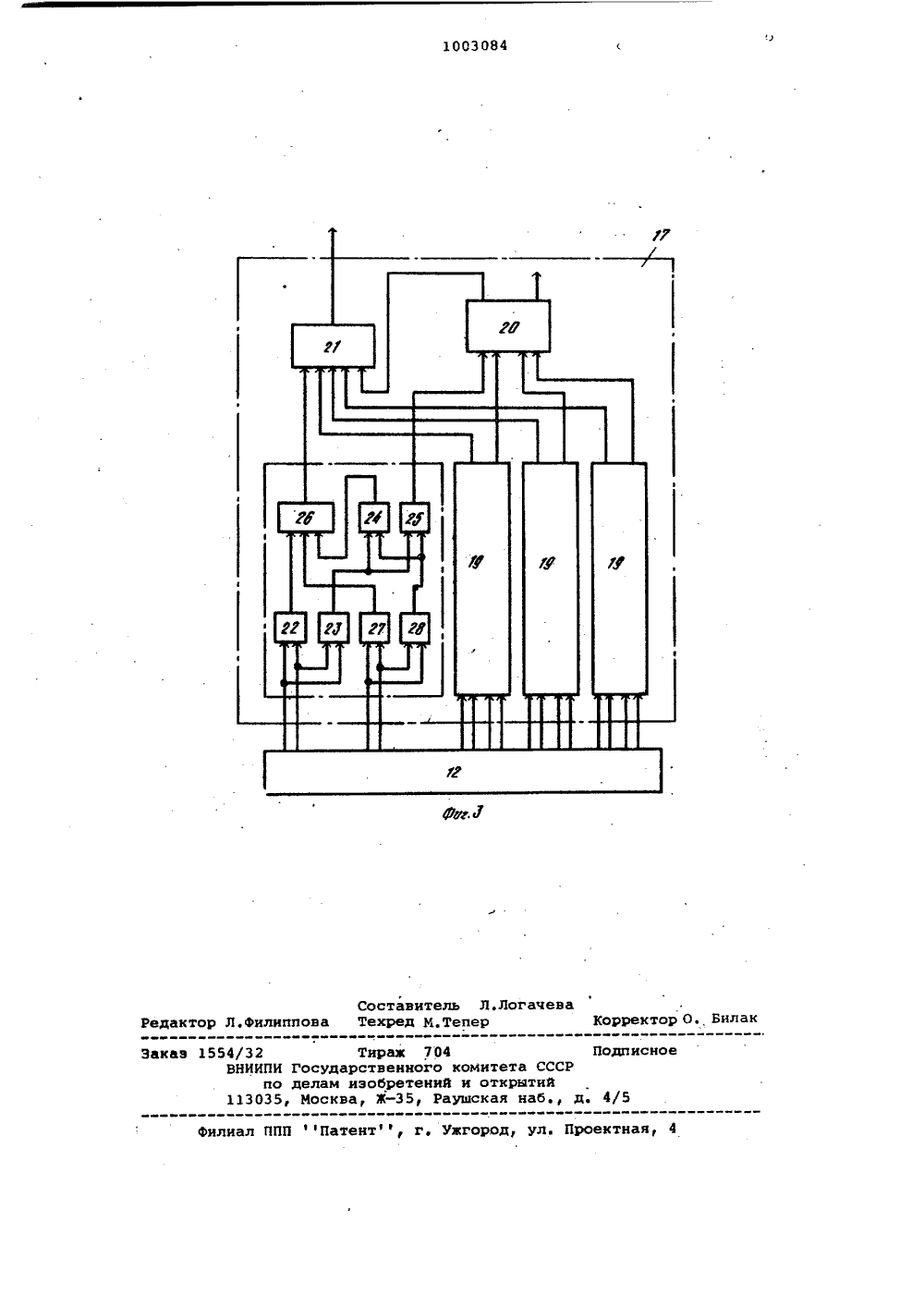

ОР ИСАНИЕ ИЗОБРЕТЕНИЯ Союз СоветскииСоциалистическияРеспубликМ. Кп. 606 Г 9/22 с присоединением заявки МоГосударственный комитет СССР ио делам изобретений и открытий(54) МИКРОПРОГРАММНОЕ УСТРОИСТВО УПРАВЛЕНИЯ Изобретение относится к вычислительной технике и может быть использовано в устройствах управления вычислительных машин.Известно микропрограммное устройство управления, содержащее блоки памяти, регистры адреса, коммутатор, . триггеры, элементы И, элементы ИЛИ, 111.Однако это устройство обладает избытком оборудования.Известно микропрограммное устройство управления, содержащее блоки памяти, регистр адреса, элемент ИЛИ 1 2 ) .Недостаток известного устройства - низкая надежность работы.Цель изобретения - повышение надежности работы устройства.Поставленная цель достигается тем, что микропрограммное устройство управления, содержащее регистр адреса, два элемента И, два блока памяти, каждый иэ которых содержит накопитель, дешифратор строк, дешифратор, столбцов, дешифратор микрокоманд, причем первая группа выходов накопителя соединена с информационньии входами первой группы регистра ацреса, первая группа выходов которого подключена к ин" формационному входу дешифраторастолбцов, выход которого подключен кпервому адресному входу накопителя, 5 второй адресный вход которого соединен с выходом дешифратора строк, информационный вход которого соединенс второй группой выходов регистра адреса, вторая группа выходов накопителя соединена с входом дешифраторамикрокоманд, выход которого подключенк информационному выходу устройства,выходы первого и в срого элементов Иподключенык управлякщим входам дешифраторов столбцов и строк первогои второго блоков памяти соответтвенно, первые входы первого и второгоэлементов И соединены с управлякщимвходом устройства, вторые входы - спрямым и инверсным выходом младшегоразряда регистра адреса соответственно, дополнительно содержит элементИЛЙ, каждый блок памяти дополнительно содержит элемент ИЛИ, три блокаконтроля дешифратора и блок контроляадреса, причем выходы дешифраторовстолбцов, строк и микрокоманд соединены с входами соответственно первоговторого и третьего блоков контролядешифраторов, выходы которых соединены соответственно с первьтл, вторыми итретьим входами элемента ИЛИ блокапамяти, четвертый вход которого соединен с выходом блока контроля адре"са, вход которого соединен с первойгруппой выходов накопителя, выходыэлементов ИЛИ первого и второго блокон памяти соединены с первым и вторым входами элемента ИЛИ, выход которого подключен к информационным входам третьей группы регистра адреса, выход элемента ИЛИ первого блока памяти 10соединен с нулевым установочным входоммладшего разряда регистра адресаединичный установочный вход младшегоразряда которого подключен к выходуэлемента ИЛИ второго блока памяти.Блок контроля дешифратора содержит и узлов контроля первого уровня,узел контроля второго уровня и элемент ИЛИ, причем входы узлов контроляперного уровня подключены к входублока, первые выходы узлов контроляпервого уровня и выход узла контролявторого уровня подключены к входам,элемента ИЛИ,выход которого подключенк выходу блока, вторые выходы. узловконтроля первого уровня соединены свходами узла контроля второго уровня,Узел контроля первого уровня содержит три элемента И и четыре эле- .мента ИЛИ, причем входы узла соединены с входами первых и вторых элементов И и ИЛИ соответственно, выходыпервоГо и второго Элементов И соединены с первым и вторым входами элемента ИЛИ, выход которого подключенк первому выходу узла, выходы первого 35и второго элементов ИЛИ подключенысоответственно к первым и вторым входам третьего элемента И и четвертогоэлемента ИЛИ, выход которого подключен к второму выходу узла, выход тре"40т:,его элемента И соединен с третьимвходом элемента ИЛИ.На Фиг, 1 приведена Функциональнаясхема устройства; на фиг, 2 - функциональнаяя схема блока памяти; на Фиг, 3 -45Функциональная схема блока контролядешифратора,Устройство содержит регистр 1 адререса, первый и нторой блоки 2 и 3памяти, информационные выходы 4 и 5устройства, первый и второй элементыИ 6 и 7, управляющий вход 8 устройства, прямой выход 9 младшего разрядарегистра 1, инверсный выход 10 младшего разряда регистра 1, элементИЛИ 11,Блок 2 (3) памяти (фиг. 2) содержит дешифратор 12 столбцов, дешифратор, 13, блок-накопитель 14, дешифра.тор 15 микрокоманд, блок 16 контроляадреса, блоки 17 контроля дешифратораб 0элемент ИЛИ 18,Блок 17 контроля дешифратора содержит узлы 19 контроля первого уровня,узел 20 контроля второго уровня, элемент ИЛИ 21, каждый узел 19 содержит,б 5 элемент И 22, элемент ИЛИ 23, элементИ 24, элементы ИЛИ 25 и 26, элементИ 27, элемент ИЛИ 28Устройство работает следующим образом.При исправности обоих блоков памяти сигналы на третьих выходах блоковйамяти отсутствуют и устройство раб,тает так же, как и известное. При по"ступлении управлякщего импульса наблок 2 (3) памяти адрес считываемойячейки поступает на дешифраторы 12и 13 столбцов и строк. Считываемаяиз накопителя 14 информация поступает на входы дешифратора 1 микрокоманд15 и на вторую группу выходов блокапамяти.При правильной работе дешифраторов 12 и 13 столбцов и строк сигналдолжен быть только на одном из выхо"дов каждого из них, а при правильнойработе дешифраторов 15 микрокомандсигнал единичного уроння должен бытьна одном из выходов каждой из группмикрокоманд. Правильность работы дешифраторов 12,. 13 и 15 контролируетсяблоками контроля дешифраторов и, еслисигнал единичного уровня присутствуетодновременно на нескольких выходах,ито с выхода соответствующего блока 17контроля дешифраторов сигнал авариичерез элемент ИЛИ 18 поступает натретий выход блока памяти. Правильностьинформации, поступающей на вторуюгруппу выходов блока памяти, контролируется по четности блоком 16 контроля адреса и н случае некорректнос"ти информации с выхода контроля адреса сигнал аварии через элемент ИЛИ 18поступает на третий выход блока памяти,Если из строя вышел первый блок 2памяти, то сигнал с третьего выходапервого блока 2 памяти поступает напервый вход элемента ИЛИ 11, присна,иная старшим разрядам регистра 1 ад" реса значение фиксированного адреса, и на нулевой установочный вход младшего разряда регистра Г адреса, осуществляя таким образом переход на подпрограмму обработки аварии, находящуюся во втором блоке 3 памяти.При выходе из строя второго блока 3 памяти сигнал третьего выхода второго блока 3 памяти поступает на второй вход элемента ИЛИ 11, присна- . иная старшим разрядам регистра 1 адреса значение фиксированного адреса, и на единичный установочный вход млад-. шего разряда регистра 1 адреса, осуществляя таким образом переход на подпрограмму обработки аварии, находящуюся в первом блоке 2 памяти.В обоих случаях подпрограмма обработки аварии анализирует причину отказа блока памяти и при невозможности дальнейшего использования блока памяти обеспечивает работу устройства по усеченной программе.Поскольку в известном устройстве неисправность одного из блоков памяти вызывает остановку устройства, ,то изобретение позволит значительно повысить надежность устройстваи обеспечивает его работу при выходе иэ строя одного из блоков памяти.Для расчета техНико-экономического эффекта примем;количество сбоев в=3 при двухсменной работе устройства, время на определение причины сбоя и перезапуска 1 = 0,08 ч, количество рабочих дней в году к = 250, стоимость одного часа работы й = 30 руб. Тогда В = щ )с-й = 3 0,08250 й :60 а = 60 30 = 1800"руб.Таким образом, годовой экономический эффект от эксплуатации одного образца составляет 1800 руб. Формула изобретения 20 Микропрограммное устройство управления, содержащее регистр адреса, два элемента И, два блока памяти, каждый из которых содержит накопи тель, дешифратор строк, дешифратор столбцов, дешифратор микро- команд, причем первая группа выходов накопителя объединена с информационными входами первой группы регистраЗ 0 адреса, первая группа выходов которо" го подключена к информационному входу дешифратора столбцов, выход которого подключен к первому адресному.входу накопителя, второй адресный вход которого соединен с выходом дешифратора строк, информационный вход которого соединен с второй группой выходов регистра адреса, вторая группа выходов накопителя соединена с входом дешифратора микрокоманд, выход которого подключен к информационному выходу устройства, выходы первого и второго элементов И подключены к уп,равляющим входам дешифраторов столбцов и строк первого и второго блоков 45 памяти соответственно, первые .входы первого и второго элементов И соединены с управляющим входом устройства вторые входы - с прямым и инверсным выходом младшего разряда регистра адреса соответственно, о т л и ч а ю - щ е е с я тем, что, с целью повышения надежности, оно содержит элемент ИЛИ, каждый блок памяти дополнительно содержит элемент ИЛИ, три блока 55 контроля дешифратора и блок контроля адреса, причем выходы дешифраторов столбцов, строк и микрокоманд соедииены с входами соответственно первого,второго и третьего блоков контролядешифраторов, выходы которых соединены соответственно с первым, вторым итретьим входами элемента ИЛИ блокапамяти, четвертый вход которого соединен с выходом блока контроля адреса,вход которого соединен с первой группой выходов накопителя, выходы элементов ИЛИ первого и второго блоков памяти соединены с первым и вторым входами элемента ИЛИ, выход которогоподключен к информационным входамтретьей группы регистра адреса, выходэлемента ИЛИ первого блока памятисоединен с нулевым установочным входом младшего разряда регистра адреса,единичный установочный вход младшегоразряда которого подключен к выходуэлемента ИЛИ второго блока памяти.2. Устройство по п, 1, о т л ич а ю щ е е с я тем, что блок контроля дешифратора содержит И узловконтроля первого уровня, узел контролявторого уровня и элемент ИЛИ, причемвходы узлов контроля первого уровняподключены к входу блока, первые выходы узлов контроля первого уровня ивыход узла контроля второго уровняподключены к входам элемента ИЛИ, выход которого подключен к выходу блока,вторые выходы узлов контроля первогоуровня соединены с входами узла контроля второго уровня,3, Устройство по пп. 1 и 2, о тл и ч а ю щ е е с я тем, что узелконтроля первого уровня содержит триэлемента И и четыре элемента ИЛИ,причем входы узла соединены с входамипервых и вторых элементов И и ИЛИ соответственно, выходы первого и второго элементов И соединены с первым ивторым входами элемента ИЛИ, выходкоторого подключен к первому выходуузла, выходы первого и второго элементов ИЛИ подключены соответственнок первым и вторым входам третьегоэлемента И и четвертого элемента ИЛИ,выход которого подключен к второмувыходу узла, выход третьего элементаИ соединен с третьим входом третьегоэлемента ИЛИ. Источники информации,принятые во внимание при экспертизе 1. Авторское свидетельство СССР Р 646333, кл, 606 Р 9/22, 1976,2. Авторское свидетельство СССР В 705450, кл. 606 Г 9/22, 1977 (прототип).1003084 Составитель Л.ЛогачеваТехред М.Тепер Корректор О. Билак актор Л.филип 54/32 ВНИИП исное каз 113 лиал ППП фПатентфф, г. Ужгород, ул. Проектная,Тираж 704 И Государственного ком о делам иэобретений и 5, Москва, Ж, Рауш итета СССРоткритийкая наб., д. 4/5

СмотретьЗаявка

3271170, 08.04.1981

ПРЕДПРИЯТИЕ ПЯ В-8751

ХЛЮНЕВ АЛЕКСЕЙ ЛЕОНИДОВИЧ, КУЗНЕЦОВ АЛЕКСАНДР АЛЕКСЕЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 07.03.1983

Код ссылки

<a href="https://patents.su/5-1003084-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Генератор одномерных дискретных случайных блужданий

Следующий патент: Устройство микропрограммного управления

Случайный патент: Карабин для тросовых оттяжек