Устройство для обнаружения и исправления ошибок в блоке памяти

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

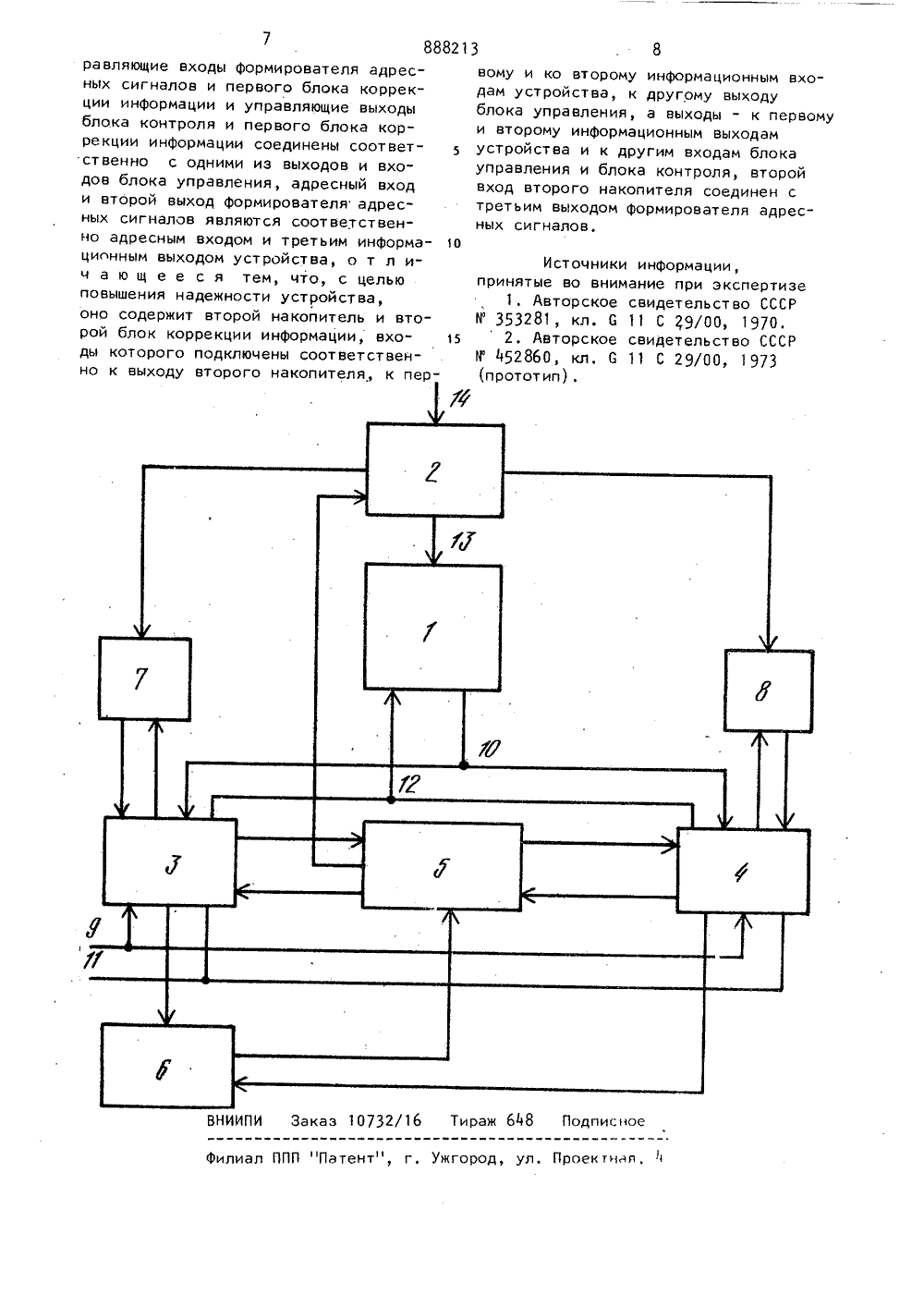

ОП ИСАКИИИЗОБРЕТЕНИЯН АВТОРСКОМУ СВИДЮПЛЬСТВУ Союз СоветскихСоциалистическихРеспубпии гц 888213(23) ПриоритетОпубликовано 071281 бголлетень Ре ЙДата опубликования описания 071 281но ленам нзабретеннй н открытнй(54 УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ И ИСПРАВЛЕНИЯ ОШИБОК В БЛОКЕ ПАМЯТИИзобретение относится к области запоминающих устройств(ЗУ)и может быть использовано для построения ЗУ с избыточностью.Известны устройства для обнаружения и исправления ошибок в блоке па 5мяти Щ 21В одном из известных устройств реализуется способ обнаружения и исправления искажений при записи и счиго тывания двоичной информации из ЗУ, использующий геометрический код, представляющий собой блок данных из а слов по и разрядов в каждом, При этом используется контрольные разряды,г 5 образующиеся при суммировании по модулю два как по строкам, так и по столбцам 11.Недостатком этого устройства является низкая надежность.Из известных устройств наиболее близким техническим решением к изоб- . ретению является устройство, содержащее регистр числа, накопитель, блок 2свертки по модулю два, сумматор, регистр контрольного слова и блок анализа числа единиц Г 2Недостатком этого устройства является низкая надежность вследствие недостаточной эффективности контроля и восстановления информации при многократных искажениях в одном или нескольких различных словах блока данных, предназначенного дпя хранения в ЗУ.Целью изобретения является повышение надежности устройства.Поставленная цель достигается тем, что в устройстве для обнаружения и исправления ошибок в блоке памяти, содержзщее формирователь адресных сигналов, первый блок коррекции информации, блок управления, блок контроля и первый накопитель, входы которого подключены соответственно к первым выходам формирователя адресных сигналов и первого блока коррекции. информации, а выход - к первому входу88821 15 первого блока коррекции информации,второй. и третий входы которого являются соответственно первым и вторыминформационными входами устройства,второй выход подключен к одному иэвходов блока контроля, а третий ичетвертый выходы являются соответственно первым и вторым информационными выходами устройства, управляющие входы формирователя адресных 1 Осигналов и первого блока коррекцииинформации и управляющие выходы блока контроля и первого блока коррекции и нформа ции соединены соот еет ственно с одними иэ выходов и входовблока управления, адресный вход ивторой выход формирователя адресныхсигналов являютсе соответственно адресным входом и третьим информационнымвыходом устройства, введены второй Онакопитель и второй блок коррекцииинформации, входы которого подключены соответственно к выходу второгонакопителя, к первому и ко второмуинформационным входам устройства, к р 5другому выходу блока управления,а выходы - к первому и второму информационным выходам устройства и к другим входам управления и блока контроля. Второй вход второго накопителясоединен с третьим выходом формирователя адресных сигналов,На чертеже изображена фуййЦйональная схема предложенного устройстваи контролируемый блок памяти 1.Устройство содержит формировательадресных сигналов 2,первый 3 и второй 4блоки коррекции информации, блок управления 5, блок контроля 6, первый 7и второй 8 накопители,Входы накопителя 7 подключены соответственно к первым выходам формирователя адресных сигналов 2 и блока информации 3, а выход - к первомувходу блока коррекции информации 345второй и третий входы которого являются соответственно первым 9 ивторым 10 информационными входамиустройства, второй выход подключенк одному иэ входов блока контроля 6,а третий и четвертый выходы являются50соответственно первым 11 и вторым 12информационными .выходами устройства.Управляющие входы формирователя 2 иблока коррекции информации 3 и управляющие выходы блока контроля 655и блока коррекции информации 3 соединены соответственно с одними извыходов и входов блока управления 5,3 4Адресный вход и второй выход формирователя 2 являются соответственноадресным входом 14 и третьим информационным выходом 13 устройства. Входыблока коррекции информации 4 подключены соответственно к выходу накопителя 8, к первому 9 и ко второму 10информационным входам устройства,к другому выходу блока управления 5,а выходы - к первому 11 и второму 12информационным выходам устройстваи к другим входам блока управления 5и .блока контроля 6. Второй вход накопителя 8 соединен с третьим выходом формирователя 2.Устройство работает следующимобразом.Вся информация, хранимая в блокепамяти 1 е виде блоков данных в геометрическом коде, дополнительно компонируется в другие блоки данных,отличные от первых и составленные изслов, входящих в разные исходные блоки данных. Новые блоки данных также;представляются в геометрическом коде.При этом каждое кодовое слово данных,запоминающее физически всего однуячейку накопителя, входит е несколько независимых блоков даннных в геометрическом коде, что позволяет контролировать и восстанавливать данноеслово с эффективностью, пропорциональной количеству независимых блоков, пересекающихся по данному слову,Способ заключается в том, что приобнаружении аппаратными средствамиконтроля (например, по числовомумодулю) искажения в считываемом двоичном кодовом слове считываются изгруппы ячеек блока памяти 1, в которых размещен первый блок данных, ипорязрядно суммируются по модулюдва все слова этого блока данных,включая контрольное слово, но заисключением восстанавливаемого слова.При этом каждый разряд контрольногослова представляет собой г,оразрядную сумму по модулю два всех слов,входящих в этот блок данных. Формирование контрольных слов производится заранее аппаратным способом в. процессе функционирования блока памяти (например, для постоянного ЗУконтрольные слова заранее заносятсяв соответствующие ячейки накопителя). Оставшееся на сумматоре словоявляется восстановленным с достоверностью аппаратного контроля в случае88213 6 30 33 Формула изобретения И му из входов блока контроля, а третий и четвертый выходы являются соответственно первым и вторым инфор 5 8положительного результата этого контроля для всех суммируемых слов, В: противном случае искаженное слово неможет быть восстановлено с помощьюпервого блока данных, и считываются и поразрядно суммируются по модулю два все слова второго блокаданных, также включающего в себявосстанавливаемое слово. Процедуравосстановления искаженного словатаким образом повторяется с исполь"зованием слов второго блока данных.В случае невозможности восстановления искаженного слова по второмублоку данных( при отрицательном результате аппаратного контроля в процессе считывания суммируемых слов),аналогично считываются и суммируются слова третьего блока данных ит.д. до тех пор, пока исправленноеслово не будет считано из.блока па.мяти 1. В.противном случае формируется сигнал неисправности блока памяти 1. Количество блоков данных пересекающихся по восстанавливаемому слову,(записанному физически в однойячейке блока памяти 1) определяетсятребованиями к эффективности восстановления информации .При записи слова по. выбранномуадресу сначала из накопителей 7, 8в блоки коррекции информации 3 и 4считываются контрольные числа посоответствующим адресам, а из блокапамяти 1 считывается ранее запомненное по данному адресу слово. Затемв каждом из блоков коррекции информацйи 3 и 4 информационное и контрольное слова проверяются по модулю спомощью блока контроля 6, при отсутст;вии на его выходе сигнала об ошибкесчитанное слово складывается по модулю два с соответствующим контрольным словом. Получившиеся суммы вобщем случае различны,Записываемое число поступает попервому информационному входу 9 навходы блоков коррекции информации 3и 4, суммируется.по модулю два сконтрольными словами, после чего.получившиеся значения контрольных словзаносятся в накопители 7 и 8 по соответствующим адресам, которые форми- .руются формирователем 2 и выдаютсяпо первому и третьему выходам формирователя 2 на входы накопителей 7 и 8.При считывании слова из блока памяти 1 оно поступает в блоки коррекции информации 3 и 4. При этом от" сутствие ошибок в слое проверяетсяс помощью блока контроля 6, При обнаружении ошибки с выхода блока контроля 6 в блок управления 5 поступает сигнал ошибки, после чего производится считывание всего блокаданных, за исключением корректируемого слова, и суммирование по модулю два с предварительно считаннымииз накопителя 7 контрольным слов.м,соответствующим данному блоку данных. ,Если в процессе считывания блока данных блоком контроля 6 не выдан сигнал ошибки, то получившееся в результате .такого суммирования по модулю два слово с достоверностью аппаратногоконтроля является восстановительными выдается на выход 11. Если присчитывании всего блока данных зафиксирована многократная ошибка блоком контроля 6, блок управления 5инициирует работу блока коррекцииинформации 4, который восстанавливает данное слово, находящееся уже всоставе другого блока данных, пересекающегося с исходными по восстановливаемому слову,В постоянном блоке памяти 1 контроль и исправление информации производятся аналогично, но массивы контрольных слов Формируются заранее и заносятся в накопители 7 и 8.Технико-зкономическое преимущество описываемого устройства заключается в более высокой по сравнению с прототипом надежности. Устройство для обнаружения и исправления ошибок в блоке памяти, содержащее формирователь адресных сигналов, первый блок коррекции информации, блок управления, блок контроля и первый накопитель, входы которого подключены соответственно к первым выходам формирователя адресных сигналов и первого блока коррекции информации, а выход - к первому вхо" ду первого блока коррекции информации, второй и третий входы которого являются соответственно первым и втоРым информационными входами устройства; второй выход подключен к одномационными выходами устройства, уп888213 равляющие входы формирователя адресных сигналов и первого блока коррекции информации и управляющие выходыблока контроля и первого блока коррекции информации соединены соответственно с одними из выходов и входов блока управления, адресный входи второй выход формирователя адресных сигналов являются соответственно адресным входом и третьим информационным выходом устройства, о т л ич а ю щ е е с я тем, что, с цельюповышения надежности устройства,оно содержит второй накопитель и второй блок коррекции информации, входы которого подключены соответственно к выходу второго накопителя, к первому и ко второму информационным входам устройства, к другому выходублока управления, а выходы - к первомуи второму информационным выходамустройства и к другим входам блокауправления и блока контроля, второйвход второго накопителя соединен стретьим выходом формирователя адресных сигналов,Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРЙ 353281, кл. С 11 С 9/00, 1970.2, Авторское свидетельство СССРИ Ц 52860, кл. С 11 С 29/00, 1973

СмотретьЗаявка

2893517, 10.03.1980

ОРДЕНА ОКТЯБРЬСКОЙ РЕВОЛЮЦИИ И ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ПРЕДПРИЯТИЕ ПЯ В-2969

ВЕРБИЦКИЙ ЮРИЙ ГРИГОРЬЕВИЧ, ЗЕЛЕНИНА ГАЛИНА ПАВЛОВНА

МПК / Метки

МПК: G11C 29/00

Метки: блоке, исправления, обнаружения, ошибок, памяти

Опубликовано: 07.12.1981

Код ссылки

<a href="https://patents.su/4-888213-ustrojjstvo-dlya-obnaruzheniya-i-ispravleniya-oshibok-v-bloke-pamyati.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обнаружения и исправления ошибок в блоке памяти</a>

Предыдущий патент: Устройство для контроля запоминающих матриц

Следующий патент: Запоминающее устройство с самоконтролем

Случайный патент: Штамп для обработки полосового и ленточного материала