Устройство для формирования контрольных разрядов логических операций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 570898

Автор: Карпухин

Текст

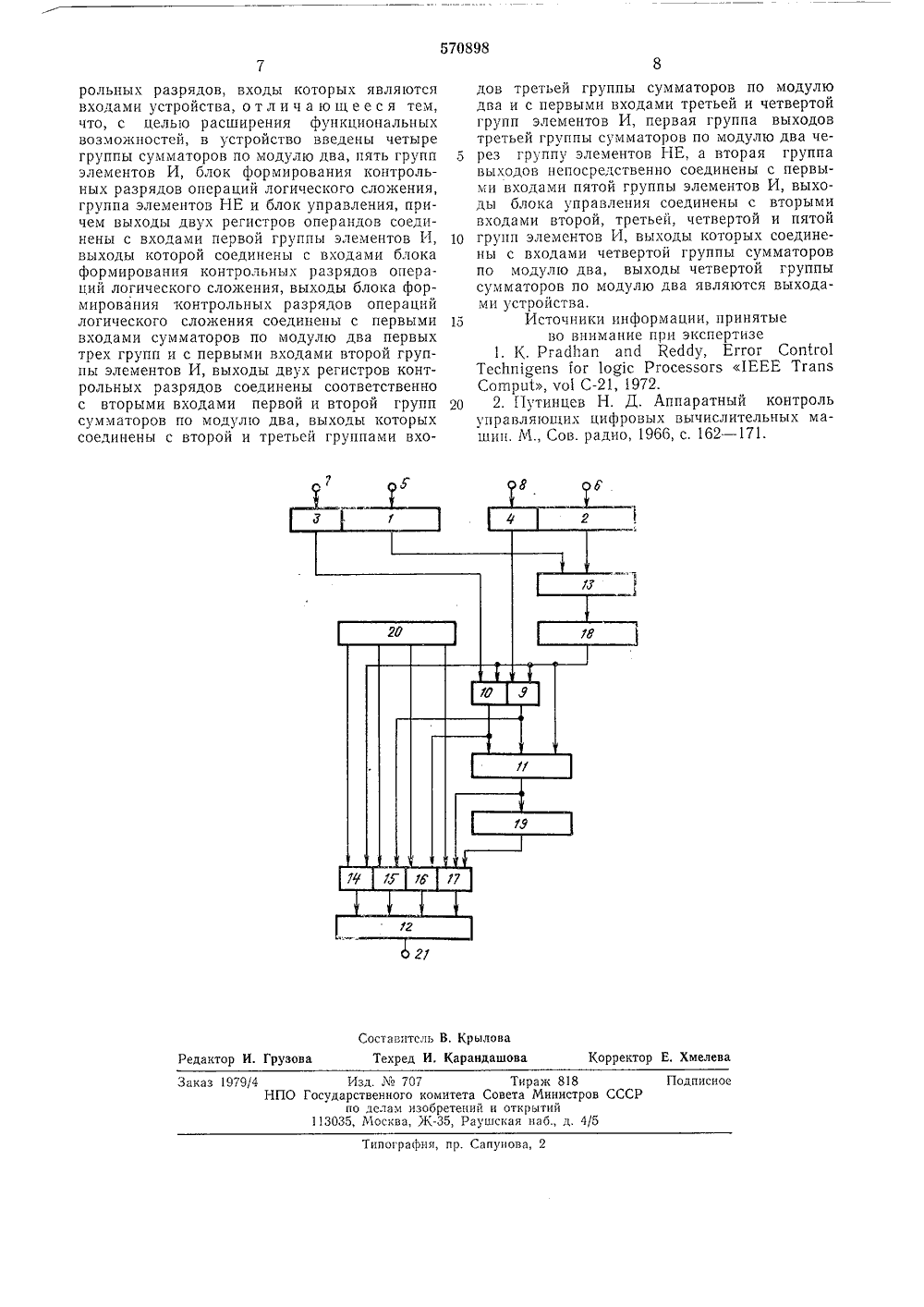

ш 570898 Союз Советских Социалистических Реолублик(61) Дополнительное к (22) Заявлено 02.06.75 т,2139749 51) М. Кл6 06 Г 11/1 с прис нением яв Опубликовано 30,08.77. Бюл 53) УДК 681.326.75(088.8) тень М о делам изобрете и открытий та опубликовани 4.09.77 ис(72) Автор изобретения ар пухи 1) Заявител 54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ КОНТРОЛЬНЬ 1 Х РАЗРЯДОВ ЛОГИЧЕСКИХ ОПЕРАЦИЙ2 государственныи комитет (23) Приор итСовета Министров СССР Изобретение относится к вычислительной технике и может быть использовано в устройствах обнаружения и исправления 1-кратных ошибок логических операций.Известно устройство для формирования контрольных разрядов некоторых логических операций кодом Рида - Маллера 1.Однако это устройство имеет большую кодовую избыточность при реальной разрядности вычислительных машин, Например, защита от тройных ошибок результата логической операции над 16-разрядными операциями требует 112 избыточных разрядов, что равносильно 8-кратному резервированию.Известно также наиболее близкое по техническому решению к изобретению устройство для формирования контрольных разрядов логических операций, содержащее два регистра операндов и два регистра контрольных разрядов, входы которых служат входами устройства 2.Недостатком этого устройства является невозможность получения контрольных разрядов любой логической операции на одном оборудовании.Цель изобретения - расширение функциональных возможностей устройства путем обеспечения возможности формирования любых логических операций по единому алгоритЭто достигается тем, что в устроиство введены четыре группы сумматоров по модулю два, пять групп элементов И, блок формирования контрольных разрядов операций логи ческого сложения, группу элементов НЕ иблок управления. Выход двух регистров операндов соединены с входами первой группы элементов И, выходы которой подключены к входам блока формирования контрольных 0 разрядов операций логического сложения, выходы блока формирования контрольных разрядов операций логического сложения - с первыми входами сумматоров по модулю два первых трех групп и с первыми входами вто рой группы элементов И. Выходы двух регистров контрольных разрядов подключены соответственно к вторым входам первой и второй групп сумматоров по модулю два, выходы которых связаны с второй и третьей 20 группами входов третьей группы сумматоровпо модулю два и с первыми входами третьей и четвертой групп элементов И. Первая группа выходов третьей группы сумматоров по модулю два через группу элементов НЕ, а 25 вторая группа выходов непосредственно соединены с первыми входами пятой группы элементов И, выходы блока управления - с вторыми входами второй, третьей, четвертой и пятой групп элементов И, выходы которых ЗО подключены к входам четвертой группы сумматоров по модулю два, выходы четвертойгруппы сумматоров по модулю два являютсявыходамп устройства.Принцип действия устройства заключаетсяв следующем, 5Пусть две двоичные последовательностиА=(а ал 1, а а,)В=(Ь Ь 1, Ьл - ,. , Ц10защищенные систематическим линейным кодом, имеют Й контрольных и /г - /г = )гг информационных разрядов, Требуется произвести над разрядами этих последовательностейодну из 1 б логических операций таким образом, чтобы результат логической операциитакже имел бы правильные контрольные разряды.Переведем разряды двоичных последовательностей Л и В вместс с контрольными разрядами из элементов аддитивной группы поля6 Р (2) в элементы 0 = (00) и 2 = (10) дляпоследовательности Л и в элементы 0 = (00)и 1 = (01) для последовательности В аддитивной группы поля 6 Р (2). Обозначим полученные последовательности буквами А и Всоответственно,Известно, что любая логическая операциядвух аргументов а; и Ь; может быть представлена уравнением 30(агЬ 1)= аг ЬР, , Я 1 ЬР/ агЬРз / агЬ 14 (1)где к - управляющие сигналы.Представим каждый член дизъюнкции (1)(за исключением управляющих сигналов а,) З 5в виде элементов поля 6 Р (22), т, е, а(Ь( (== )00, так как если аг = Ь; = О, то а;Ь; = 1.Аналогично, аА( = ) 01, а,Ь;( = ) 10,а,Ь;(= )11, где 00, 01, 10, 11 я 6 Р(22), Тогда при сложении в поле 6 Р(2) соответствующих разрядов последовательностей А и Вобразуется последовательность, имеющая правильные контрольные разряды применяемоголинейного кода. Обозначим эту последовательность буквой С.Однако для выполнения какой-либо логической операции из совокупности четырех членов дизыонкции (1) необходимо выбратьлишь заданные управляющими сигналами а, 50Обозначим:С, С - контрольные разряды последова(,)тельностей С и С( ), где Ч =( )14,аждой последовательности Сл, соответствует своя последовательность контрольных 60разрядов С, образованная в соответствии спроверочной матрицей применяемого линейного кода, Очевидно, чтоС, = С+ С+ С, (2) 65 где + - сумма в поле 6 Р(2), так как в противном случае последовательность С в соответствии с доказанным утверждением правильная, т. е. ей не соответствует последовательность Ст.Если из последовательности С, содержащей все четыре элемента поля 6 Р(2), выделить контрольные разряды соответствующего линейного кода по одному из элементов поля, например по элементу Зя-:6 Р(22), и составить последовательность С(3), то последователь 3ность Ст = С,л + Ст (вычитание в поле 6 Р(2") эквивалентно сложению) будет содержать только три элемента поля 6 Р(2). Тогда разряды последовательности С = С + С, равные 3, будут суммой соответствующих раз 1 2рядов последовательностей С и С, а равные 1 и 2 - разрядами последовательностейгС и С соответственно. Если разряды последовательности С равны нулю, то соответствующие разряды последовательностей3 2 1С, С и С также равы нулю.Для определения контрольных разрядов последовательности С(о) переведем разряды выделенных из С последовательностей С, С, С в элементы поля 6 Р(2). Очевидно, что полученные таким образом последовательности имеют правильные контрольные разряды применяемого систематического линейного кода,Обозначим эти последовательности С ), где в общем случае Ч = О, 1, 2, 3; так как сумма четного числа единиц по модулю два равна нулю, а нечетного числа единиц - единице, контрольные разряды последовательности С равны(3)где 4=(+), если число единиц в 1-й строкепроверочной матрицы четное;= ( ), если число единиц нечетное.Очевидно, что полученные последовательности С(о), С(1), С(2), С(3) имеют правильные контрольные разряды и у суммы в поле 6 Р(2) (т, е, по модулю два) любых из них правильные контрольные разряды. Таким образом, можно сформировать 1 б последовательностей, компоненты которых соответствуют 1 б логическим функциям двух переменных а; и Ь;, Любую из этих последовательностей можно получить из выраженияу( ) - . С(о) о Г- С г., ( ) С г, (+) С (4)где п = 0,15 - десятичная форма записи двоичного числа (ць аг С 43 а 4)Так как соответствующие разряды последовательности Сл, не пересекаются,10 15 На основании изложенного алгоритм формирования контрольных разрядов результаталогических операций над последовательностями, имеющими контрольные разряды систематического линейного кода, можно сформулировать следующим образо.;(;1) каждым двум разрядам а;, Ь, е=6 Р(2)входных последовательностей А = (аа - +ь а - а,), В = (Ь Ь -+иЬй -., Ь 1) ставится в соответствие компонента С;е:=6 Р (2) последовательности С=(з) р)и С переводятся в элементы поля 6 Р(2) инад ними выполняется операция (3) для определения С,(о) .5) над разрядами последовательностей(о) .(1)С , С( ), С( ), С ) производится операция (4).Полученная последовательность - результат одной из 16 поразрядных логических операций - имеет правильные контрольные разряды соответствующего систематического линейного кода при условии, что входные последовательности А и В были правильными.На чертеже представлена блок-схема предлагаемого устройства.Устройство содержит регистры 1 и 2 операндов, регистры 3 и 4 контрольных разрядов,входы которых являются входами 5, 6, 7 и 8устройства соответственно группы 9 - 12 сумматоров по модулю два, группы 13 - 17 элементов И, блок 18 формирования контрольных разрядов операций логического сложения, группу 19 элементов НЕ и блок 20 управления.Выходы регистров 1 и 2 соединены с входами группы 13 элементов И, выходы которойподключены к входам блока 18 формирования контрольных разрядов операций логического сложения, выходы блока 18 - с первыми входами групп 9, 10 и 11 сумматоров помодулю два и с первыми входами группы 14элементов И, Выходы регистров 3 и 4 подклочены к вторым входам групп 9 и 10 сумматоров по модул(о два, выходы которых связаны с вторыми и тр тьими входами группы11 сумматоров по модулю два и с первымивходами групп 15 и 16 элементов И.Выходы группы 11 сумматоров по модулюдва, которым соответствуют строки матрицыприменяемого систематического линейного кода с нечетным числом единиц, через группу 19элементов НЕ, а остальные непосредственносоединены с первыми входами группы 17 элементов И, а выходы блока 20 управления - с 20 25 30 35 40 45 50 55 60 65 вторыми входами групп 14 - 17 элементов И Выходы групп 14 - 17 элементов И подключены к входам группы 12 сумматоров по модулю два, выходы которой являются выходами21 устройства.Устройство работает следующим образом.Сигналы с регистров 1 и 2 поступают нагруппу 13 элементов И, где формируются(з)функции С( = а,Ь;. С выходов группы 1 3 сигналы подаются на блок 1 8 формирования контрольных разрядов функций СР . Сигналы с выходов блока 18 поступают на одни входы групп 9 и 10 сумматоров по модулю два. Истинные значения сигналов с группы 9 являются контрольными для последовательности С(, а с выходов группы 10 - для последовательности С. Истинные значения сигналов с блока 18 и групп 9 и 10 поступают на ьходы группы 11 сумматоров, а с выходов группы 11, которым соответствуют строки матрицы применяемого систематического линейного кода с нечетным числом единиц, через группу 19 элементов НЕ, а с остальных - непосредственно, сигналы, являющиеся контрольными для последовательности С(о), поступают на одни входы группы 17 элементов И. Сигналы с выходов блока 18 и групп 9 и 10 подаются на первые входы групп 14, 15, 16 элементов И соответственно. На вторые входы групп 14 - 17 поступают сигналы с выходов блока 20 управления, а с выходов групп 14 - 17 - на входы группы 12 сумматоров по модулю два, в которой формируются контрольные разряды результата заданной управляющими сигналами логической операции.Если 1 (или менее) ошибок произошло при формировании функции С; = а;Ь;, то они(з)искажают только(или менее) последовательности 2;("), т, е. ошибки также не будут размножены. Ошибки, возникшие при формировании контрольных разрядов логических операций, исправляются последующими исправляющим слоем.Перевод входных двоичных последовательностей, защищенных систематическим линейным кодом, в последовательность с компонентами из поля 6 Р(2) позволяет выделить в ней элементы С = а;Ь( и затем применить(з)единый алгоритм для определения контрольных разрядов люоой логической операции,Предлагаемое устройство формирования контрольных разрядов логических операций дает возможность распространить корректируюц(ую способность систематического линейного кода на любые поразрядные логические операции.Ф ор мул а изобретенияУстройство для формирования контрольных разрядов логических операций, содержащее два регистра операндов и два регистра конт570898 Составитель В, Крылова Техред И. Карандашова Корректор Е. Хмелева Редактор И. Грузова Заказ 1979/4 Изд. Уо 707 Тираж 818 НПО Государственного комитета Совета Министров СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д. 4/5Подписное Типография, пр. Сапунова, 2 рольных разрядов, входы которых являются входами устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возмокностей, в устройство введены четыре группы сумматоров по модулю два, пять групп элементов И, блок формирования контрольных разрядов операций логического сложения, группа элементов НЕ и блок управления, причем выходы двух регистров операндов соединены с входами первой группы элементов И, выходы которой соединены с входами блока формирования контрольных разрядов операций логического сложения, выходы блока формирования контрольных разрядов операций логического слояения соединены с первыми входами сумматоров по модулю два первых трех групп и с первыми входами второй группы элементов И, выходы двух регистров контрольных разрядов соединены соответственно с вторыми входами первой и второй групп сумматоров по модулю два, выходы которых соединены с второй и третьей группами входов третьей группы сумматоров по модулю два и с первыми входами третьей и четвертой групп элементов И, первая группа выходов третьей группы сумматоров по модулю два че рез группу элементов НЕ, а вторая группавыходов непосредственно соединены с первыми входами пятой группы элементов И, выходы блока управления соединены с вторыми входами второй, третьей, четвертой и пятой 10 групп элементов И, выходы которых соединены с входами четвертой группы сумматоров по модулю два, выходы четвертой группы сумматоров по модулю два являются выходами устройства.15 Источники информации, принятыево внимание при экспертизе1. К. Ргас 111 ап апс 1 КесЫу, Еггог Соп 1 го 1Тес 11 п 1 оепэ 1 ог 1 орс Ргосеззогэ 1 ЕЕЕ Тгапз Согпри 1, ю 1 С, 1972.20 2. Г 1 утинцев Н. Д. Аппаратный контрольуправляющих цифровых вычислительных машин. М., Сов. радио, 1966, с, 162 - 171.

СмотретьЗаявка

2139749, 02.06.1975

ПРЕДПРИЯТИЕ ПЯ Р-6052

КАРПУХИН АНАТОЛИЙ ИВАНОВИЧ

МПК / Метки

МПК: G06F 11/10

Метки: контрольных, логических, операций, разрядов, формирования

Опубликовано: 30.08.1977

Код ссылки

<a href="https://patents.su/4-570898-ustrojjstvo-dlya-formirovaniya-kontrolnykh-razryadov-logicheskikh-operacijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для формирования контрольных разрядов логических операций</a>

Предыдущий патент: Устройство для получения тестов бесповторных комбинационных схем

Следующий патент: Корректирующее устройство

Случайный патент: Способ очистки нефтяных остатков