Устройство для обнаружения и исправления ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1149263

Авторы: Белалов, Рудаков, Саламатов, Чалчинский

Текст

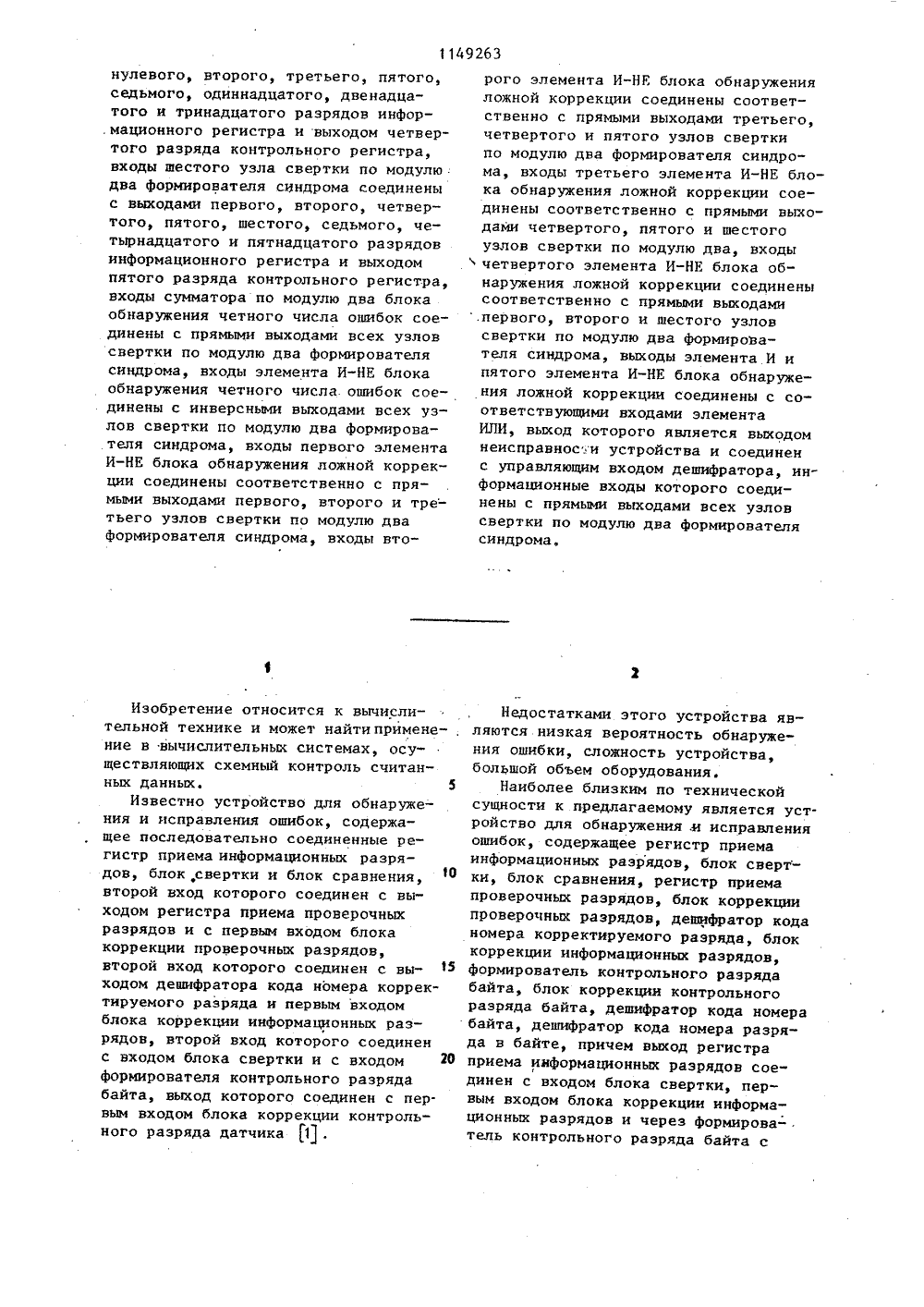

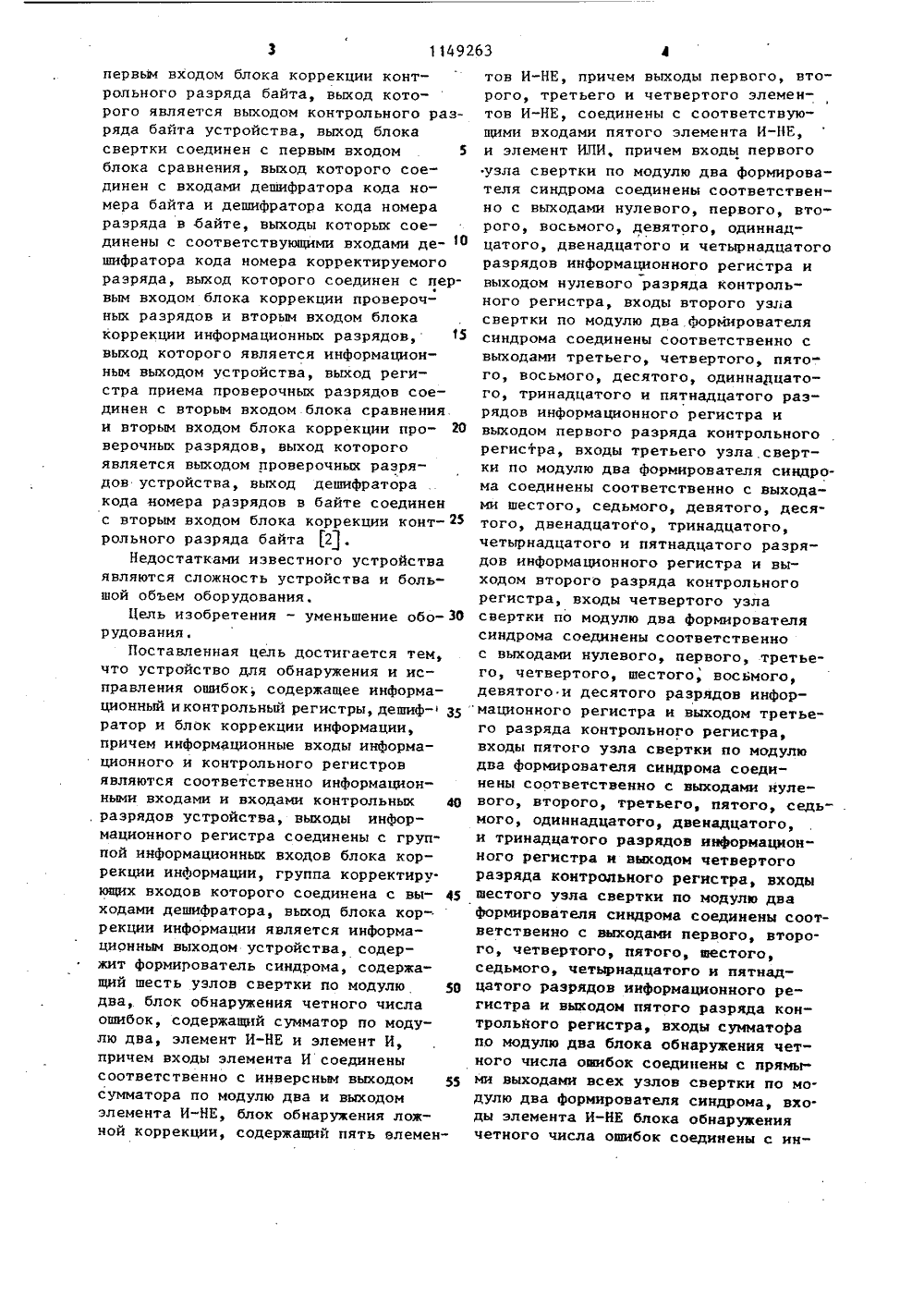

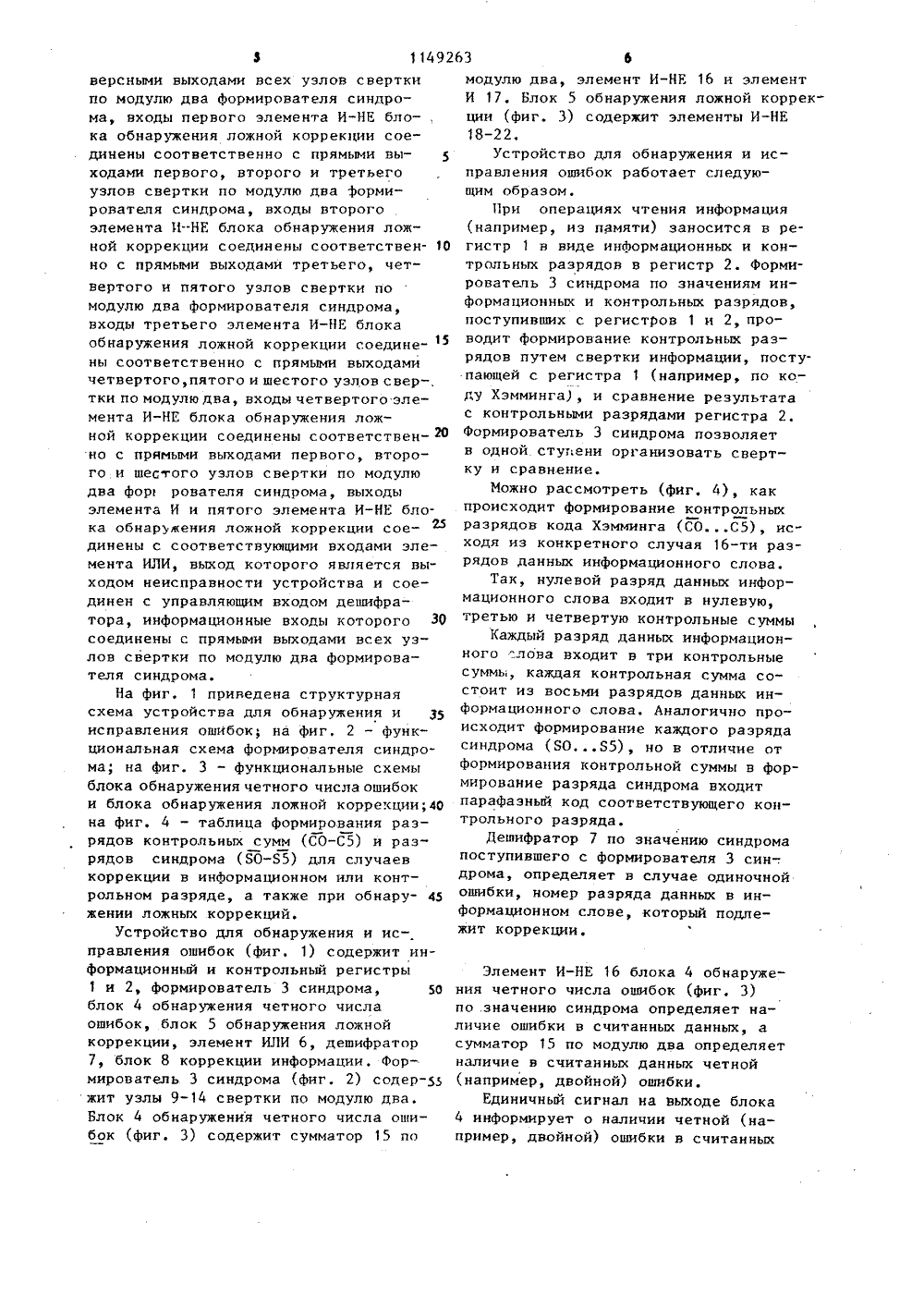

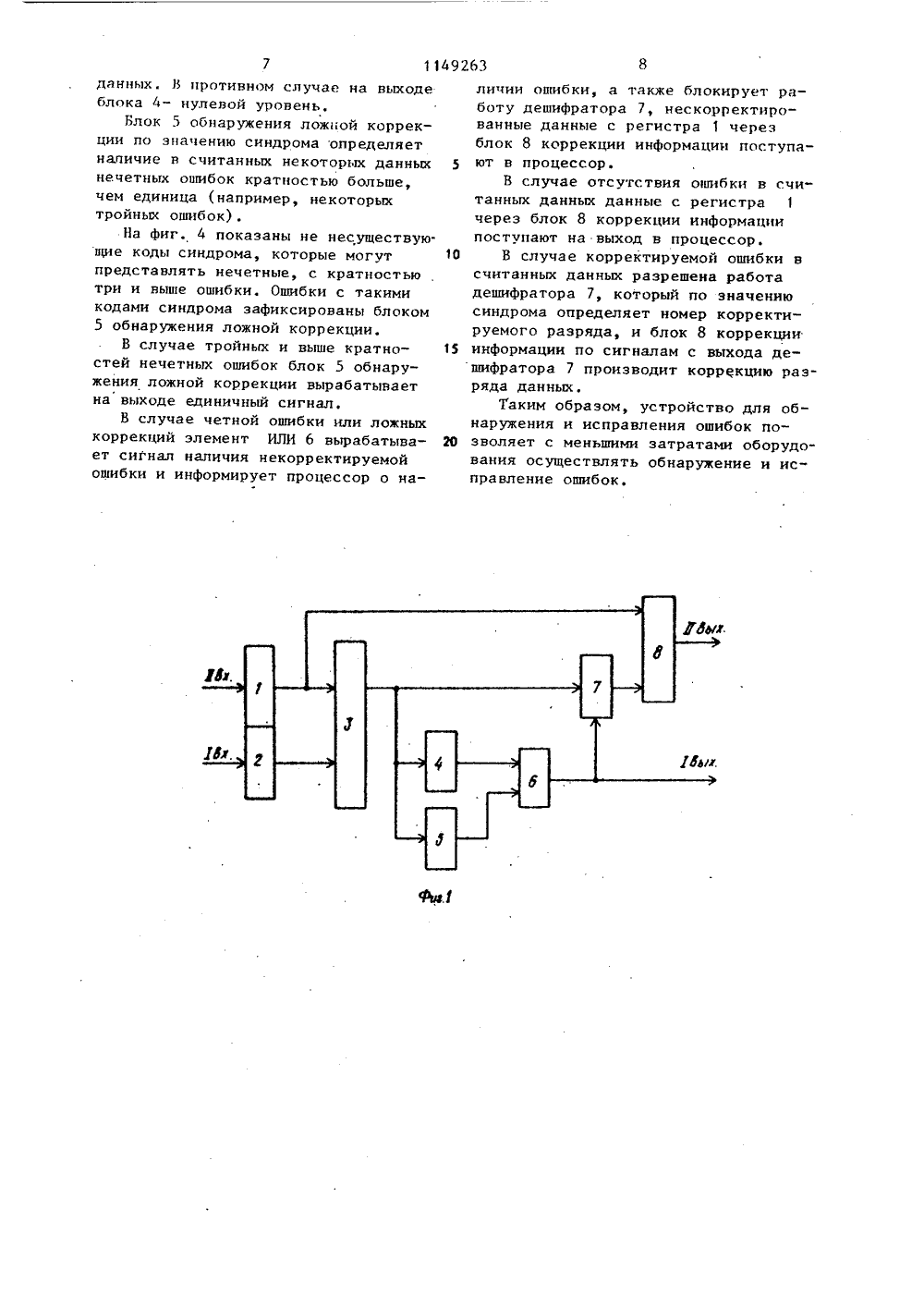

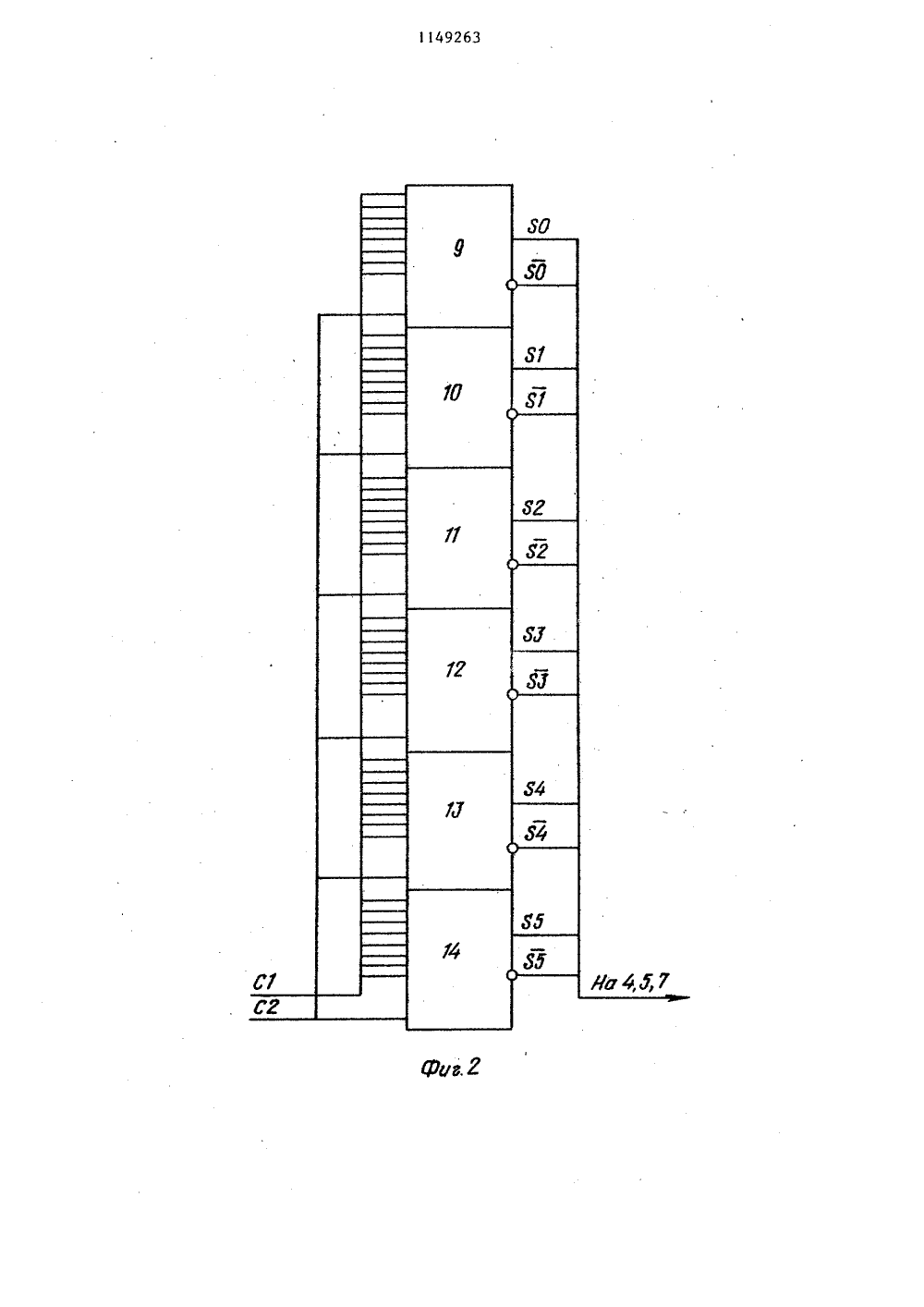

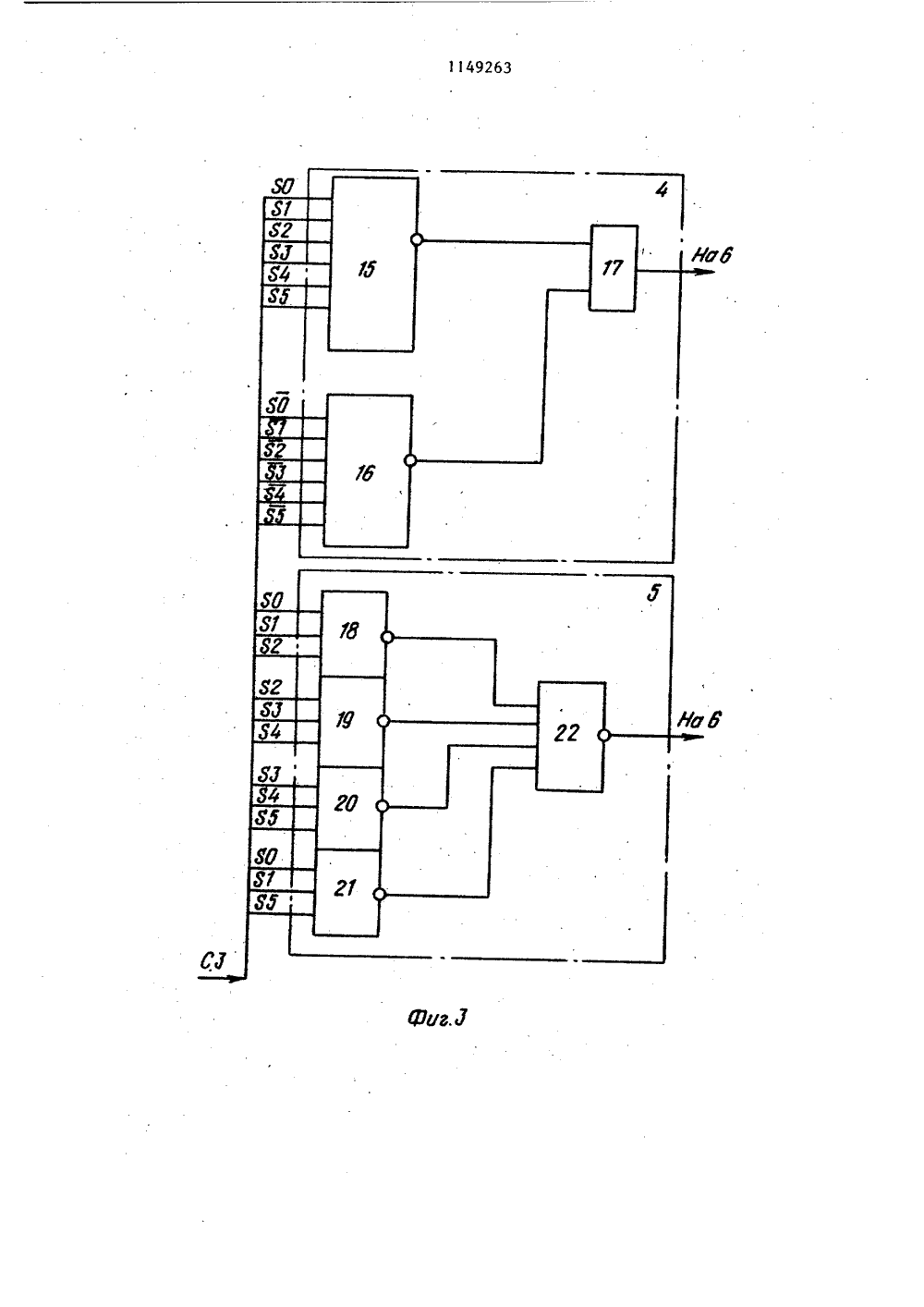

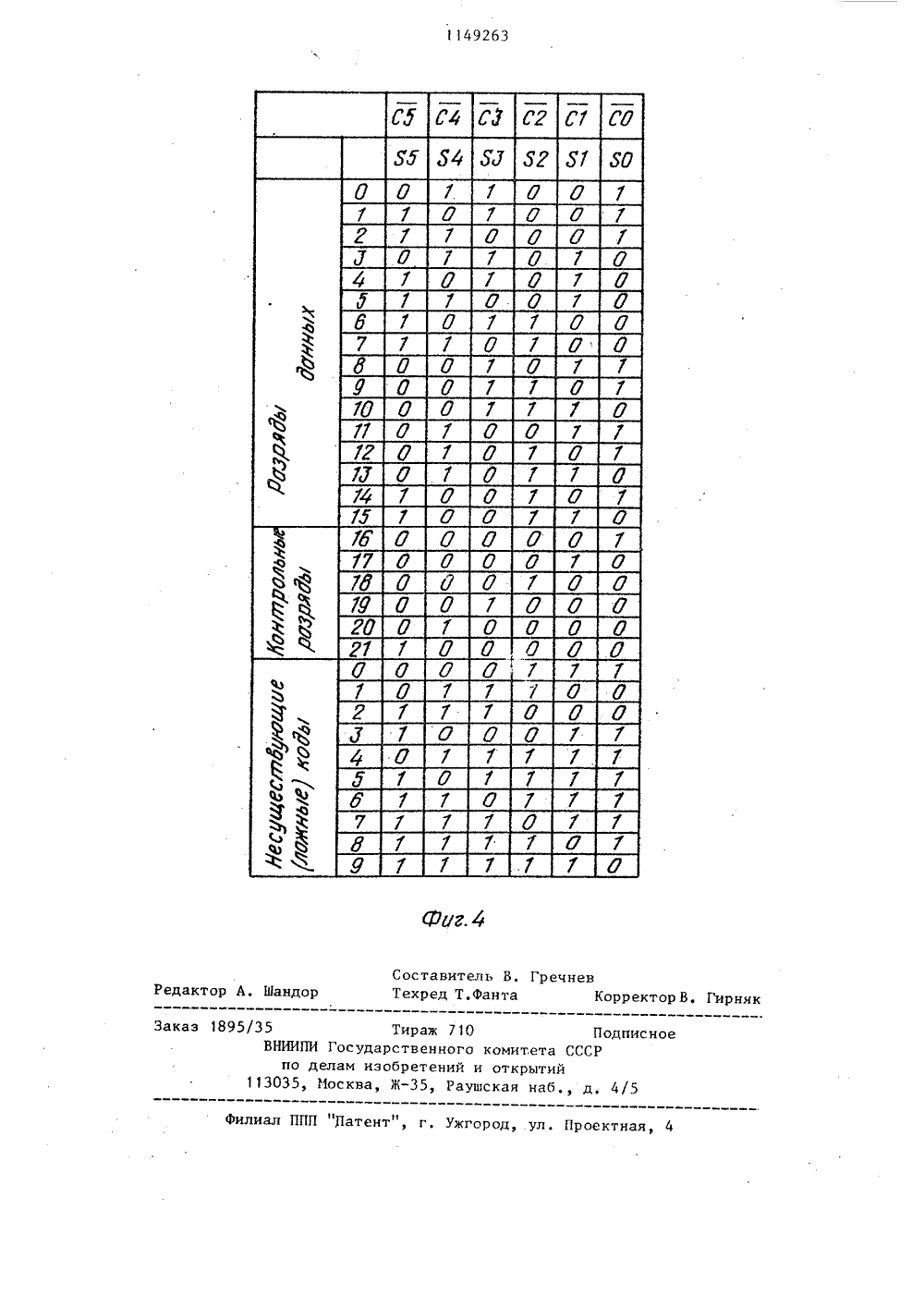

го, над ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ(71) Киевский ордена Трудовоного Знамени завод электроннлительных и управляющих маши(54) (57) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯИ ИСПРАВЛЕНИЯ ОШИБОК, содержащееинформационный и контрольный регистры, дешифратор и блок коррекции информации, причем информационные входы информационного и контрольногорегистров являются соответственноинформационными входами и входамиконтрольных разрядов устройства, выходы информационного регистра соединены с группой информационных входов блока коррекции информации, группа корректирующих входов которогосоединена с выходами дешифратора,выход блока коррекции информацииявляется информационным выходом устройства, о т л и ч а ю щ е е с ятем, что, с целью уменьшения оборудования, оно содержит формировательсиндрома, содержащий шесть узловсвертки по модулю два, блок обнаружения четного числа ошибок, содержащий сумматор по модулю два, элемент И-НЕ и элемент И, причем входыэлемента И соединены соответственнос инверсным выходом сумматора по модулю два и выходом элемента И-НЕ,блок обнаружения ложной коррекции,содержащий пять элементов И-НЕ, причем выходы первого, второго, третьего и четвертого элементов И-НЕ соединены с соответствующими входамипятого элемента И-НЕ, и элемент ИЛИ,причем входы первого узла свертки помодулю два формирователя синдромасоединены соответственно с выходаминулевого, первого, второго, восьмогодевятого, одиннадцатого, двенадцатого и четырнадцатого разрядов информационного регистра и выходом нулевого разряда контрольного регистраФ двходы второго узла свертки по модулю два формирователя синдрома соединены соответственно с выходами третьего, четвертого, пятого, восьмого,десятого, одиннадцатого, тринадцатого и пятнадцатого разрядов инфор- Ямационного регистра и выходом первого разряда контрольного регистра,входы третьего узла свертки по модулю два формирователя синдрома соединены соответственно с выходами шестоседьмого, девятого, десятого,двецатого, тринадцатого, четырнадцатого и пятнадцатого разрядов информационного регистра и выходом второгоразряда контрольного регистра, входычетвертого узла свертки по модулюдва формирователя синдрома соединенысоответственно с выходами нулевого, фьпервого, третьего, четвертого, шестого, восьмого, девятого и десятогоразрядов информационного регистра ивыходом третьего разряда контрольногорегистра, входы пятого узла сверткипо модулю два формирователя синдромасоединены соответственно с выходами1149263 нулевого, второго, третьего, пятого, седьмого, одиннадцатого, двенадцатого и тринадцатого разрядов инфор.мационного регистра и выходом четвертого разряда контрольного регистра, входы шестого узла свертки по модулю два формирователя синдрома соединены с выходами первого, второго, четвертого, пятого, шестого, седьмого, четырнадцатого и пятнадцатого разрядов информационного регистра и выходом пятого разряда контрольного регистра, входы сумматора по модулю два блока обнаружения четного числа ошибок соединены с прямыми выходами всех узлов свертки по модулю два формирователя синдрома, входы элемента И-НЕ блока обнаружения четного числа. ошибок соединены с инверсными выходами всех узлов свертки по модулю два формирова.теля синдрома, входы первого элемента И-НЕ блока обнаружения ложной коррекции соединены соответственно с прямыми выходами первого, второго и тре- тьего узлов свертки по модулю два формирователя синдрома, входы втоИзобретение относится к вычислительной технике и может найтипримене-,ние в вычислительных системах, осуществляющих схемный контроль считанных данных, 5Известно устройство для обнаружения и исправления ошибок, содержащее последовательно соединенные регистр приема информационных разрядов, блок, свертки и блок сравнения,0второй вход которого соединен с выходом регистра приема проверочныхразрядов и с первым входом блокакоррекции проверочных разрядов,второй вход которого соединен с выходом дешифратора кода номера корректируемого разряда и первым входомблока коррекции информационных разрядов, второй вход которого соединенс входом блока свертки и с входом 20формирователя контрольного разрядабайта, выход которого соединен с первым входом блока коррекции контрольного разряда датчика 1 . рого элемента И-НЕ блока обнаруженияложной коррекции соединены соответственно с прямыми выходами третьего,четвертого и пятого узлов сверткипо модулю два формирователя синдрома, входы третьего элемента И-НЕ блока обнаружения ложной коррекции соединены соответственно с прямыми выходами четвертого, пятого и шестогоузлов свертки по модулю два, входычетвертого элемента И-НЕ блока обнаружения ложной коррекции соединенысоответственно с прямыми выходамипервого, второго и шестого узловсвертки по модулю два формирователя синдрома, выходы элемента И и пятого элемента И-НЕ блока обнаружения ложной коррекции соединены с соответствующими входами элемента ИЛИ, выход которого является выходомнеисправнос.и устройства и соединенс управляющим входом дешифратора, информационные входы которого соединены с прямыми выходами всех узловсвертки по модулю два формирователясиндрома. Недостатками. этого устройства являются низкая вероятность обнаружения ошибки, сложность устройства, большой объем оборудования.Наиболее близким по технической сущности к предлагаемому является устройство для обнаружения,и исправления ошибок, содержащее регистр приема информационных разрядов, блок сверт- ки, блок сравнения, регистр приема проверочных разрядов, блок коррекции проверочных разрядов, дешифратор кода номера корректируемого разряда, блок коррекции информационных разрядов, формирователь контрольного разряда байта, блок коррекции контрольного разряда байта, дешифратор кода номера байта, дешифратор кода номера разряда в байте, причем выход регистра приема имформационных разрядов сое" динен с входом блока свертки, первым входом блока коррекции информационных разрядов и через формирова- . тель контрольного разряда байта спервым входом блока коррекции контрольного разряда байта, выход которого является выходом контрольного разряда байта устройства, выход блокасвертки соединен с первым входом 5блока сравнения, выход которого соединен с входами дешифратора кода номера байта и дешифратора кода номераразряда в байте, выходы которых соединены с соответствующими входами де Ошифратора кода номера корректируемогоразряда, выход которого соединен с первым входом блока коррекции проверочных разрядов и вторым входом блокакоррекции информационных разрядов, 15выход которого является информационным выходом устройства, выход регистра приема проверочных разрядов соединен с вторым входом. блока сравнения.и вторым входом блока коррекции проверочных разрядов, выход которогоявляется выходом проверочных разрядов устройства, выход дешифраторакода номера разрядов в байте соединенс вторым входом блока коррекции контрольного разряда байта 2 .Недостатками известного устройстваявляются сложность устройства и большой объем оборудования.Цель изобретения - уменьшение обо- Зпрудования,Поставленная цель достигается тем,что устройство для обнаружения и исправления ошибок, содержащее информационный иконтрольный регистры, дешиф- З 5ратор и блок коррекции информации,причем информационные входы информационного и контрольного регистровявляются соответственно информационными входами и входами контрольных 40, разрядов устройства, выходы информационного регистра соединены с группой информационных входов блока коррекции информации, группа корректиру.ющих входов которого соединена с выходами дешифратора, выход блока кор-.рекции информации является информационным выходом устройства, содержит формирователь синдрома, содержащий шесть узлов свертки по модулю 50два, блок обнаружения четного числаошибок, содержащий сумматор по модулю два, элемент И-НЕ и элемент И,причем входы элемента И соединенысоответственно с инверсным выходом 55сумматора по модулю два и выходомэлемента И-НЕ, блок обнаружения ложной коррекции, содержащий пять влементов И-НЕ, причем выходы первого, второго, третьего и четвертого элементов И-НЕ, соединены с соответствующими входами пятого элемента И-НЕ, и элемент ИЛИ, причем входы первого узла свертки по модулю два формирователя синдрома соединены соответственно с выходами нулевого, первого, второго, восьмого, девятого, одиннадцатого, двенадцатого и четырнадцатого разрядов информационного регистра и выходом нулевого разряда контрольного регистра, входы второго узла свертки по модулю два.формирователя синдрома соединены соответственно с выходами третьего, четвертого, пятого, восьмого, десятого, одиннадцатого, тринадцатого и пятнадцатого разрядов информационного регистра и выходом первого разряда контрольного регистра, входы третьего узла свертки по модулю два формирователя синдрома соединены соответственно с выходами шестого, седьмого, девятого, десятого, двенадцатого, тринадцатого, четырнадцатого и пятнадцатого разрядов информационного регистра и выходом второго разряда контрольного регистра, входы четвертого узла свертки по модулю два формирователя синдрома соединены соответственно с выходами нулевого, первого, третьего, четвертого, шестого, восьмого,девятого и десятого разрядов информационного регистра и выходом третьего разряда контрольного регистра,входы пятого узла свертки по модулюдва формирователя синдрома соединены соответственно с выходами нулевого, второго, третьего, пятого, седьмого, одиннадцатого, двенадцатого,и тринадцатого разрядов информацнон"ного регистра к выходом четвертогоразряда контрольного регистра, входы шестого узла свертки по модулю дваформирователя синдрома соединены соответственно с выходами первого, второго, четвертого, пятого, шестого, седьмого, четырнадцатого и пятнадцатого разрядов информационного регистра и выходом пятого разряда контрольного регистра, входы сумматорапо модулю два блока обнаружения четного числа ошибок соединены с прямыми выходами всех узлов свертки по мо.дулю два формирователя синдрома, вхо.ды элемента И-НЕ блока обнаружения четного числа ошибок соединены с ин 1149263версными выходами всех узлов свертки по модулю два Формирователя синдро - ма, входы первого элемента И-НЕ бло-, ка обнаружения ложной коррекции соединены соответственно с прямыми выходами первого, второго и третьего узлов свертки по модулю два Формирователя синдрома, входы второго элемента И-НЕ блока обнаружения ложной коррекции соединены соответствен О но с прямыми выходами третьего, четвертого и пятого узлов свертки по модулю два формирователя синдрома, входы третьего элемента И - НЕ блока обнаружения ложной коррекции соедине ны соответственно с прямыми выходами четвертого, пятого и шестого узлов свер-, тки по модулю два, входы четвертого элемента И-НЕ блока обнаружения ложной коррекции соединены соответствен но с прямыми выходами первого, второго и шестого узлов свертки по модулю два фор рователя синдрома, выходы элемента И и пятого элемента И-НЕ блока обнаружения ложной коррекции соединены с соответствующими входами элемента ИЛИ, выход которого является выходом неисправности устройства и соединен с управляющим входом дешифратора, информационные входы которого ЗО соединены с прямыми выходами всех узлов свертки по модулю два формирователя синдрома.На фиг, 1 приведена структурная схема устройства для обнаружения и д исправления ошибок; на Фиг. 2 - функциональная схема формирователя синдрома; на Фиг. 3 - функциональные схемы блока обнаружения четного числа ошибок и блока обнаружения ложной коррекции;40 на Фиг. 4 - таблица формирования разрядов контрольных сумм (СО-С 5) и разрядов синдрома (БО-Б 5) для случаев коррекции в информационном или контрольном разряде, а также при обнару жении ложных коррекций.Устройство для обнаружения и исправления ошибок (фиг. 1) содержит информационный и контрольный регистры 1 и 2, формирователь 3 синдрома, БО блок 4 обнаружения четного числа ошибок, блок 5 обнаружения ложной коррекции, элемент ИЛИ 6, дешифратор 7, блок 8 коррекции информации, Формирователь 3 синдрома (фиг. 2) содержит узлы 9-14 свертки по модулю два. Блок 4 обнаружения четного числа ошибок (фиг. 3) содержит сумматор 15 по модулю два, элемент И-НЕ 16 и элементИ 17, Блок 5 обнаружения ложной коррекции (фиг. 3) содержит элементы И-НЕ18-22.Устройство для обнаружения и исправления ошибок работает следующим образом.При операциях чтения информация(например, из памяти) заносится в регистр 1 в виде информационных и контрольных разрядов в регистр 2. Формирователь 3 синдрома по значениям информационных и контрольных разрядов,поступивших с регистров 1 и 2, проводит Формирование контрольных разрядов путем свертки информации, посту.пающей с регистра 1 (например, по коду Хэмминга), и сравнение результатас контрольными разрядами регистра 2.Формирователь 3 синдрома позволяетв одной ступени организовать свертку и сравнение.Можно рассмотреть (фиг, 4), какпроисходит формирование контрольныхразрядов кода Хэмминга (СОС 5), исходя из конкретного случая 16-ти разрядов данных информационного слова.Так, нулевой разряд данных информационного слова входит в нулевую,третью и четвертую контрольные суммыКаждый разряд данных информационного -лова входит в три контрольныесуммь; каждая контрольная сумма состоит из восьми разрядов данных инФормационного слова. Аналогично происходит формирование каждого разрядасиндрома (БОЯ 5), но в отличие отформирования контрольной суммы в формирование разряда синдрома входитпарафазный код соответствующего контрольного разряда.Дешифратор 7 по значению синдромапоступившего с формирователя 3 син-.дрома, определяет в случае одиночнойошибки, номер разряда данных в информационном слове, который подлежит коррекции,Элемент И-НЕ 16 блока 4 обнаружения четного числа ошибок (фиг. 3) по значению синдрома определяет наличие ошибки в считанных данных, а сумматор 15 по модулю два определяет наличие в считанных данных четной (например, двойной) ошибки.Единичный сигнал на выходе блока 4 информирует о наличии четной (например, двойной) ошибки в считанныхданных. В противном случае на выходе блока 4- нулевой уровень.Блок 5 обнаружения ложной коррекции по значению синдрома определяет наличие в считанных некоторых данных нечетных ошибок кратностью больше, чем единица (например, некоторых тройных ошибок).На фиг. 4 показаны не несуществую. щие коды синдрома, которые могут представлять нечетные, с кратностью три и выше ошибки. Ошибки с такими кодами синдрома зафиксированы блоком 5 обнаружения ложной коррекции.В случае тройных и выше кратностей нечетных ошибок блок 5 обнаружения ложной коррекции вырабатывает на выходе единичный сигнал.В случае четной ошибки или ложных коррекций элемент ИЛИ 6 вырабатывает сигнал наличия некорректируемой ошибки и информирует процессор о наличии ошибки, а также блокирует работу дешифратора 7, нескорректированные данные с регистра 1 черезблок 8 коррекции информации поступают в процессорВ случае отсутствия ошибки в считанных данных данные с регистра 1через блок 8 коррекции информациипоступают на выход в процессор.10 В случае корректируемой ошибки всчитанных данных разрешена работадешифратора 7, который по значениюсиндрома определяет номер корректируемого разряда, и блок 8 коррекции 15 информации по сигналам с выхода дешифратора 7 производит коррЕкцию разряда данныхГаким образом, устройство для обнаружения и исправления ошибок по зволяет с меньшими затратами оборудования осуществлять обнаружение и исправление ошибок,149263 оставитель В. Гречнехред Т.фанта Редактор А, Шандор Корректо ирня Заказ 1895/ одписное Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 ВНИИПИ Госуда по делам из13035, Москва,ираж 71твенногретений-35, Раук омитета СССРоткрытий кая наб д. 4/

СмотретьЗаявка

3521956, 09.12.1982

КИЕВСКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ЗАВОД ЭЛЕКТРОННЫХ ВЫЧИСЛИТЕЛЬНЫХ И УПРАВЛЯЮЩИХ МАШИН

БЕЛАЛОВ ЕВГЕНИЙ ЯКОВЛЕВИЧ, РУДАКОВ ЭДУАРД ВЛАДИМИРОВИЧ, САЛАМАТОВ СЕРГЕЙ ПЕТРОВИЧ, ЧАЛЧИНСКИЙ ИВАН АНТОНОВИЧ

МПК / Метки

МПК: G06F 11/08

Метки: исправления, обнаружения, ошибок

Опубликовано: 07.04.1985

Код ссылки

<a href="https://patents.su/8-1149263-ustrojjstvo-dlya-obnaruzheniya-i-ispravleniya-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обнаружения и исправления ошибок</a>

Предыдущий патент: Устройство для контроля -кодов фибоначчи

Следующий патент: Адаптивное резервированное устройство

Случайный патент: Устройство автоматического торможения реверсивного стана холодной прокатки