Процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 557366

Авторы: Заславский, Нефедченко, Стоенко, Фиалко, Харитонов, Шередин

Текст

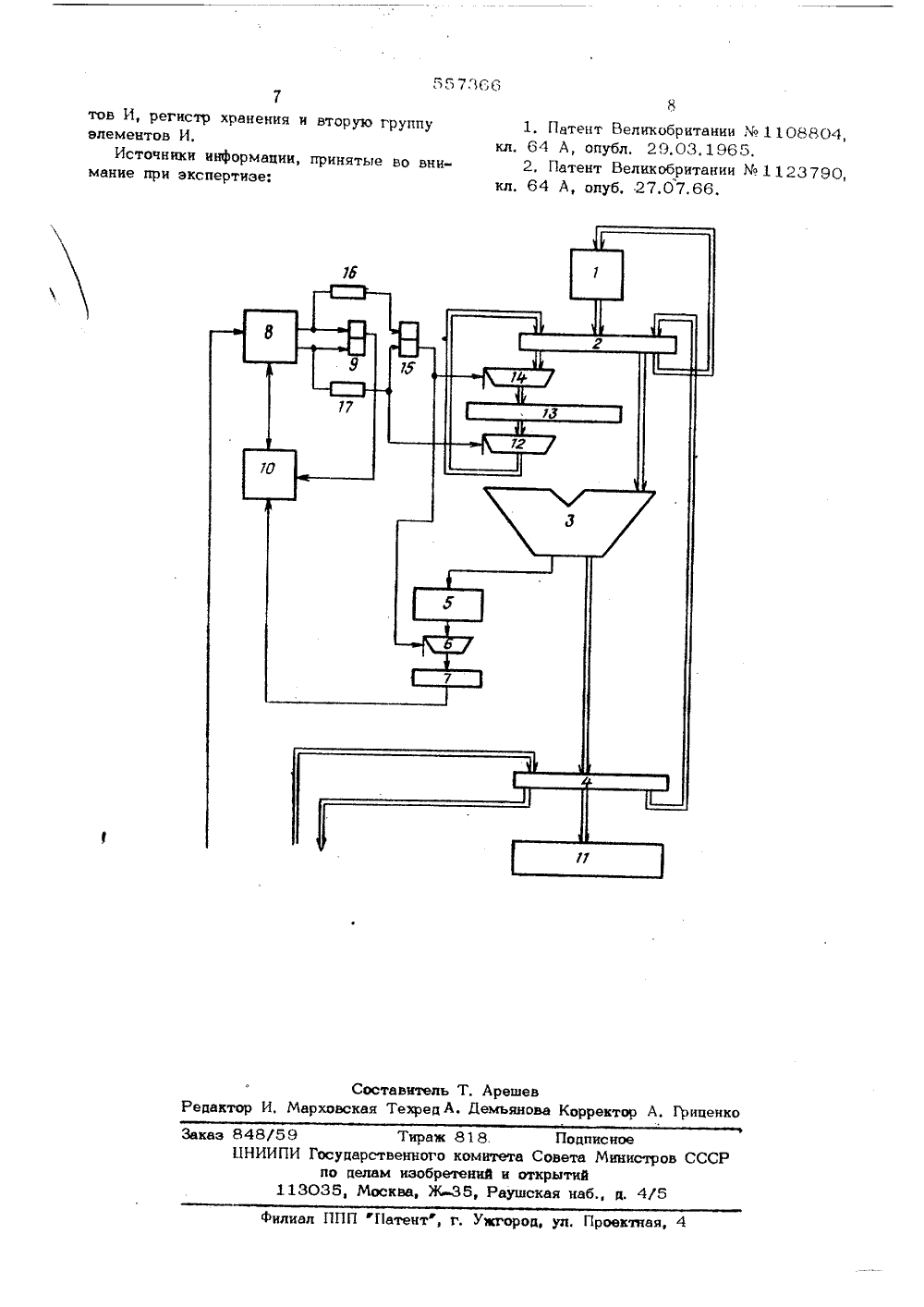

СП ИСАНИЕИЗОБРЕТЕН ИЯК А 61 ОР СКОМУ СВИДЕТЕЛЬСТВУ Союз Советскик Социалистические Республик(22) Заявлено 08.12. 74 (21) 2082196/24 51) М, Кл,т 506 Р 15/00 присоединением заявки Яасудврственный комитетСовете Иннистров СССРпо делам изобретенийи открытий 3) Приоритет -еиь %1(43) Опубликовано 05,05. 77,Бюлл (45) Пата опубликования описаии К 681.3 (088,8(72) Л вторы изобретения Киевский ордена Трудового Красного Знаменизавод электронных вычислительных и управляюших машин(71) Заявите 4) ПРОЦЕССОР 1Изобретение относится к вычислительной технике и может быть использовано при кон. струироввнии процессоров, оборудование которых используется для передачи данных между каналами ввода-вывода и главной па мятью,Известен процессор, содержаший информационные регистры и каналы, первые выходы и входы которых подключены соответственно к входным и выходным информацион- Ю ным шинам главной памяти, а вторые выходы - к адресным шинам, которые через регистр адреса соединены с адресным входом главной памяти, информационные регистры соединены также двусторонней связью 5 с арифметическим блоком 111. Недостатком этого устройства является значительный расход оборудования, связанный с наличием адресных щин, а также аппаратуры для хранения и модификации адресов в каналах.Наиболее близким техническим решением является процессор, содержащий блек местной памяти, выход и вход котооо 1 о соедикены соответственно с первыми входом и выходом информационного регистра, второйвыход которого через .сумматор соединен спервым входом выходного регистра, первыйвыход которого соединен со вторым входоминформационного регистра, вторые вход ивыход выходного регистра соединены соответственно с первыми выходом и входомпроцессора, выходной регистр также соединен двусторонней связью с информационноймагистралью каналов, второй выход сумматора соединен через последовательно соединенный узел формирования признаков, пер.вую группу элементов И, регистр признаков с первым входом узла микропрограммного управления, второй вход которотосоединен с единичным выходом первоготриггера режима, единичный и нулевой входы которого соединены соответственно спервым и вторым выходами узла управлния микропрерываниями, вход которого соединен со вторым выходом процессора, у;илуправления микропрерываниями соединендвусторонней связью с узлом мякропротъпммного управления.55 т" 36 НЕДОСтат НОМ Н,ВЕС .тР, т :т. ОГ ЯВ ЛяЕтСя ПОтЕря МтщтНННОГО т.;.На НЕре -КЛЮЧЕПНЕ С т КН.т ттят.Гтнтт.ьттНЯ .ттаШНННт-тХкоманд на режнм ввода-вывода и в обрагном направлен 1 тя, Эта потеря обусловлена 5, использованием местной памяти для сохранения содержимого инфэрмационпого регистра.эЦелью изобретения является ловышениебыстродействия процессора за счет исклкь- Очения потерь машинного времени при переключении режимов,Поставленная цель дОСтИГается тем, чтоустройство доттолнительно содержит двегруппы элементов И, регистр хранения, два Иэлемента задержки и второй триггер рекиМа, ЕДИНИЧНЬтй Н НУЛЕВОЙ ВХОДЫ КотОРОГОчерез элементы задержки соединены соотВЕтСтВЕННО С ПэрВЫМ И ВтОрЫМ Втт.ХОПаМНуЗЛа утПЭОВтЕННтт МтКГтонтртэрЫОаНГяМИ НУЛЕВой ВХОД ВтОРОгтРИтЧ"ЕРа РЕжИМа СОЕДИнен с управляющим входом второй группыэлементов И, а нулевой выход - с управЛЯиЩИМИ ВХОдтжтн НЕРВОй и тРЕтЬЕй ГРУППЭЛЕМЕНТОВ И, трат.Н ВЫХОД Н ВХОД тттн 5 эр- ймационного регистра соединены через поСлйтттттттттй тт тттт ттчтт 1 тоттт-тт. тттст рЭтКттть.то 1 т,т. т т .,Р ЛРт.Н тттнт Н ВТОРУигруппу элемтентов И,На чертеже изображена блэк-схема прэ- ЭОПЕОСтт т1 роцессор содержит блок 1 местной памяти, информациоь-.щй регистр 2, суммат.,".;, : тдтттетт рЕГцотр 4 уЗЕП 5 фОГтМ 1 т.-рования признаков, первая группа элементов И 6, регистр 7 признаков, узел. 8 упраВЛЕНИЯ МНК.ОГГ)эттнтттнятттт;ттт тртГГГ О 9 ОЕ .кит дат, -,т,тдания, содержашнй память микрокоманд, регистр адреса, регистр микрокоманды с де ОШнфРатОРОМ МНКГтООПЕРгцтнйт ИНфОРМаЦНОННаЯмагистраль 11 каналов, вторая группа элементов И 12, регистр 13 хранения, третьягруппа элементов И 14, второй трптер режима 15, элементы 16,17 задержки. 4Устройство работает следующим Образом,В режиме выполнения машинных команд(режим процессора) триггеры 9 и 15 находятся в нулевом состоянии, снггалы на фОих входах отсутстьуют, Из блока 1 информация считывается в информационные регистры 2 (на чертеже показан Один из трехрет истров), Содержимое информационногорегистра 2 передается на входы сумматора 3, рЕЗуЛЬтат ОГЕрацИИ КОторОГО ПОМЕщается в регистр 4. Из последНего информация поступэгт н главную память процессора или (и) в один из информационных регистров 2. Из информационного ретистра 2 64Она за.,нстчмется в блок 1 или (и) переда: . на вход сумматора 3,В каждом цикле содержимое регистра 2переписывается в регистр 13. ПередачаОСУЩЕСтВЛЯЕтСЯ ЧЕРЕЗ тРЕтЬЮ ГРУППУ ЭЛЕментов И 14, на управляющем входе оторой действует разрешающий потенциал снулевого выхода триггера 15. Этот же дотенциал поддерживает в открытом состояниипервую группу элементов И 6, через кото.рую признаки, формируемые узлом 5, передаются д регистр 7, где они запоминаются,Содержнмое регистра 7 служит условиемветвлений для микропрограмм процессора.Одновременно с выполнением микропрограммы процессора происходит побайтнаяпередача данных между каналами ввода-вывода и внешними устройствами, Если выполняется операция чтения, данные принимаются из внешнего устройства и накапливаются в канале. Если выполняется операция записи, данные из канала передаютсяво внешнее устройство, Обмен данными меж.ДУ КаяаттаМН Н ВНЕШНИМИ УСтРОЙСтВаМИ ВЫнэтпть;те:с., Лчттономнэ без использованиямикропрограммного управления.ЕОдта Чэ.тННКВЕт НЕОбХОдГЧтОГ тЬ В Обращении к главной памяти, каналы вырабатывают запросы на микропрерывание, посту-.пающие на вход узла 8, Последний выделя; наиболее приоритетный из одновременно существующих запросов и вырабатываетпоследовательность сигналов, реализующуюпереключение на режим ввода-вывода. Если запрос принят узлом 8 в цикле вью полнения мнкрокоманды процессора с номе 1, н слдующем цикле вьитолнение микрокоманды Ъ+ 1 совмещается с переключением на режим ввода-вывода: в узле 10 сохраняется адрес очередной микроко- манды процессора (Л, +2), формируется ад- РЕГ Гтэтнтэй НКРОКОМаНДЫ ВВОДа-ВЫВОДа И счнтывается эта микрокоманда; триггер 9 устанавливается в единичное состояние.Снгтал на единичном входе триггера 9, задержанный элементом 16, переклточает и едгнтнчное состояние второй триггер 15, в РЕЗУЛЬттзтЕ ЧЕГО ЗаПИРаЮтСЯ ПЕРВаЯ И тРЕ- г 1 я гругнпт элементов И 6 и 14 и тем самым запрещается запись и регистры 7 и 13. Задержка, Формируемая элементом 16 подобрана таки.л Образом, что триггер 15 устананлнвается в единичное состояние, этим эбестчт.чивдется сохранение в регистсрах 13 и 7 именно той информации, которая бЫЛа СФОтынрооака В рЕГИСтрЕ 2 И уэле 5 в конце цикла выполнения микрокоманды г 1 +1 - последней микрокоманды процессора, выполнявшейся перед микоопре5 5 766 Ь 9 3 рыванием. (Элементы 16 и 17 могут быть реализованы, например, в виде сдвиговых регистров).Вслед за микрокомандой процессора Ъ +1 выполняется первая микрокоманда микропрограммы ввода-вывода. Эта микропрограмма осуществляет обращение к главной памяти дпя передачи данных в канал или иэ него. Адрес данных считывается из блока 1 в регистр 2 и затем передается в сумматор 3, где к нему прибавляется "4", если обмен с главной памятью четырехбайтовый. Обновленный адрес поступает в регистр 4, затем в регистр 2 и записывается в блок 1. Он же с регистра 4 передается в главную память. По этому адресу пооисходит передача данных между главной памятью и каналом; если выполняется операция чтения,данные через информапионную магистраль 11 каналов и регистр 4 записываются в главную память, Если выполняется операция записи, данные считываются иэ главной памяти и через регистр 4 и информа- йЬ ционную магистраль 11 передаются в канал. На выполнение микропрограммы канала требуется т циклов. Если в цикле считыва- О ния микрокоманды тп отсутствуют запросы от каналов, ожидающие обслуживания, происходит возврат на микропрограмму процессора. Если микрокоманда тп не использует регистр 2, цикл возврата совмещается сЬЬ циклом выполнения микрокоманды ттт, Во время этого цикла: в узле 10 считывается очередная микрокоманда процессора ( т 1 +2) а триггер 9 сбрасывается в нул евое состояние,Сигнал на нулевом входе триггера 9, задержанный элементом 17, открывает вт рую группу элементов И 12, разрешая передачу в регистр 2 из регистра 13, и сбрасывает в нулевое состояние триттера . 15. Величина задержки, формируемой элементом 17, подобрана такой, чтобы восстановление информации в регистре 2 сброс ЬО триггера 15 происходили на однэм синхроимпульсе цикла выполнения госледней микрокоманды ввода-вывода. В результате к моменту возобновления работы микропрограммы процессора содержимое регистров 2,7 и состояние схем оказываются такими же, как если бы микропрерывания не было.За циклом выполнения тп -й микрокоман ды ввода-вывода следует плкл выполнения ( тт +2) -ой микрокоманды процессора, и ЬО таким образом возобновляется работа микропрограммы процессора.таким образом в предложенном процессоре переключение режимов совмещено во времени с выполнением микрокоманд. Благодарк этому на каждое обращение к главной памяти со стороны каналов процессор затрачивает равно столько машинных циклов, сколько необходимо для вьптолнения микропрограммы ввода-вывода, В резуль тате на каждом таком обращении экономится два машинных цикла, что приводит к существенному повышению производительно".ти пооцессора. формула изобретения Процессор, содержащий блок местной памяти, выход и вход которого соединены сооветственно с первыми входом и выходоминформационного регистра, второй выход которого через сумматор соединен с первымвходом выходного регистра, первьгй выходкоторого соединен со вторым входом информационного регистра, вторые вход и выход выходного регистра соединены соответственно с первыми выходом и входом процессора, выходной регистр также соединен двусторонней связью с информационной магистралью каналов, второй выход сумматора соединен через последовательно соединенный узел формирования признаков, первую группу элементов И, регистр признаков с первым входом узла микропрограммного управления, второй вход которого соединен с единичным выходом первого триггера режима, единичный и нулевой входы которого соединены соот:;,твенно с первы.1 я вторым выходами узла управления микропрерываниями, вход которого соединен со вторым выходом процессора, узел управления микропрерываниями соединен двусторонней связью с узлом микропрограммного управления, о т - л и ч а ю щ и й с я тем, что, с целью повышения быстродействия процессора, он дополнительно содержит две группы элементов И, регистр хранения, два элемента задержки и второй тритгер режима, единичный и нулевой входы которого через элементы задержки соединены соответственно с первым и вторым выходами узла управления микропрерываниями нулевой вход второго триггера режима соединен с управляющим входом второй группы элементов И, а нулевой выход - с управляющими входами первой и. третьей групп элементов И, третьи выход и вход информационного регистра соединены через последовательно соединенные третью группу элемен557366 7тов И, регистр хранения и вторую группу элементов И.Источники информации, принятые во внимание при экспертизе: Составитель Т. Арешевдактор И. Марховская ТехредА. Йемьянова Корректор А. фипен Тираж 818. Подписноеарсгвенного комитета Совета Министров ССелам изобретений и открытийМосква, Ж 35, Раушская наб., д. 4/5 филиал ППППатент, г. Ужгород, уп. Проектная,Заказ 848/59 ИНИИПИ Гос по 11303

СмотретьЗаявка

2082196, 08.12.1974

КИЕВСКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ЗАВОД ЭЛЕКТРОННЫХ ВЫЧИСЛИТЕЛЬНЫХ И УПРАВЛЯЮЩИХ МАШИН

ЗАСЛАВСКИЙ РЕМА ИОСИФОВИЧ, НЕФЕДЧЕНКО БОРИС ПАВЛОВИЧ, СТОЕНКО ДАВИД ЯКОВЛЕВИЧ, ФИАЛКО ЛЮБОВЬ ИЛЬИНИЧНА, ХАРИТОНОВ ВАСИЛИЙ НАУМОВИЧ, ШЕРЕДИН АЛЕКСАНДР ПЕТРОВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: процессор

Опубликовано: 05.05.1977

Код ссылки

<a href="https://patents.su/4-557366-processor.html" target="_blank" rel="follow" title="База патентов СССР">Процессор</a>

Предыдущий патент: Устройство для коррекции базовых регистров

Следующий патент: Система дублированных цифровых вычислительных машин (цвм)

Случайный патент: Разжигатель цементного сырьевого шлама