Система коммутации процессоров

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

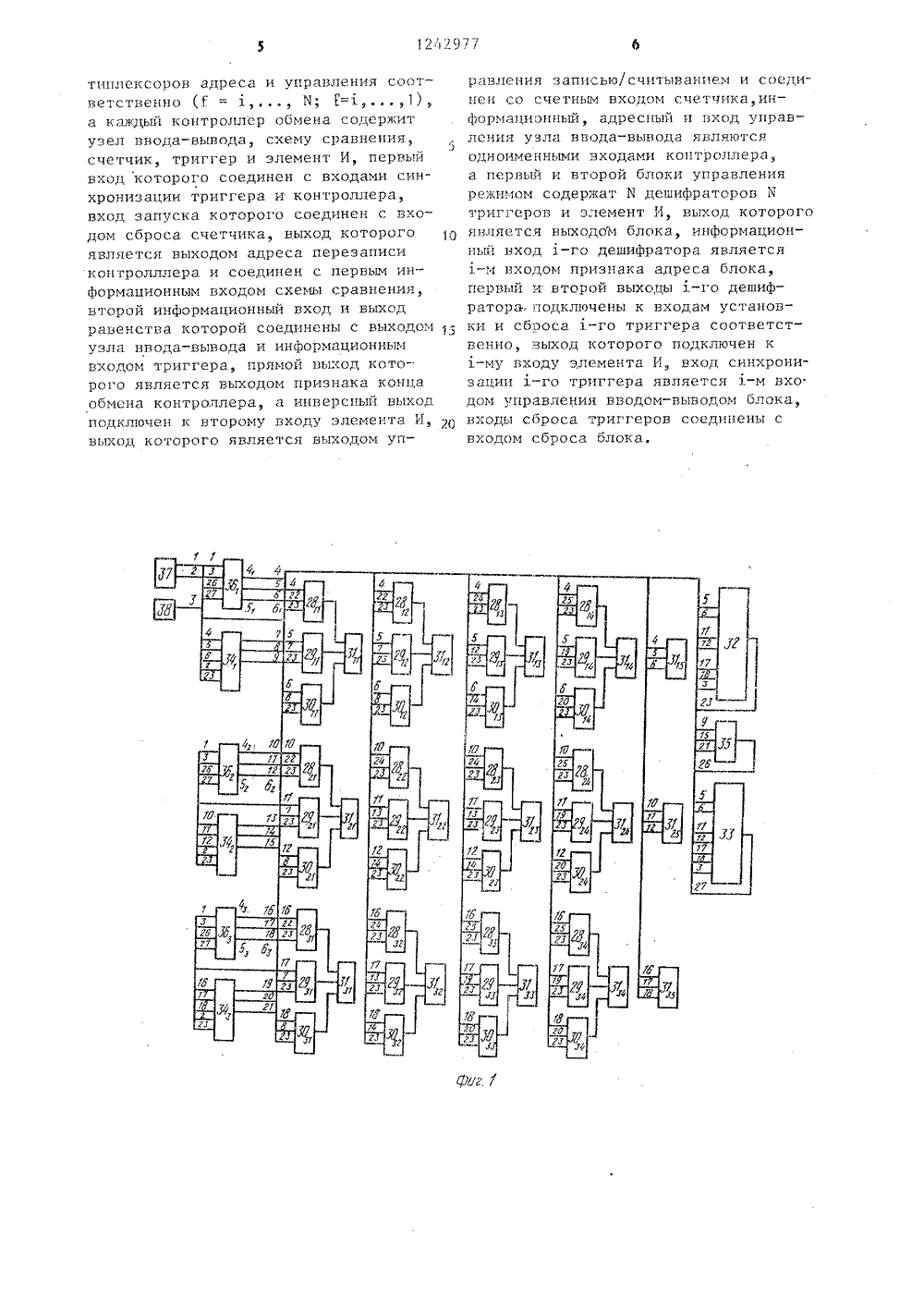

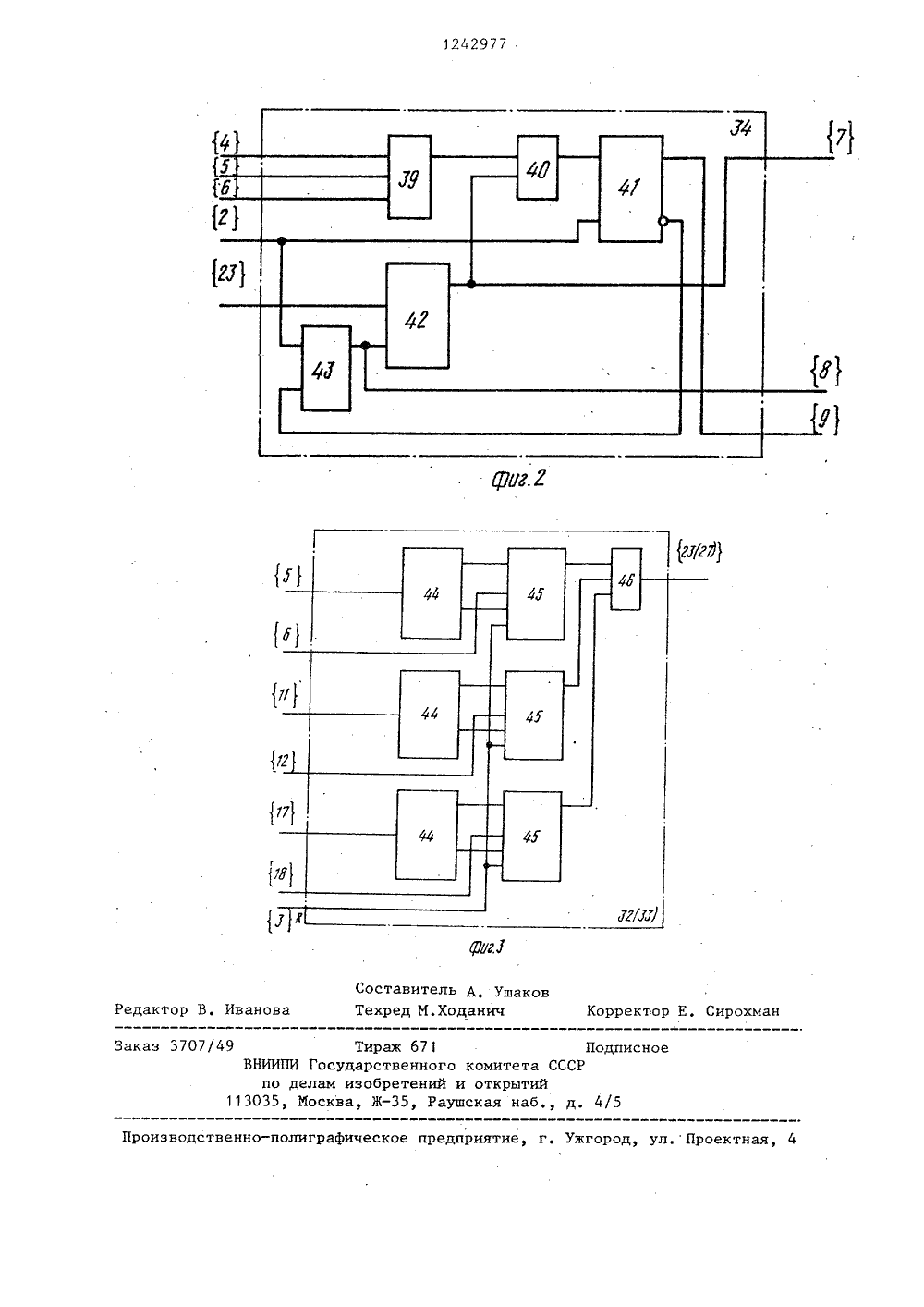

(50 4 С 06 Р 15/1 ДПИСАНИЕ ИЗОБРЕТЕН бмена ме их затра Р Н.Нкоммутато подключаемьматрицу И,и управленоперативно вые интегральное пособие Под ред,зд., перераб.зь, 1985,блоки управлени леров обмена, э контрол-,нкциониро.чередуюбмен, В режимом,мент И. Ф вание систе оисходит в абота" имы п11таи а щих ежим "Раб реж таю процессорытономно ирежиме "0иными междам данных оаллельно изадачи. 2 ешают осмен про- И процес новремен- втономное раллельн тво СССР 5/16, 1979.ПРОЦЕССОРОВ тся к вычислибыть исполь- эффективного ионную зада исходит обм сорами по И но, а также н шение онов ОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ К АВТОРСКОМУ СВИДЕТЕЛЬСТ(57) Изобретение откостельной технике и можезовано для организации я 13, 3ЬКБМво. у процессорами при небольх оборудования. Системасодержит матрицу И, И+1в данных, где И - числож к системе процессоров,И+1 мультиплексоров адресая, матрицу М, И+2 блоковпамяти, первый и второй1 124Изобретение относится к вычислительной технике и может быть использовано при разработке многопроцессорных систем, в частности мулътимикропроцессорных,Целью изобретения является сокращение затрат оборудования.На фиг, 1 представлена функциональная схема системы при 11 = 3,13; 3 = 15; на фиг,2функциональная схема контроллера обмена, соответствующего первому процессору системы, в Фигурных скобкахсохранены номера шин и проводниковжгута, приведенного на фиг. 1; нафиг. 3 - функциональная схема блоковуправления режимом,Вычислительная система, построенная с использованием предложеннойсистемы коммутации процессоров, содержит шину 1 синхронизации процессо.ров,шину 2 синхронизации системы, шину3 сброса системы, шины 4-6 данных,адреса управления первого процессора,шины 7-9 - адреса перезаписи управления записью/считыванием и конца обмена первого процессора, шины 10-15 второго процессора и 16-21 третьего процессора, которые имеют аналогичноеФункциональное назначение и названиесоответственно шинам 4-9 первого процессора, первую шину 22 обмена данных,шину 23 запуска обмена, вторую 24 итретью 25 шины обмена данных, первую26 и вторую шины 27 прерывания,а системакоммутации содержит матрицу И, И+1коммутаторов 28 данных, матрицумультиплексоров 29, адреса и 30,управления, матрицу И, И+2 блоков 31оперативной памяти, первый и второйблоки 32 и 33 управления режимов, Иконтроллеров обмена 34, , элементИ 35, К системе коммутации подключаются процессоры 36 а для обеспечения ее работы подключен общий синхрогенератор 37 и блок 38 сброса,Каждый контроллер 34 обмена содержит узел 39 ввода/вывода, схему 40сравнения, триггер 41, счетчик 42 иэлемент И 43. Каждый блок 32 (33) управления ре жимом содержит Б дешифраторов 44, 11 триггеров 45, элемент И 46,Система работает следующим образам.Все микроЭВИ, подключаемые к сис" теме коммутации, идентичны по структуре.2977 контролллеров 10 обмена, на вход считывания блоков 31," , из которых производится считывание данных, а навход записи блоков 31, в которыепроизводится запись данных. В функции контроллеров 10 обмена входит; а) Формирование адреса перезаписи(для всех блоков 31; ),",2Если сигнал на входах управления коммутаторов 28,; и мультиплексоров 29;, 30 назовем его "Обмен/работа" (О/Р),равен нулю,т,е, О/Р=О,то блоки 31,(где з. = 1, И; 1 = 1, М+ 1) подключены к внутренним шинам своих процессоров 36;. Так, например, информационные входы блоков 31,- 31через коммутаторы 28 - 28, подключены к шине 4 данных, адресные входы блоков 31-31 через мультиплексоры. 1,4.29 - 29,подключены к шине 5 адреса,входы управления записью (считыванием) блоков 31 - 31,4 через мультиплексоры 30- 304 подключены к шине 6 управления.При этом блоки 31 -31 образуют единый модуль оперативной памяти первого процессора, все ячейки которого доступны для адресации их первым процессором. В таком режиме производится .решение основной задачи параллельно тремя процессорами При О/Р = 1 блоки 31, отключаются от внутренних шин соответствующих процессоров, при этом возникает возможность для обмена данными между всеми процессорами одновременно, При реализации обмена блоки 314 не отключаются от внутренних шин своих 1. = х процессоров 36 (к таким относятся блоки 31 31 , 31 ), поэтому процессоры в режиме обмена сохраняют возможность решать Фоновую" задачу, В режиме обмена определенные блоки 31, через коммутаторы 28 и мультиплексо)ры 29 и 30," связываются между собой, образуя цепочки блоков 31; . Обмен разрешен только внутри определенной цепочки блоков 31, и только следующим образом: один блок 31, этой цепочки работает на считывание, остальные на запись, Например, в первой цепочке таким блоком является блок 31 . во второй 31, в третьей 31 . Такойрежим обмена в цепочках блоков 31;11 обеспечивается подачей синхроимпульсов, определяющих начало и длительность записи и считывания, которые формируются на выходах управления записью (считыванием) соответствующихкоммутатора данных и выходам Ц мультиплексоров адреса и управления соответственно, вход-выход данных -го процессора системы подключен ченез,-ю шину данных к вторым двунаправленным информационным входам- выходам коммутаторов данных 1-Й строки матрицы и к информационному входу-выходу И+2 блока оперативной 1-й строки матрицы, входы адреса и разрядов управления записью/считыванием 1-го процессора системы соединены с первыми информационными входами мультиплексоров адреса и управления 1-й строки матрицы соответственно и с адресным входом и входом управления записью считывания И+2-го блока оперативной памяти -й строки матрицы соответственно, третий двунаправленный информационный вход- выход Ц коммутатора данных ( - 1 И) соединен с третьими двунаправленными информационными входами-выходами 1, 3 и 1, 1+1 коммутаторов данных (к =+ 1 И;- 1), информационный, адресный входы и вход управления вводом- выводом -го контролллера обмена сое динены с входом-выходом данных 1-го процессора системы, входом 1-го канала адреса и входом разрядов управления вводом-выводом 1-й шины управления системы соответственно, -е входы признака адреса и управления вводом-выводом первого и второго блоков управления режимом соединены с входом -го канала адреса и входами разрядов управления вводом-выводом -й шины управления системы соответственно, выход первого блока управления режимом подключен к входам управления всех коммутаторов обмена, мультиплексоров адреса и управления и к входам запуска всех контроллеров обмена, выход второго блока управления режимом и выход элемента И являются первым и вторым выходами прерывания системы, выход признака конца обмена 1 контроллера обмена подключен к -му входу элемента И, выход адреса перезаписи и выход управления записью/считыванием -го контроллера обмена соединены с вторыми информационными входами Е, 1 и Г, 1+1 мульСистема коммутации процессоров, содержащая матрицу И, И+1 коммутаторов данных, где И - количество коммутируемых процессоров, матрицу мультиплексоров адреса, матрицу мультиплексоров управления и матрицу И, И+2 блоков оперативной памяти, о т - л и ч а ю щ а я с я тем, что, с целью сокращения затрат оборудования,50 в нее введены И контроллеров обмена, два блока управления режимом и элемент И, вход начальной установки системы соединен с входами сброса блоков управления режимом, вход син хронизации системы соединен с входами синхронизации всех контроллеров обмена, информационный вход-выход,з 126297б) Формирование синхроимпульсов, определяющих начало и длительность записи и считывания (эти синхроимпульсы Формируются на выходах управления записью (считыванием) контролерров 10 обмена); в) осуществление строго5 определенного числа тактов перезаписи, код числа тактов перезаписи загружается в соответствующий контроллер 10 обмвна перед началом решения задачи; г) Формирование сигнала "Конец обмена" (КО), когда реализовано необходимое число тактов перезаписи (такой сигнал с уровнем логической единицы формируется на выходе лризнака конца обмена конттроллера 10 обмена), Таким образом, в ходе функционирования системы происходит чередование режимов "Работа и режимов "Обмен". В режиме "Работа"20 в процессорах 38 .работающих автономно и параллельно, происходит решение основной задачи. В режиме "Обмен" происходит обмен данными (по И каналам сразу) между процессорами 36 а также автономное и параллельное решение фоновой задачи. Синхронизация работы вычислительной системы обеспечивается синхрогенератором 37 и блоком 38 сброса, который формирует сигнал "Сброс" (СБР) при включе - нии питающих напряжений. Сигнал СБР производит начальную установку внутренних регистров и счетчиков всех процессоров, а также обеспечивает необходимое начальное состояние триг- З 5 геров, входящих в блоки 32 и 33 управления режимом. Формула изобретения,40 адресный вход и вх( д управления :аписью/считыванием 11 блока оператив- ной памяти ( = 1, , И; 1 = 1, И+1) подключены к первому двунаправленному информационному входу-выходутиплексоров адреса и управления соотВЕТСТВЕЕЕЕЕО (Г - 3. рр р Е Е р р ") ра каждый контроллер обмена содержитузел ввода-вывода, схему сравнения,счетчик, трелггер и элемент И, первыйвход которого соединен с входами синхронизации триггера и контроллера,вход запуска которого соединен с входом сброса счетчика, выход которогоявляется выходом адреса перезаписикоытролллера и соединен с первым информационным входом схемы сравнения,второй информационный вход и выходравенства которой соединены с выходомузла ввода-вывода и информационнымВХОДОМ ТРИГГЕРа ПР 51 МОйЕ ВЫХОД КОТО-рого является выходом признака концаобмена контроллера, а инверсный выходподключен к второму Входу элемента И,выход которого является выходом управнения записью/считыванием и соединен со счетным входом счетчика,информационный, адресный и вход управления узла ввода-вывода являютсяодноименными входами контроллера,а первый и второй блоки управлениярежимом содержат И дешифраторов Итриггеров и элемент И, выход которого д явпяется Выходом блока, информационный вход 1-го дешифратора является1.-м входом признака адреса блока,первый и второй выхоцы з.-го дешифратора,подключены к входам установки и сброса 1-го триггера соответст.)венно, выход которого подключен к1.-му входу элемента И, вход синхронизации -го триггера является з.-м вхо.цом управления вводом-выводом блока, рО входы сброса триггеров соединены свходом сброса блока.1242977 Составитель А. УшаТехред М.Ходанич ктор В. Ивано Корректор Е. Сирохм каэ 3707/49 Тираж 671 ВНИИПИ Государственного комитета СС по делам изобретений и открытий 113035, Москва, Ж, Раушская наб

СмотретьЗаявка

3792458, 04.07.1984

ФИЛИАЛ "ВОСХОД" МОСКОВСКОГО ОРДЕНА ЛЕНИНА И ОРДЕНА ОКТЯБРЬСКОЙ РЕВОЛЮЦИИ АВИАЦИОННОГО ИНСТИТУТА ИМ. СЕРГО ОРДЖОНИКИДЗЕ

КОМАРОВ АНАТОЛИЙ ВЕНИАМИНОВИЧ, КОНОВАЛОВ НИКОЛАЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 15/163

Метки: коммутации, процессоров

Опубликовано: 07.07.1986

Код ссылки

<a href="https://patents.su/5-1242977-sistema-kommutacii-processorov.html" target="_blank" rel="follow" title="База патентов СССР">Система коммутации процессоров</a>

Предыдущий патент: Микропроцессорная система с контролем

Следующий патент: Система коммутации

Случайный патент: Суппорт к строгальному станку для обработки гребных винтов