Сумматор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 541172

Авторы: Воробьев, Грехнев, Павлюченков

Текст

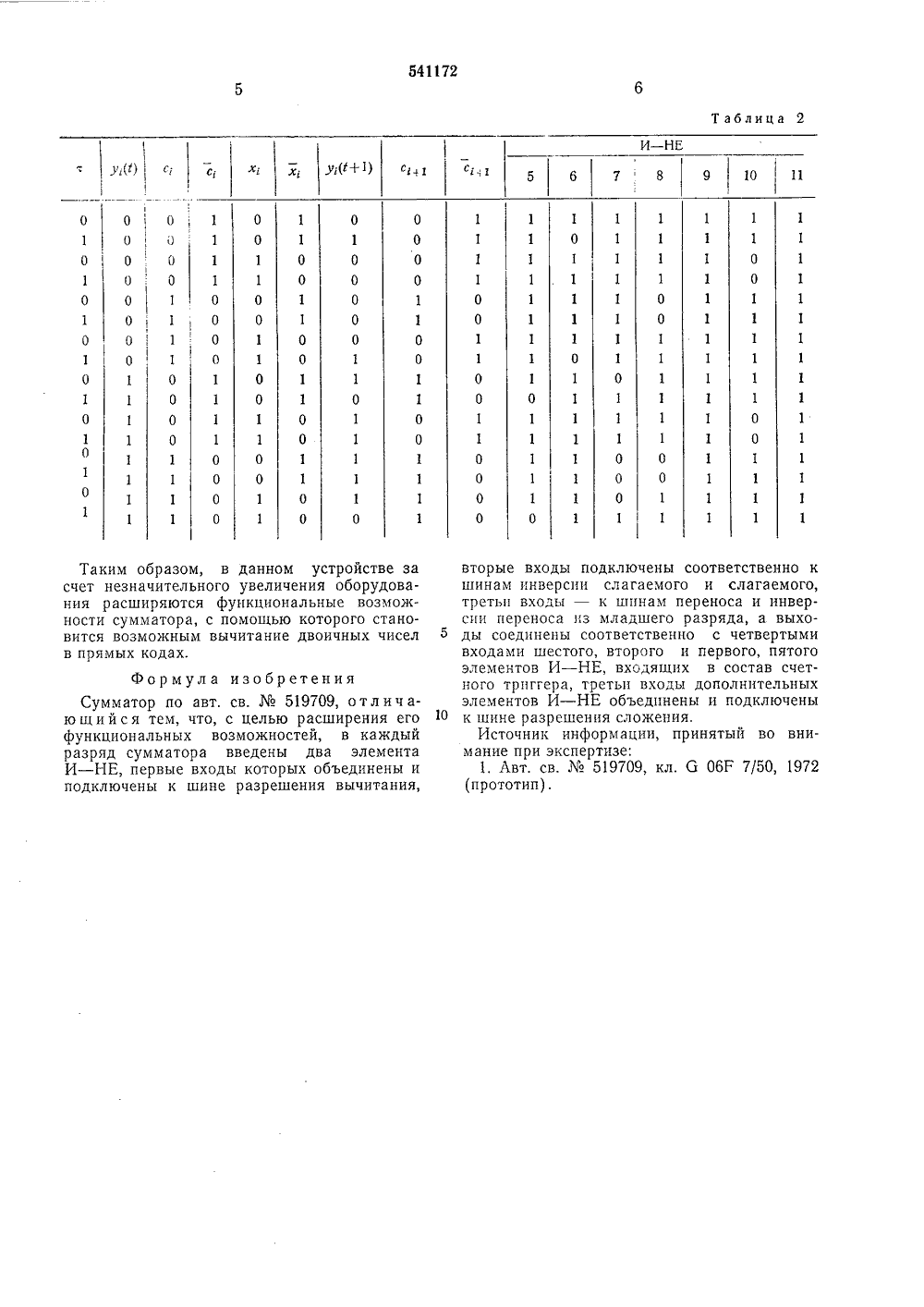

541172 ОПИСАНИЕИЗОБРЕТЕН И ЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советских Социалистических РесоурчикГосударственный комитет Совета Министров СССР 53) УД Опубликовано 30,12.76, Бюллетень4Дата опубликования описания 25.01.77 1.325.588.8) ло делам изобретен крытн 72) Авторы изобретени хнев, Н. П. Павлюченков ье(54) СУММАТОР Изобретение относится к области автоматики и вычислительной техники.Известен сумматор по основному авт. св.519709, содержащий в каждом разряде счетный триггер, выполненный на элементах И - НЕ, и дополнительные элементы И - НЕ. В счетном триггере первые входы первого и второго элементов И - НЕ подключены к тактовой шине, а выходы - к первым входам третьего и четвертого элементов И - НЕ соответственно. Второй вход третьего элемента И - НЕ соединен с выходом четвертого элемента И - НЕ, а второй вход четвертого - с выходом третьего и первым входом пятого элементов И - НЕ, второй вход которого под ключен к выходу первого, а выход - к первому входу шестого элемента И - НЕ. Второй вход шестого элемента И - НЕ подсоединен к выходу, а второй вход - к второму входу второго и входу седьмого элемента И - НЕ. Вы ход седьмого элемента И - НЕ соединен с вторым входом первого элемента И - НЕ. Шина слагаемого и шина переноса из младшего разряда подключены к входам первого дополнительного элемента И - НЕ, шины ин версии слагаемого и инверсии переноса пз младшего разряда - к входам второго дополнительного элемента И - НЕ, а выходы дополнительных элементов И - НЕ - к третьим входам соответственно второго и шестого 30 и первого и пятого элементов И - НЕ. Выходы шестого и седьмого элементов И - НЕ являются выходами переноса и инверсии переноса в старший разряд.С помощью этого сумматора нельзя производить вычитание двоичных чисел.Цель изобретения - расширение функциональных возможностей сумматора,Для этого в каждый разряд сумматора введены два элемента И - НЕ, первые входы которых объединены и подключены к шине разрешения вычитания, вторые входы подсоединены соответственно к шинам инверсии слагаемого и слагаемого, третьи входы - к шинам переноса и инверсии переноса из младшего разряда, а выходы соединены соответственно с четвертыми входами шестого, второго и первого, пятого элементов И - НЕ, входящих в состав счетного триггера. Третьи входы дополнительных элементов И - НЕ объединены и подключены к шине разрешения сложения.На чертеже представлена функциональная схема одного разряда сумматора.Элементы И - НЕ 1 - 7 образуют счетный триггер. Шины слагаемого и переноса из младшего разряда подключены к первому и второму входам дополнительного элемента И - НЕ 8, шины инверсии слагаемого и инверсии переноса из младшего разряда - к541172 Таблица 1 И - НЕ 141 у; (1+1) 6 7 10 11 первому и второму входам дополнительного элемента И - НЕ 9. Третьи входы этих элементов объединены и подсоедипены к шине разрешения сложения. К входам введенного элемента И - НЕ 10 подключены шины инверсии слагаемого, переноса из младшего разряда и разрешения вычитания, а к входам введенного элемента И - НЕ 11 - шины слагаемого, инверсии переноса из младшего разряда и разрешения вычитания. Результат суммирования или вычитания у;(1+1) будет получен на выходе элемента И - НЕ 2, сигнал переноса в старший разряд с;+ и его инверсия с,+, на выходах элементов И - НЕ 4 и 3, тактовая шина подключена к входам элементов И - НЕ 5 и 6. В режиме сложения на шину разрешения сложения подан сигнал, равный логической единице, а на шину разрешения вычитания - сигнал, равный логическому нулю. Сигнал переноса в старший разряд и его инверсия формируются элементами И - НЕ 3, 4, 7 - 11. Поскольку в начальный момент сигнал на тактовой шине отсутствует, то на выходах элементов И - НЕ 5 и 6 присутствует сигнал логической единицы и связи с выходов этих В режиме вычитания на шину разрешения сложения подан сигнал, равный логическому нулю, а на шину разрешения вычитания - сигнал, равный логической единице, Сумматор в режиме вычитания работает аналогичным образом за исключением того, что по шине переноса из младшего разряда поступает инверсия сигнала заема из младшего разряда, а по шине инверсии переноса из элементов на входы элементов И - НЕ 4 и 7 не влияют на формирование сигнала переноса. В момент изменения состояния счетного триггера под действием тактового сигнала эти связи позволяют запомнить предыдущее значение сигнала переноса в старший разряд на время действия тактового сигнала, т. е. сигнал переноса в старший разряд меняет свое значение в тот момент времени, 10 когда отсутствует тактовый сигнал. Изменение состояния элемента И - НЕ 5 происходит в том случае, если счетный триггер находится в состоянии 1, а значения сигналов переноса из младшего разряда и второго сла гаемого не равны между собой; состояниеэлемента И - НЕ 6 изменяется тогда, когда счетный триггер находится в состоянии 0, а значения сигналов переноса из младшего разряда, и второго слагаемого так же не рав ны между собой. В табл. 1 приведены значения выходных сигналов элементов И - НЕ, а также результат суммирования у;(1+1) в зависимости от предыдущего состояния счетного триггера (у, (1) ) и значений входных сиг налов, позволяющие проследить все возможные ситуации, возникающие в процессе суммирования. младшего разряда - сигнал заема из младшего разряда. Значение выходных сигналов З 0 элементов И - НЕ, а также результат вычитания у;(1+1) в зависимости от предыдущего состояния счетного триггера (у;(1 и значений входных сигналов, позволяющие проследить все возможные ситуации, возникаю щие в процессе вычитания, приведены в табл, 2.с;,у у (+1) сс 78 0О , 1 0О, 1 00 1 00 11О1 О 01 0 01 0 01 0 Таким образом, в данном устройстве за счет незначительного увеличения оборудования расширяются функциональные возможности сумматора, с помощью которого становится возможным вычитание двоичных чисел в прямых кодах. вторые входы подключены соответственно к шинам инверсии слагаемого и слагаемого, третьи входы - к шинам переноса и инверсии переноса из младшего разряда, а выхо ды соединены соответственно с четвертымивходами шестого, второго и первого, пятого элементов И - НЕ, входящих в состав счетного триггера, третьи входы дополнительных элементов И - НЕ объединены и подключены 10 к шине разрешения сложения.Источник информации, принятый во внимание при экспертизе:1, Лвт. св.519709, кл. 6 06 Р 7/50, 1972 (прототип). Формула изобретенияСумматор по авт. св.519709, отличающийсяся тем, что, с целью расширения его функциональных возможностей, в каждый разряд сумматора введены два элемента И - НЕ, первые входы которых объединены и подключены к шине разрешения вычитания,0 0 1 1 0 0 1 1 О 0 1 1 0 0 1 1 0 0 0 0 1 1 0 0 1 1 0 0 1 1 1 1 11 1 1 1 1 1 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 0 0 0 1 1 1 1 1 0 0 1 1 1 1 1 1 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1541172 Составитель В. Березкин Техред Е. Петрова Редактор И. Грузова Корректор Т. Гревцова Типография, пр. Сапунова, 2 Заказ 2897/5 Изд.1898 Тираж 864 Подписное ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д. 4/5

СмотретьЗаявка

2015106, 05.04.1974

ВОЙСКОВАЯ ЧАСТЬ 44388-Р11

ГРЕХНЕВ ВЛАДИМИР АЛЕКСЕЕВИЧ, ПАВЛЮЧЕНКОВ НИКОЛАЙ ПАВЛОВИЧ, ВОРОБЬЕВ ЮРИЙ ЗАХАРОВИЧ

МПК / Метки

МПК: G06F 7/50

Метки: сумматор

Опубликовано: 30.12.1976

Код ссылки

<a href="https://patents.su/4-541172-summator.html" target="_blank" rel="follow" title="База патентов СССР">Сумматор</a>

Предыдущий патент: Двоичное устройство деления

Следующий патент: Сумматор

Случайный патент: Дегазатор