Преобразователь правильной двоичной дроби в двоично десятичную дробь и целых двоично-десятичных чисел в двоичные

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 526885

Автор: Штурман

Текст

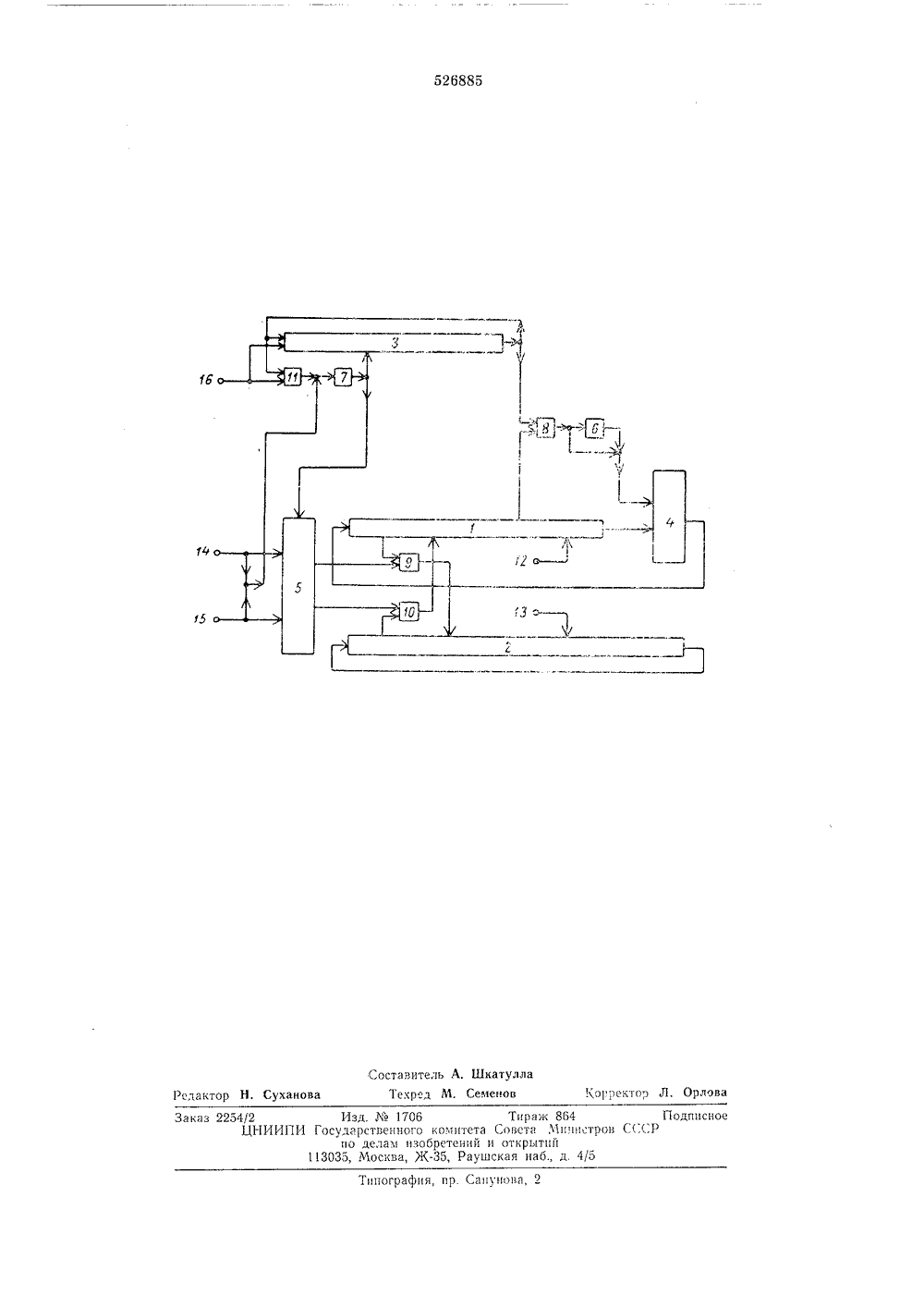

О П И С А Н И Е п 1) 526885ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советских Социалистических Республик(21) 2000320/24 2) 3 влено 26.02.7 рисоединениек 1 заявкисударственныи комитет вета Министров СССР) Автор изобретени П, Штурм Всесоюзный институт научной и техничеАН СССР 1) Заявител Й ДРО) ПРЕОБРАЗОВАТЕЛЬ ПРАВИЛЬНОЙ ДВОИЧНО Б В ДВОИЧНО-ДЕСЯТИЧНУЮ ДРОБЬ ЦЕЛЪХ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ В ДВОИЧНЫЕсш ирен Изобретение относится к области автоматики и вычислительной техники и предназначено для последовательного преобразования кодов правильных дробей и целых двоичных чисел из одной системы счисления в другую.Известны преобразователи кодов, используемые в устройствах автоматики и вычислительной техники и позволяющие преобразовывать коды чисел из одной системы счисления в другую.Первое из известных устройств позволяет осуществлять преобразование двоичного кода в двоично-десятичный и наоборот, как целых, так и дробных чисел, однако оно содержит большой объем оборудования. 1Второе из известных устройств содержит небольшой объем оборудования, однако оно предназначено для преобразования только дробных чисел. 2Наиболее близким техническим решением к данному изобретению является преобразователь, содержащий три линии задержки, одноразрядный двоичный вычитатель, коммутатор кода операции, два элемента задержки и четыре элемента И, причем первый промежуточный вход первой линии задержки соединен с первой входной шиной, выход первой линии задержки подключен к первому входу одноразрядного двоичного вычитателя, а первый промежуточный выход соединен с первым входом первого элемента И, выход которого соединен со вторым входом одноразрядного двоичного вычитателя и входом первого элемента задержки, выход которого подключен ко второму входу одноразрядного двоичного вычитателя, выход которого соединен с входом первой линии задержки, а выход второй линии задержки соединен с ее входом. 3Недостатком указанного преобразователяявляется ограниченный класс решаемых задач, поскольку он осуществляет преобразование только дробных чисел.Целью изобретения является ра ие 15 класса решаемых задач.Поставленная цель достигается за счет того, что второй промежуточный выход первой линии задержки соединен с первым входом второго элемента И, второй вход которого 20 соединен с первым выходом коммутатора кода операции, а выход подключен к первому промежуточному входу второй линии задержки, второй промежуточный вход которой соединен со второй входной шиной, а промежу точный выход соединен с первым входомтретьего элемента И, второй вход которого соединен со вторым выходом коммутатора кода операции, а выход подключен ко второму промежуточному входу первой линии задерж ки, первый и второй входы коммутатора кодаоперации подключены соответственно к третьей и четвертой входным шинам и соединены с выходом четвертого элемента И и с входом второго элемента задержки, выход которого соединен с третьим входом коммутатора кода операции и промежуточным входом третьей линии задержки, выход которой соединен со вторым входом первого элемента И и ее первым входом, второй вход третьей линии задержки соединен с пятой входной шиной и первым входом четвертого элемента И, второй вход которого соединен с первым входом третьей линии задержки.На чертеже представлена блок-схема преобразователя.Преобразователь содержит первую линию задержки 1, вторую линию задержки 2, третью линию задержки 3, одноразрядный двоичный гычитатель 4, коммутатор 5 кода операции, первый элемент 6 задержки, второй элемент 7 задержки, первый элемент И 8, второй элемент И 9, третий элемент И 10, четвертый элемент И 11, первую входную шину 12, вторую входную шину 13, третью входную шину 14, четвертую входную шину 15 и пятую входную шину 16,В качестве метода преобразования как дробей, так и целых чисел принят метод сдвига и коррекции.Преобразование правильной двоичной дроби в двоично-десятичную дробь.Сущность метода сдвига и коррекции для этого вида преобразования заключается в том, что мантисса исходной двоичной дроби последовательно делится на два, т. е. сдвигается на один разряд в сторону младших разрядов. При этом двоичные разряды, выходящие за пределы разрядной сетки исходной дроби, переходят в качестве старших разрядов искомой двоично-десятичной дроби.Коррекции, заключающейся в вычитании кода 0011 (три), подлежат те тетрады, в которые единица переходит при очередном цикле сдвига из соседней (старшей) тетрады или из исходной двоичной дроби. Например, если младший разряд тетрады или двоичного числа до сдвига есть ноль, то старший разряд соответствующей (соседней) тетрады после сдвига сохранит свое нулевое значение, Коррекции в этом случае не потребуется. Если же указанный разряд до сдвига есть единица, то после сдвига он станет старшим разрядом тетрады (1000, 1001 и т, д.), что потребует ее коррекции.Работа преобразователя происходит следующим образом.На линию задержки 2 по шине 13 последовательно поступает исходная двоичная дробь. Одновременно по шине 15 в коммутатор кода операции 5 и на линию задержки 3 поступает импульс кода операции. Обе линии задержки благодаря обратной связи образуют циркуляционные регистры, Один из них обеспечивает хранение исходной двоичной дроби (а далее промежуточных результатов),5 О 15 20 25 зо 35 4 О 45 50 55 ьо 65 а другой - управляющего импульса, который осуществляет все необходимые переключения схемы.Операция сдвига реализуется за счет увеличения на один такт периода обращения управляющего импульса в линии 3. Это происходит в каждом цикле, когда по шине 16 (на элемент И 11) поступает управляющий импульс, Задержка на один такт этого импульса осуществляется при помощи элемента 7, который со сдвигом вновь вводит его в линию 3. Одновременно импульс с выхода элемента 7, пройдя через коммутатор 5, на элементе 10 в каждом цикле преобразования опрашивает двоичную дробь, циркулирующую в линии 2, на наличие единицы в младшем разряде. Если таковая имеется, то она через элемент 10 поступает на линию задержки 1 в качестве старшего разряда преобразуемой двоично-десятичной дроби.Необходимость коррекции определяется с помощью элемента 8, при этом выявляются те тетрады, в которые при сдвиге переходит единица. Тетрады двоично-десятичной дроби циркулируют в регистре, образованном линией задержки 1 и вычитателем 4.На элементе И 8 импульсами с выхода линии задержки 3 последовательно опрашиваются старшие двоичные разряды всех тетрад. Если этот разряд равен единице, то на элементах 8 и 6 вырабатывается корректирующий код 0011, который в качестве вычитаемого поступает на одноразрядный двоичный вычитатель 4, где происходит вычитание кода коррекции из соответствующей тетрады. Благодаря этому компенсируется ошибка, неизбежно возникающая при сдвиге (делений на два) двоично-десятичных дробей.Преобразование целых двоично-десятичных чисел в двоичные числа.Сущность метода сдвига и коррекции для этого вида преобразования заключается в том, что исходное десятичное число (а далее - промежуточные значения) также делится на два. Младшие разряды двоично-десятичного числа после сдвига переходят на место старших разрядов формируемого двоичного числа.Коррекции, заключающейся в вычитании кода 0011 (три), также подлежат те тетрады, в которые единица переходит при очередном цикле сдвига из соседней (старшей) тетрады.Работа преобразователя в этом режиме начинается с прихода исходного двоично-десятичного числа по шине 12 на линию задержки 1 и импульса кода операции по шине 14.В каждом цикле преобразования управляющий импульс с выхода элемента 7, пройдя через коммутатор 5 кода операции, на элементе 9 опрашивает младшие разряды десятичного числа. Если в этом разряде содержится единица, то она, пройдя через элемент 9, поступает в линию 2 в качестве старшего разряда двоичного числа.В остальном схема работает аналогично то 526885 6му, как это было рассмотрено для режима преобразования дробей.В обоих случаях время преобразования составляет Й циклов, где Й - число разрядов двоичного числа.Каждый из рассмотренных блоков преобразователя имеет простейшее строение, требующее минимальных аппаратурных затрат. Например, три линии задержки, составленные из последовательно соединенных накопительных элементов, за счет обратных связей осразу.от циркуляционные регистры, где хранятся исходные операнды, промежуточные и окончательные результаты преобразований, а также управляющий импульс.При этом, если линия 2 должна содержать не менее Й накопительных элементов (по числу разрядов двоичного числа или дроби), то регистр, составленный из первой линии задержки 1 и вычитателя 4, должен сыть рассчитан на хранение не менее (4 Й 1 оо 2) разрядного двоично-десятичного кода. Периоды обращения этих регистров должны быть кратны между собой, а также периоду осращения циркуляционного регистра, реализованного на линии задержки 3, равному четырем тактам.Предлагаемый преобразователь позволяет при небольших аппаратурных затратах осуществлять преобразование как дробньх, так и целых чисел. Формула изобретенияПреобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные, содержащий три линии задержки, одноразрядный двоичный вычитатель, коммутатор кода операции, два элемента задержки и четыре элемента И, поичем первый промежуточный вход первой линии задержки соединен с первсй входной шиной, выход первой линии задержки подключен к первому входу одноразрядного двоичного вычитателя, а первый промежуточный выход соединен с первым входом первого элемента И, выход которого соединен со вторым входом одноразрядного двоичного вычитателя и входом первого элемента за.5 держки, выход которого подключен ко второму входу одноразрядного двоичного вычитателя, выход которого соединен с входом первой линии задержки, а выход второй линии задержки соединен с ее входом, о т л и ч а ю 1 о щи й ся тем, что, с целью расширения класса решаемых задач, второй промежуточный выход первои линии задержки соединен с первым входом второго элемента И, второй вход которого соединен с первым выходом 15 коммутатора кода операции, а выход подключен к первому промежуточному входу второй линии задержки, второй промежуточный вход которой соединен со второй входной шиной, а промежуточный выход соединен с первым о входом третьего элемента И, второй вход которого соединен со вторым выходом коммутатора кода операции, а выход подключен ко второму промежуточному входу первой линии задержки, первый и второй входы ком мутатора кода операции подключены соответственно к третьей и четвертой входным шинам и соединены с выходом четвертого элемента И и с входом второго элемента задержки, выход которого соединен с третьим входом ком- ЗО мутатора кода операции и промежуточнымвходом третьей линии задержки, выход которой соединен со вторым входом первого элемента И и ее первым входом, второй вход третьей линии задержки соединен с пятой Зб входной шиной и первым входом четвертогоэлемента И, второй вход которого соединен с первым входом третьей линии задержки,Источники информации, принятые во внимание прп экспертизе:4 о 1, Лвт. св.201774, кл, б 06 Р 5/02,08.09.67.2. Авт. св.302714, кл. б 06 Р 5,02,28.04. 1.3. Лвт, св395831, кл, б 06 Р 5(02, 45 28.08,73 (прототип) .526885 но еда ктор Изд.1706 Тираж 864Государственного комитета Совета Ми.пстроппо делам изобретений и открьтий3035, Москва, Ж, Раушская нао., д. 45 одппсн каз 22542ЦНИИП ипографня, пр, Са) нова, 2 ставитель А. ШкатуллаТекред М. Семенов Ко,ектор Л. Орлова

СмотретьЗаявка

2000320, 26.02.1974

ВСЕСОЮЗНЫЙ ИНСТИТУТ НАУЧНОЙ И ТЕХНИЧЕСКОЙ ИНФОРМАЦИИ АН СССР

ШТУРМАН ЯКОВ ПЕТРОВИЧ

МПК / Метки

МПК: G06F 5/02

Метки: двоично, двоично-десятичных, двоичной, двоичные, десятичную, дроби, дробь, правильной, целых, чисел

Опубликовано: 30.08.1976

Код ссылки

<a href="https://patents.su/4-526885-preobrazovatel-pravilnojj-dvoichnojj-drobi-v-dvoichno-desyatichnuyu-drob-i-celykh-dvoichno-desyatichnykh-chisel-v-dvoichnye.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь правильной двоичной дроби в двоично десятичную дробь и целых двоично-десятичных чисел в двоичные</a>