Преобразователь правильной двоичнодесятичной дроби в двоичную дробь и целых двоичных чисел в двоично-десятичные числа

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 526886

Автор: Штурман

Текст

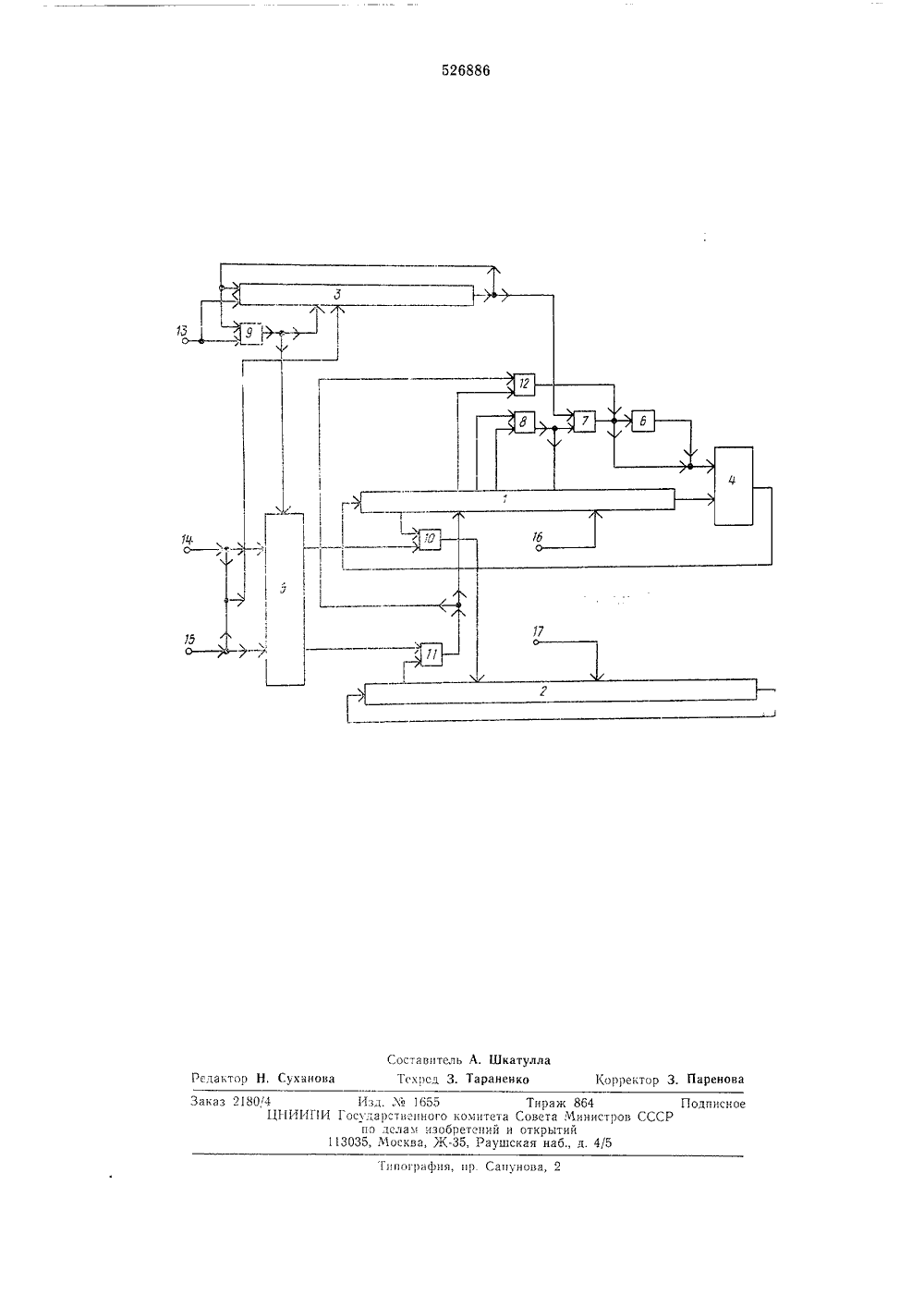

) 52688 Н И И Союз Советски иалистическихРеспублик ЗОБРЕТЕН И ВТОРСКОМУ СВИДЕТЕЛЬСТВУ олнительное к авт. св 51) М. Кл. б 06 Г 5,02(23) ПриоритетОпубликовано 30,08,76. Бюллетень32Дата опубликования описания 20.10,76 Государственный комитет Совета Министров СССР по делам изобретений 681,325(088.8(72) Автор изобретения Я. П. Штурман сесоюзный институт научной и технической информации АН СССР(54) ПРЕОБРАЗОВАТЕЛЬ ПРАВИЛЬНОЙ ВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ И ЦЕЛЫХ ДВОИЧНЫХ ЧИСЕЛ ДВОИЧНО-ДЕСЯТИЧНЫЕ ЧИСЛАВ Изобретение относится к вычислительной техничке и предназначено для последовательного преобразования кодов дробей и целых чисел.Известны преобразователи кодов, выполняющие преобразования кодов из одной системы счисления в другую.Один из известных преобразователей, содержащий сдвиговый регистр, позволяет осуществлять преобразование двоичного кода в двоично-десятичный и наоборот как целых, так и дробных чисел, однако он содержит большой объем оборудования 1.Второй из известных преобразователей осуществляет преобразование правилыной двоично-десятичной дроби в двоичную дрооь, однако он также содержит достаточно большой объем оборудования и не осуществляет лреобразование целых чисел 21.Наиболее близким техническим решением к даиному изобретению является преобразователь правилыной двоично-десятичной дроби в двоичную дробь, содержащий три линии задержки, одноразрядный двоичный, сумматор, коммутатор кода операции, элемент задержки и шесть элементов Ипричем выход первой линии задержки соединен с первым входом одноразрядного двоичного сумматора, выход которого соединен с входом первой линии задержки, первый промежуточный выход которои соединен с гервым входом первого элемента И, выход которого соединен с входом и выходом элемента задержки и вторым входом одноразрядного двоичного сумматора, выходы 5 второй и третьей линий задержки соединенысоответственно с пх входами 31.Недостатком указанного преобр азователяявляется ограниченный класс решаемых задач, поскольку с его помощью невозможно 10 осуществлять преобразование целых чисел.Целью изобретения является расширениекласса решаемых задач.Указанная цель достигается тем, что второйи третий промежуточные выходы первой линии 15 задержки соединены с входами второго элемента И, выход которого подключен к первому входу первого элемента И, второй вход которого соединен с выходом третьей линии задержки и перовым входом третьего элемента 20 И, второй вход которого соединен с первойвходной шинной и дополнительным входом третьей линии задержки, а выход соединен с первым промежуточным входом третьей линии задержки и первым входом коммутатора кода 25 операции, второй и третий входы которогоподключены соответственно к второй и третьей входным шинам и соединены со вторым промежуточным входом третьей линии задержки, первый и второй выходы, коммутатора 30 кода операции подключены к первым входам3четвертого и пятого элементов И, второй вход 1 сВертОГО э,еемеета И соединен с чстВсртым иромеькуточным выходом первой линии задержкьь, первый 111 имежутоныьь вход которой соедьИон с четвертои Входной шиной, а пятый промеькуточный выход соединен с первым Входом шсстого элемента И, выход которого подкл 10 чсн к Входу эе.1 сыта зеьдсржки а Второй вход соединен со вторым промежуточным Входом первой линии задержки и выхо 1 ох пятого элемента И, второй вход которого соединен с промежуточным выходом Втсдой линьи задержки, первы Елромежточпый вход которой сосдинсн с выходом четвертого элемента И, а Второй промськуточный вход подклО Сн к пягой входной,шьИе.На чертсжс пуедставгеня блок-схема преобразователя кодов.Преобразователь содсржьт перьую линию задержки 1, вторуо линию задержки 2, третью линию задоржки 3, одноразрядный двоичный сумматор 4, коммутатор 5 кода опсрации, элемент 6 задержки, первый элемент И 7, второй элемент И 8, третий элемент И 9, четвсчртый элемеыт И 10, пятый элемент И 11, шестой элсмснт И 12, порвуо входную шину 13, вторую входную шину 14, третьО входную шину 15, четвертую входнуьо шину 16 и пятую входную шину 17.Преобразование дрооных и целых чисел в у стройстве осу ществляется с помолеыо,еетодя сдвь 1 Я и КОррекции. В соответсВАР с этим ряссхОтрим р 1100 тустроиства В дВух режи мах; преобразоваьВе дробей и целых чисел.11 реобразовань 1 с правь 1 ль 1 Ой двоино-десятичной дроби в двоичную дробь, Мегод сдвига и коррекцьР для этого вида преобразования зяклеочаеся В том, что мантисса исходь 10 Й двоично-десятлцьтой дроби последовательно умноЕжается на два (путем сдвига на один разряд в сгсрону старших разрядов) с выделРниеы ряздядов целой части, формиду 1 ощих искомое двоичное числоначиная со старших разрядов. При этосм те тетрады, которые больше или равны 5, перед сдвигом корректируют. ся путем прибавления к ним 3.Преобразователь работает следуЕощьм образом.На линию задержки 1, образующую с одноразрядным двоичным сумматором 4 циркуляционный регистр, по шине 16,последовательно поступают двоььчно-десятььчные разряды исходной дроби, Одновременно по щине 14 в комхутатор 5 кода операции и на третью линию задержки 3, такьке имеющую обратную связь, поступает импульс, кода операции, который циркулирует в ней в течение всего времени преобразоватья, обеспечивая выработку необходимых управляющих импульсов.Требуемые сдвиги осуществляеотся за счет перестроения управляющего импульса в циркуляцььоныом регистре и сокращения на один такт периода его обращения. Это происходит в каждом цикле при поступлении,по шине 13 управляющего импульса, В этом случае упД 10 15 20 25 ЗО Зб 40 45 50 55 60 65 4равляющий импульс, пройдя через элемент 11 9 и через коммутатор 5, выделит на элемсьпе 10 очередной разряд целой части, который перейдет на Вторую линию задержки 2. Бсьагодары,наличиО обратной связи она образует циркуляционный регистр, где и осуществляется последовательное формирование и хранение искомой двоичной дроби.Коррекция тетрад выполняется следующим образом.На первом элементе И 7 все тетрады проверяются на наличие у них разрядов с весовым коэффициентом р=3 (т. е. тетрады, равные 8 и 9). Элемент И 8 вырабатывает импульсы для тетрад, содержащих числа 5, 6 или 7. Таким образом, указанные элементы срабатывают во всех случаяхкогда значение тетрад не меньше 5. При этом с помощью накопительного элемента 6 вырабатывается корректирующий,код 0011 (три). Этот код посылается на сумматор 4, где и осуществляется сложение соответствующих тетрад, нуждающихся в коррекции, с кодом коррекции. Этим самым компенсируется ошибка, которая неизбежна при последующем умножении на два двоично-,десятичных дробей, реализуемом с помощью операции сдвига на один такт.Преобразование целых двоичных чисел в двоично-десятичные числа.Метод сдвига и коррекции для этого вида преобразования заключается в том, что исходное двоичное число также последовательно умножается на два (путем сдвига на один разряд В сторону старших разрядов) с выде,ением старших разрядов, формирующих искомое двоична-десятичное число, начиная со старших разрьдов. При этом те тетрады, которые больше или равны 5, также перед сдвигом корректируются путам прибавления,к ним 3,Работа преобразователя в этом режиме осуществляется следующим образои.На линию задержки 2 по шине 17 поступает исходное двоичное число, а по шине 15 - иипульс кода операции, С элемента 11 импульсамипоступающими с элемента 9 через коммутатор 5 кода операции, в каждом цикле снимается старший разряд, который направляется для хранения в циркуляционный регистр, образованный линией задержки 1 и сумматором 4,коррекция в рассматриваемом режиме происходит аналогично режиму преобразования дробей с той только разницей, что содержимое тетрады, равное 5, опрашивается на элементе И 12.В обоих р ассмотренных режимах полное время преобразования составляет й циклов, где Й - число разрядов двоичного числа.Каждый из рассмотренных отдельных блоков преобразователя имеет простейшее ст 1 роение, 11 ребующее минималыных аппаратурных затрат. Например, три линии задержки, составленные из последовательно,соединенныхнакопительных элементов, за счет обратных связей образуют циркуляциоьные регистры, где хранятся исходные операнды, ромежуточные и окончательные результаты преобразования, а также управляющий импульс.При этом линия 2 должна содержать не менее Й накопительных элементов (по числу разрядов двоичного числа), а регистр, составленный из линии задержки 1,и сумматора 4, должен быть рассчитан на хранение не менее (4 й 1 оо 2) -разрядного двоично-десятичного кода, Периоды обращения обоих регистров должны быть кратны между собой, а также периоду обращения циркуляционного регистра, реализованного на линии задержки 3, р авно му 4 такта м.Предлагаемый преобразователь правильной двоично-десятичной дроби в двоичную дробь и целых двоичных чисел,в двоично-десятичные числа позволе при спользован небольшого объема оборудования производить преобразавание как дробных, так и целых чисел. Формула изобретенияПреобразователь правильной двоично-десятичной дроби в двоичную дробь и целых двоичных чисел в двоично-десятичные числа, содержащий три линии задержки, одноразрядный двоичный сумматор, коммутатор кода операции, элемент задержки и шесть элементов И, причем выход первой линии задержки соединении с первым входом одноразрядного двоичного сумматора, выход которого соединен с входом первой линии задержки, первый промежуточный выход которой соединен с первым входом первого элемента И, выход которого соединен с входом и выходом элемента задержки и вторым входом одноразрядного двоичного сумматора, выходы второй и третьей линий задержки соединены соответственно с их входами, отличающийся тем, что, с целью расширения класса решаемых задач,второй и третий промсжуточныс выходы первси линии задерж.н сседневы с входамп второго элемента И, выход которого подключен к первому входу первого элемента И, второй вход 5 которого соединен с выходом третьей линиизадержки и первым входом третьего элемента И, второй вход которого соединен с первой входной шиной и дополнительным входом третьей линии задержки, а выход соединен с 10 первым промежуточным входом третьей лпшипзадержки н первым входом коммутатора коза операции, второй и третий входы, которого подключены соответственно к второй н третьей входным шинам и соединены со вторым 15 промежуточным входом третьей линии задержки, первый и второй выходы,кохмутатора кода опсфацип полоены к первым входам четвертс о и пятого элементов И, второй вход четвертого элемента И соединен с четвертым 20 промежуточным выходом нарвой линии задержки, первый промежуточньш вход которой соединен с четвертой входно шиной, а пятый прсхЮБ тс 1 ный вьход соединен с первым входом шестого элемента И, выход которого 25 подклочен к входу элемента задержки, а второй вход соединен со вторым промежуточным входом первой линии задержки и выходом пятого элемента И, второй вход которого соединен с прохежуточных выходом второй ли нпи задержки, псрзьш ьромеж точный входкоторой соединен с выходох четвертого элемента И, а второй промежуточный вход подключен к пятой входной шине. Источники пнформацш, принятые во вн;ванде при экспертизе:1, Авт. св. Л"о 201774, кл. . 06 Г 5,02,08.09.67.40 2. Лвт, сз. Л 331382, кл. 6 06 Г 5/02,07.03.72.3. Лвт. св. Ло 404077, кл. 6 06 Г 5,02,26.10.73.526886 Составитель А. ШкатуллаТсхрсд 3. Тараненко сдактор Н, Сухинова Корректор 3, Парено Тираж 854Совета Миноткрытийкая наб., д. писно стров СС 5 ипография, пр Сапунова, 2 аказ 2180 4 Изд. Ле 1555 ЦНИИПИ Государственного комитета по делаз изобретений и 113035, Москва, Ж, Рауш

СмотретьЗаявка

2000322, 26.02.1974

ВСЕСОЮЗНЫЙ ИНСТИТУТ НАУЧНОЙ И ТЕХНИЧЕСКОЙ ИНФОРМАЦИИ АН СССР

ШТУРМАН ЯКОВ ПЕТРОВИЧ

МПК / Метки

МПК: G06F 5/02

Метки: двоично-десятичные, двоичнодесятичной, двоичную, двоичных, дроби, дробь, правильной, целых, чисел, числа

Опубликовано: 30.08.1976

Код ссылки

<a href="https://patents.su/4-526886-preobrazovatel-pravilnojj-dvoichnodesyatichnojj-drobi-v-dvoichnuyu-drob-i-celykh-dvoichnykh-chisel-v-dvoichno-desyatichnye-chisla.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь правильной двоичнодесятичной дроби в двоичную дробь и целых двоичных чисел в двоично-десятичные числа</a>