Устройство микропрограммного управления с контролем

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

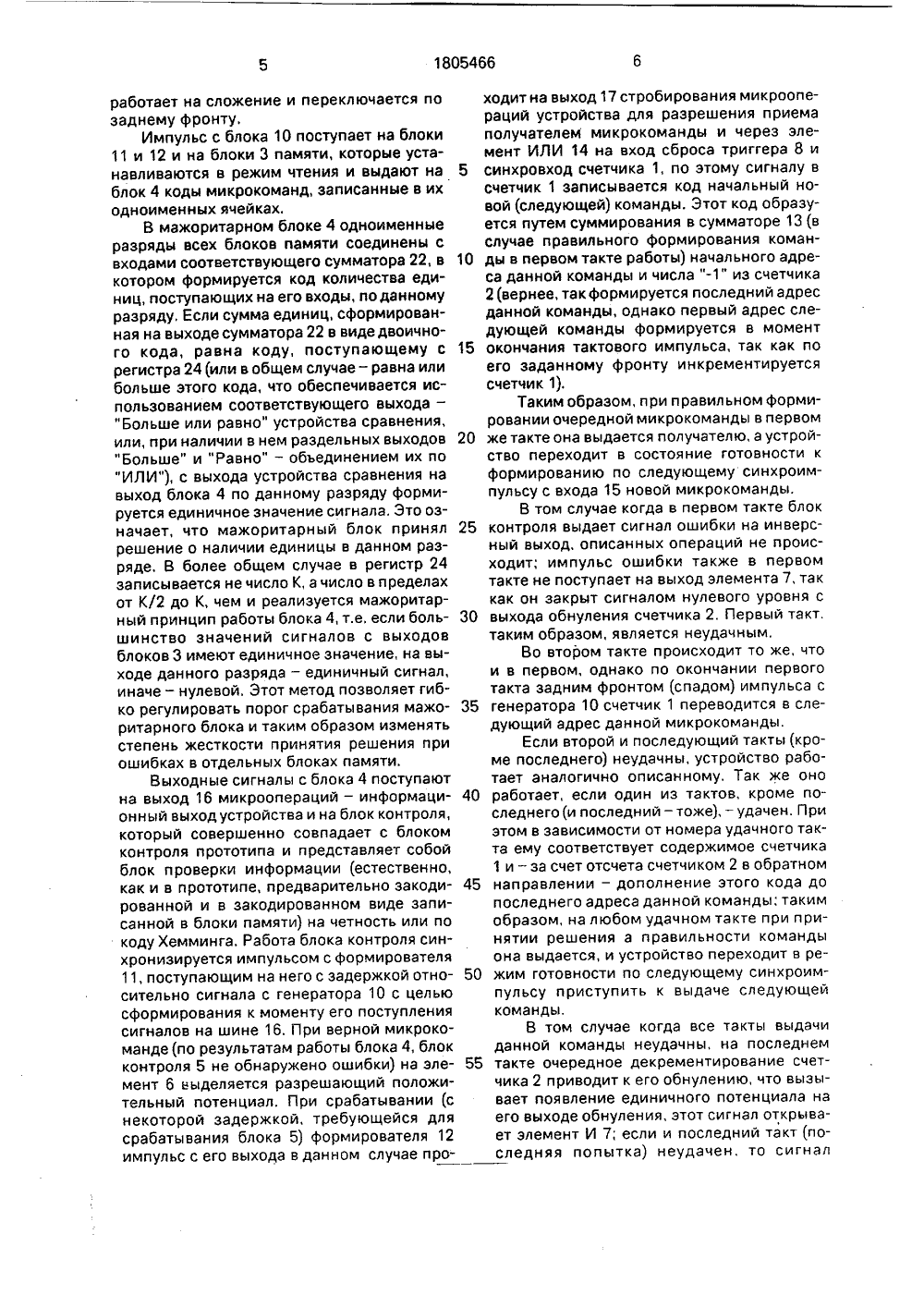

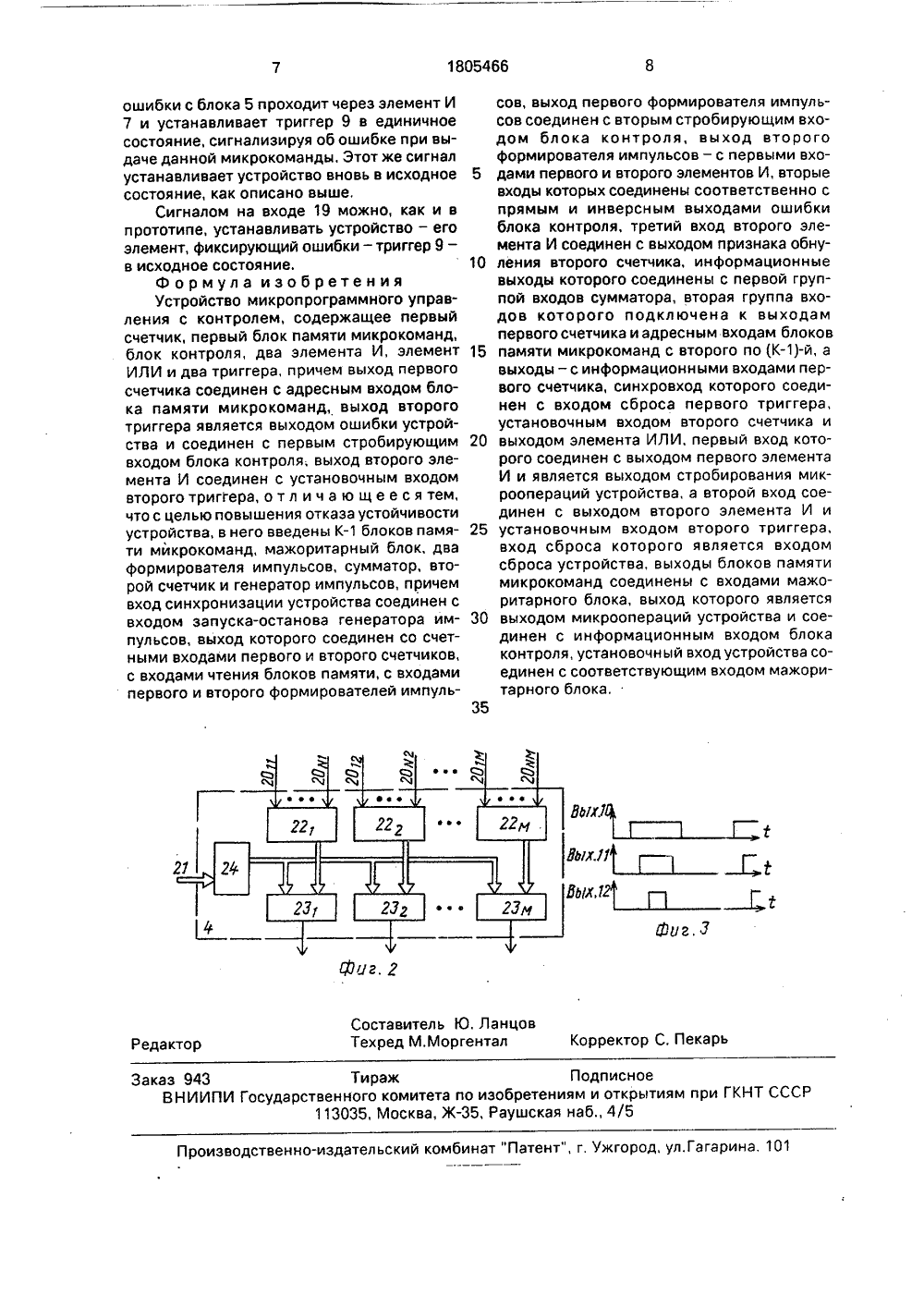

(ГОСПАТЕНТ ССС ПАТЕНТНО ПИСАНИЕ ИЗОБРЕТЕНАВТОРСКОМУ СВИДЕТЕЛЬСТВУ 54) УСТРОЙСТВО ГО УПРАВЛЕНИВ ИКРОПРО ОНТРОЛЕ ММН(71) Московский институт инженеров гражданской авиации(56) 1. Авторское свидетельство СССРМ 1309024, кл, 6 06 Р 9/22, 1983,2. Авторское свидетельство СССРМ 1508211, кл. 6 06 Р 9/22, 11/10, 1986,(57) Изобретение относится к вычислительной технике и может быть использовано при построении устройств микропрограммного управления с обнаружением и исправлением ошибок, Целью изобретения является повышение отказа устойчивости устройства, Для достижения указанной цели устройство микропрограммного управления с контролем содержит счетчик 1, блок памяти 31 - Зк микрокоманд, блок 5 контроля, два элемента И 6, 7, элемент ИЛИ 14, два триггера 8, 9, мажоритарный блок 4, два формирователя 11, 12 импульсов, сумматор 13, счетчик 2 и генератор 10 импульсов. 2 ил,Устройство относится к вычислительнойтехнике и может быть использовано при построении устройств микропрограммного управления с обнаружением и исправлениемошибок,Целью изобретения является повышение отказоустойчивости устройства.На фиг,1 приведена структурная схемаустройства микропрограммного управления с контролем; на фиг.2 - структурная 010схема мажоритарного блока; на фиг.З - временные диаграммы времязадающих узловустройства.Устройство микропрограммного управления с контролем содержит первыи 1 и 15второй 2 счетчики, группу 31 - Зк блоков памяти микропрограмм, мажоритарный 4блок, блок 5 контроля, первый 6 и второй 7элементы И, первый 7 и второй 9 триггеры,генератор 10 импульсов, первый 11 и второй 2012 формирователи импульсов, сумматор 13и элемент 14 ИЛИ, Вход синхронизации 15устройства соединен с установочным входом триггера 8, Выход микроопераций 16устройства соединен с выходом мажоритарного блока 4 и с выходом информационным блока 5. Выход стробированиямикроопераций 17 устройства соединен свыходом элемента И 6 и с первым входомэлемента ИЛИ 14, Выход 18 ошибки устройства соединен с выходом триггера 9 и синверсным стробирующим входом блока 5.Вход сброса устройства 19 соединен с входом сброса триггера 9, Выходы 20 блоков 3соединены с входами блока 4, Установочный 21 вход устройства соединен с соответствующим входом блока 4. Выходы блока 1соединены с адресными входами всех блоков 3 и с первой группой входов блока 13,Информационные входы второй группы этого блока соединены с выходами информационными блока 2, выход обнуления которогосоединен с третьим входом элемента И 7.Прямой и инверсный выходы блока 5 соединены с первыми входами соответственно 545элементов И 6 и 7, вторые входы которыхобъединены и соединены с выходом блока 12. Выход элемента И 7 соединен сустановочным входом блока 9 и с вторымвходом блока 14. Выход блока 8 соединен 550с управляющим входом блока 10, выход которого подключен к счетным входам блоков1 и 2, к входам чтения блоков 3 и к входамблоков 11 и 12, выход блока 11 подключен квторому (прямому) стробирующему входу55блока 5. Выход блока 13 соединен с информационными входами блока 1, выход элемента 14 - с установочным входом блока 2,с входом сброса блока 8 и со счетным входом блока 1,Мажоритарный блок 4 (фиг.2) содержит группу сумматоров 22, группу устройств сравнения 23 и регистр 24. Информационные входы регистра соединены с установочным 21 входом устройства (среди них есть и синхровход - при необходимости). Выходы сумматоров 22 соединены с первыми группами входов соответствующих устройств сравнения 23, вторые входы которых объединены и соединены с выходом регистра 24. выходы устройств 23 являются выходами блока 4, Выходы каждого сумматора 22 соединены с одноименными разрядными входами блока 4 и с одноименными разрядными выходами блоков 3,Устройство работает следующим образом.В исходном состоянии счетчик адреса 1 занесен адрес первой микрокоманды некоторой программы (например - нулевой), В блоки 3 занесены - в М последовательных смежных ячеек памяти - код очередной микрокоманды (таким образом, в каждом блоке 3 памяти реализуется М-кратное резервирование каждой микрокоманды). Информация, записанная во все блоки 3 памяти, совершенно идентична; таким образом реализуется К-кратное резервирование блоков памяти микрокоманд. В регистр 24 блока 4 занесен код числа К - количества блоков 3. Во второй счетчик 2 занесен код числа й - числа повторений команды в каждом блоке памяти 3. Триггеры 8 и 9 - в нулевом состоянии, Цепи начальной установки на чертежах не показаны, Не выделен также синхровход в составе входов 21 регистра 24, по сигналу с которого число К заносится в этот регистр, Генератор импульсов 10 не формирует импульсов, так как он закрыт сигналом с триггера 8.Работа устройства начинается с подачи тактового импульса на вход 15, Триггер 8 устанавливается в единичное состояние и выдает разрешающий сигнал на генератор 10, который начинает формировать импульсы управления на устройство, Соотношение длительностей импульсов с генератора 10 и формирователей 11 и 12 приведено на фиг,З. Для реализации импульсов такого вида формирователи 11 и 12 могут быть вы полнены в виде последовательно соединенных элемента задержки и одновибратора,Импульс положительной полярности с выхода генератора 10 поступает на счетный вход счетчика 2, работающего в режиме вычитания, и передним фронтом уменьшает его содержимое на единицу, Заметим, что в то время как счетчик 2 работает в режиме вычитания (всегда) и переключается по переднему фронту, счетчик 1работает на сложение и переключается по заднему фронту.Импульс с блока 10 поступает на блоки 11 и 12 и на блоки 3 памяти, которые устанавливаются в режим чтения и выдают на блок 4 коды микрокоманд, записанные в их одноименных ячейках.В мажоритарном блоке 4 одноименные разряды всех блоков памяти соединены с входами соответствующего сумматора 22, в котором формируется код количества единиц, поступающих на его входы, поданному разряду, Если сумма единиц, сформированная на выходе сумматора 22 в виде двоичного кода, равна коду, поступающему с регистра 24 (или в общем случае - равна или больше этого кода, что обеспечивается использованием соответствующего выхода - "Больше или равно" устройства сравнения, или, при наличии в нем раздельных выходов "Больше" и "Равно" - объединением их по "ИЛИ"), с выхода устройства сравнения на выход блока 4 по данному разряду формируется единичное значение сигнала. Это означает, что мажоритарный блок принял решение о наличии единицы в данном разряде. В более общем случае в регистр 24 записывается не число К, а число в пределах от К/2 до К, чем и реализуется мажоритарный принцип работы блока 4, т,е, если большинство значений сигналов с выходов блоков 3 имеют единичное значение, на выходе данного разряда - единичный сигнал, иначе - нулевой, Этот метод позволяет гибко регулировать порог срабатывания мажоритарного блока и таким образом изменять степень жесткости принятия решения при ошибках в отдельных блоках памяти.Выходные сигналы с блока 4 поступают на выход 16 микроопераций - информационный выход устройства и на блок контроля, который совершенно совпадает с блоком контроля прототипа и представляет собой блок проверки информации (естественно, как и в прототипе, предварительно закодированной и в закодированном виде записанной в блоки памяти) на четность или по коду Хемминга, Работа блока контроля синхронизируется импульсом с формирователя 11, поступающим на него с задержкой относительно сигнала с генератора 10 с целью сформирования к моменту его поступления сигналов на шине 16. При верной микрокоманде (по результатам работы блока 4, блок контроля 5 не обнаружено ошибки) на элемент 6 выделяется разрешающий положительный потенциал. При срабатывании (с некоторой задержкой, требующейся для срабатывания блока 5) формирователя 12 импульс с его выхода в данном случае проходит на выход 17 стробирования микроопераций устройства для разрешения приема получателем микрокоманды и через элемент ИЛИ 14 на вход сброса триггера 8 и 5 синхровход счетчика 1, по этому сигналу всчетчик 1 записывается код начальный новой (следующей) команды. Этот код образуется путем суммирования в сумматоре 13 (в случае правильного формирования коман ды в первом такте работы) начального адреса данной команды и числа "-1" из счетчика 2 (вернее, так формируется последний адрес данной команды, однако первый адрес следующей команды формируется в момент 15 окончания тактового импульса, так как поего заданному фронту инкрементируется счетчик 1).Таким образом, и ри правильном формировании очередной микрокоманды в первом 20 же такте она выдается получателю, а устройство переходит в состояние готовности к формированию по следующему синхроимпульсу с входа 15 новой микрокоманды.В том случае когда в первом такте блок 25 контроля выдает сигнал ошибки на инверсный выход, описанных операций не происходит; импульс ошибки также в первом такте не поступает на выход элемента 7, так как он закрыт сигналом нулевого уровня с 30 выхода обнуления счетчика 2, Первый такт,таким образом, является неудачным,Во втором такте происходит то же, чтои в первом, однако по окончании первого такта задним фронтом (спадом) импульса с 35 генератора 10 счетчик 1 переводится в следующий адрес данной микрокоманды.Если второй и последующий такты (кроме последнего) неудачны, устройство работает аналогично описанному, Так же оно 40 работает, если один из тактов, кроме последнего (и последний - тоже), - удачен, При этом в зависимости от номера удачного такта ему соответствует содержимое счетчика 1 и - за счет отсчета счетчиком 2 в обратном 45 направлении - дополнение этого кода допоследнего адреса данной команды; таким образом, на любом удачном такте при принятии решения а правильности команды она выдается, и устройство переходит в ре жим готовности по следующему синхроимпульсу приступить к выдаче следующей команды.В том случае когда все такты выдачиданной команды неудачны, на последнем 55 такте очередное декрементирование счетчика 2 приводит к его обнулению, что вызывает появление единичного потенциала на его выходе обнуления, этот сигнал открывает элемент И 7; если и последний такт (последняя попытка) неудачен, то сигнал1805466 йи.1 Йог. 3 Составитель Ю, Ла Техред М.Моргента в Корректор С. Пекарь едакто Заказ 943 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж, Раушская наб 4/5 Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 10 ошибки с блока 5 проходит через элемент И 7 и устанавливает триггер 9 в единичное состояние, сигнализируя об ошибке при выдаче данной микрокоманды. Этот же сигнал устанавливает устройство вновь в исходное состояние, как описано выше.Сигналом на входе 19 можно, как и в прототипе, устанавливать устройство - его элемент, фиксирующий ошибки - триггер 9 - в исходное состояние.ф о р мул а изобретен ия Устройство микропрограммного управления с контролем, содержащее первый счетчик, первый блок памяти микрокоманд, блок контроля, два элемента И, элемент ИЛИ и два триггера, причем выход первого счетчика соединен с адресным входом блока памяти микрокоманд, выход второго триггера является выходом ошибки устройства и соединен с первым стробирующим входом блока контроля; выход второго элемента И соединен с установочным входом второго триггера, о т л и ч а ю щ е е с я тем, что с целью повышения отказа устойчивости устройства, в него введены Кблоков памяти микрокоманд, мажоритарный блок, два формирователя импульсов, сумматор, второй счетчик и генератор импульсов, причем вход синхронизации устройства соединен с входом запуска-останова генератора импульсов, выход которого соединен со счетными входами первого и второго счетчиков, с входами чтения блоков памяти, с входами первого и второго формирователей импульсов, выход первого формирователя импульсов соединен с вторым стробирующим входом блока контроля, выход второго формирователя импульсов - с первыми вхо дами первого и второго элементов И, вторыевходы которых соединены соответственно с прямым и инверсным выходами ошибки блока контроля, третий вход второго элемента И соединен с выходом признака обну ления второго счетчика, информационныевыходы которого соединены с первой группой входов сумматора, вторая группа входов которого подключена к выходам первого счетчика и адресным входам блоков 15 памяти микрокоманд с второго по (К)-й, авыходы - с информационными входами первого счетчика, синхровход которого соединен с входом сброса первого триггера, установочным входом второго счетчика и 20 выходом элемента ИЛИ, первый вход которого соединен с выходом первого элемента И и является выходом стробирования микроопераций устройства, а второй вход соединен с выходом второго элемента И и 25 установочным входом второго триггера,вход сброса которого является входом сброса устройства, выходы блоков памяти микрокоманд соединены с входами мажоритарного блока, выход которого является 30 выходом микроопераций устройства и соединен с информационным входом блока контроля, установочный вход устройства соединен с соответствующим входом мажоритарного блока.35

СмотретьЗаявка

4873525, 10.10.1990

МОСКОВСКИЙ ИНСТИТУТ ИНЖЕНЕРОВ ГРАЖДАНСКОЙ АВИАЦИИ

КИШЕНСКИЙ СЕРГЕЙ ЖАНОВИЧ, КАМЕНСКИЙ СЕРГЕЙ ВЕНИАМИНОВИЧ, НАДОБНЫХ ЕВГЕНИЙ НИКОЛАЕВИЧ, ХРИСТЕНКО ОЛЬГА ЮРЬЕВНА

МПК / Метки

МПК: G06F 11/00, G06F 9/22

Метки: контролем, микропрограммного

Опубликовано: 30.03.1993

Код ссылки

<a href="https://patents.su/4-1805466-ustrojjstvo-mikroprogrammnogo-upravleniya-s-kontrolem.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления с контролем</a>

Предыдущий патент: Генератор псевдослучайных чисел

Следующий патент: Устройство для обслуживания запросов

Случайный патент: Устройство для дистанционного измерения расхода электроэнергии