Сумматор по модулю чисел ферма

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

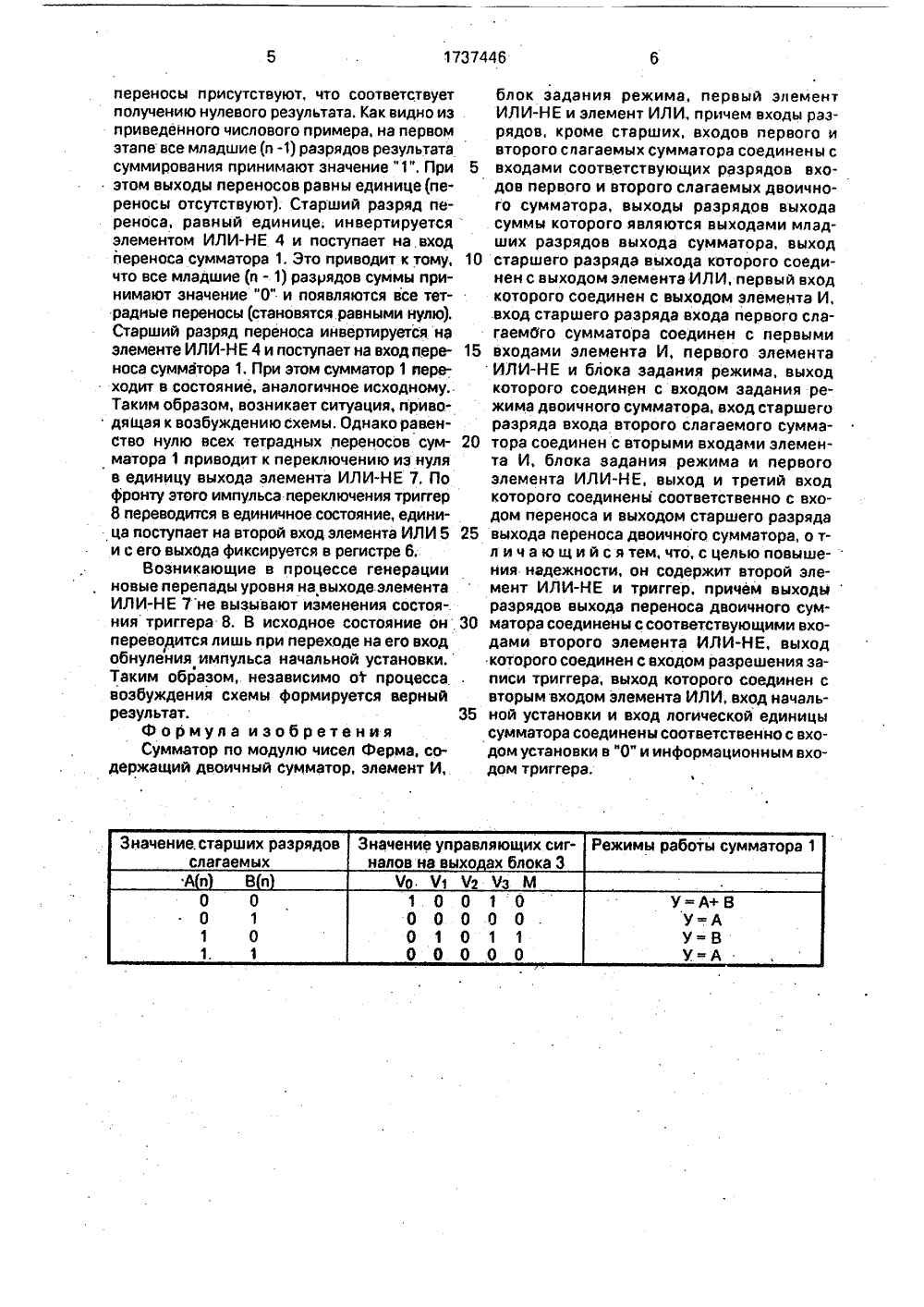

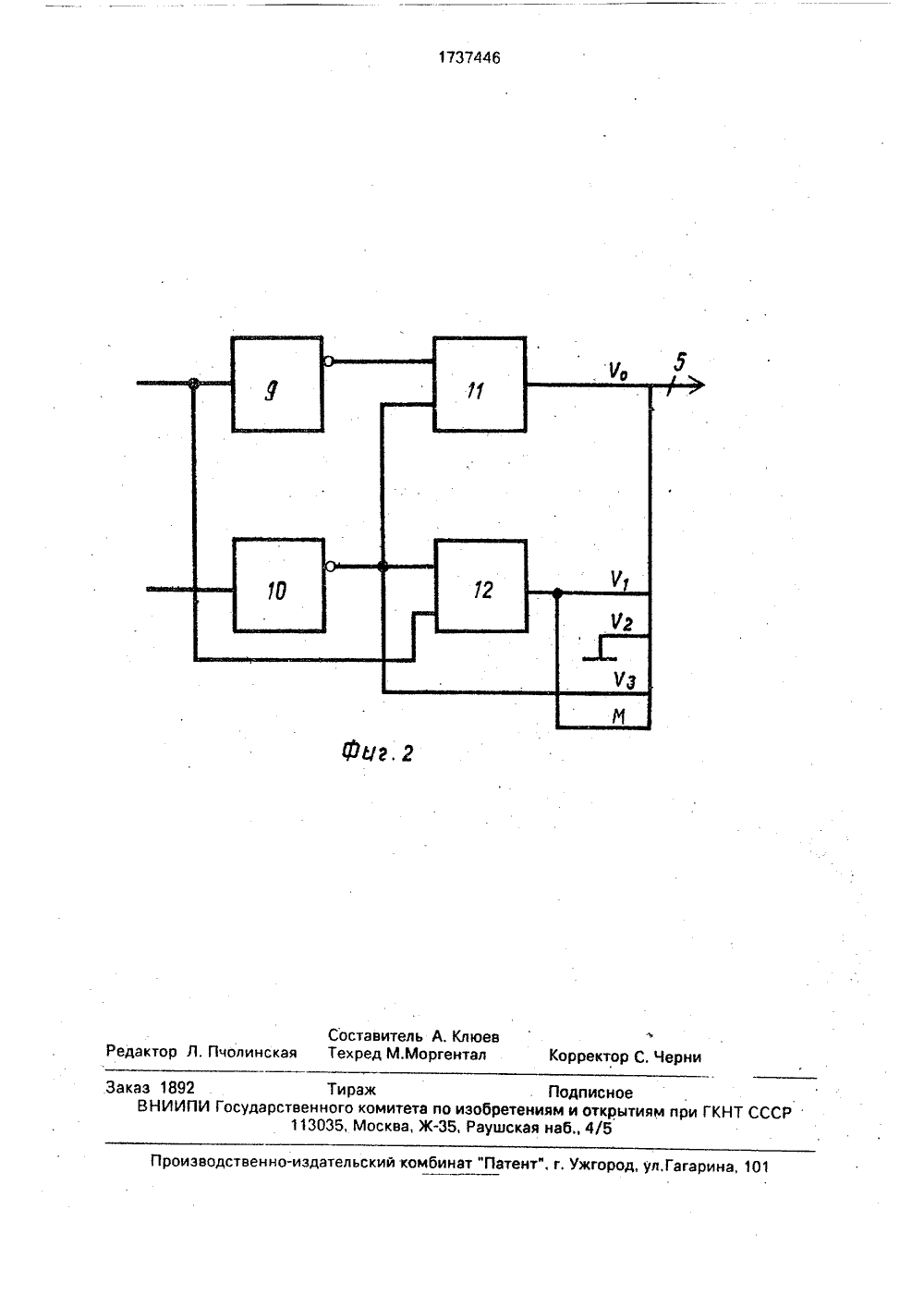

, СОЮЗ СОВЕТСКИХ СОЦИАЛИСТИЧЕСКИХ РЕСПУБЛИК(19) 5 006 Е 7/7 ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИПРИ ГКНТ СССР ОПИСАНИЕ ИЗОБРЕТЕНИ МУ СВИДЕТЕЛЬСТВ К АВТ 2(56) Авторское свидетельство СССРЬ 1251074, кл. 6 06 Р 7/72, 1984.ЕЕЕ Тгапз. Асоцз. Яреесй 8 арпаРгосезз АЗЯР, 1976, р. 216 - 225.(54) СУММАТОР ПО МОДУЛЮ ЧИСЕЛ ФЕРМА(57) Изобретение. относится к вычислительной технике и может быть использовано в устройствах цифровой обработки сигналов, специализированных вычислителях. Целью изобретения является повышение надежности. Сумматор по модулю чисел Ферма содержит двоичнцй сумматор 1, элемент И 2, блок 3 задания режима, первый 4 и второй 7 элементы ИЛИ-НЕ, элемент ИЛИ 5 итриггер 8 с соответствующими связями. которые обеспечивают устранение процесса генерации при равенстве результата нулю(или модула) при ненулевых значениях слагаемых.2 ил., 1 табл.Изобретение относится к вычислительной,технике и радиотехнике и может быть использовано в устройствах цифровой обработки сигналов, специализированных вычислителях,Цель изобретения - повышение надежности.На фиг. 1 представлена схема сумматора по модулю чисел Ферма, на фиг. 2- схема блока задания режима.Сумматор содержит двоичный сумматор 1, элемент И 2, блок 3 задания режима, первый элемент ИЛИ-НЕ 4, элемент ИЛИ 5, регистр 6, второй элемент ИЛИ-НЕ 7 и триггер 8.Блок 3 задания режима состоит из первого 9 и второго 10 элементов НЕ, а также первого 11 и второго 12 элементов И, причем первый вход блока 3 задания режима соединен с первым входом второго элемента И 12 и через первый элемент НЕ 9 с первым вхрдом первого элемента И 11, второй вход блока 3 задания режима соединен через второй элемент НЕ 10 с вторыми входами элементов И 11 и 12, выходы разрядов выхода блока 3 задания режима соединены с выходами элементов И 11 и 12, входом нулевого потенциала сумматора, выходом второго элемента НЕ 10 и выходом второго элемента И 12.В соответствии с правилами выполнения арифметических операций в кольце чи сел по модулю чисел Ферма суммирование двух операндов производится по следующему алгоритму: если старший разряд одного из слагаемых равен единице, то сумме присваивается значение другого слагаемого; если старшие разряды обоих слагаемых равны единице, то сумме присваивается значение нуль и в старший разряд(п) записывается единица; в противном случае сум-, мируются (п - 1) значащих разрядов, дополняется значение переноса и суммиру, ется со значащими разрядами суммы, при этом старший разряд является переносом из последнего значащего разряда.При выполнении суммирования по этому алгоритму может возникнуть ситуация, когда результат суммирования равен нулю (или модулю) при ненулевцх значениях сла гаемых. В этом случае сумматор переходит в режим генерации, период которой определяется временем задержки сигнала нэ элементах внутри микросхем, Этот процесс можно пояснить примером сложения двух чисел в кольце по модулю четвертого числа Ферма Г 4 2+ 1:0 1101 01 00 11 01 00 10+0001010 11 00 10 11 01 11 О 000О ОООО ОО ОО ОО ОООО ОО5,и т.д.Поскольку на последнем этапе суммирования в и-м разряде результата появляется единица, она в инвертированном видепоступает на вход переноса двоичного сум 10 маторэ и цикл операции суммирования повторяется, т.е. сумматор переходит в режимгенерации.Двоичный сумматор 1 обеспечиваетсуммирование двух (и - 1) разрядных опе 15 рандов; Он выполнен по типовой схеме сумматора с ускоренным переносом.Блок 3 задания режима формирует управляющие сигналы для двоичного сумматора 1 согласно таблице.20 Триггер 8 выставляет на выходе едини. цу по положительному фронту импульса,формируемого по наличию всех выходныхпереносов двоичного сумматора 1.Двоичный сумматор 1 может быть реа 25 лизован на микросхемах К 555 ИПЗ иК 555 ИП 4; т.е. имеет инверсные входы и выходы переноса,Сумматор работает следующим образом.30 Когда старшие разряды обоих слагаемых равны единице, на выходе элемента И2 формируется единица, поступающая навход элемента ИЛИ 5. На выходе элементаИЛИ 5 также появляется единица, которая35 фиксируется в регистре 6 по положительному перепаду тактового импульса, что в соответствии с алгоритмом суммированияявляется достаточным признаком нулевогорезультата суммирования. Когда старший40 разряд одного из слагаемых не равен единице, выход элемента И 2 находится в нулевом состоянии, выход элемента ИЛИ-НЕ 4 также в нулевом состоянии, на входе элемента ИЛИ-НЕ 7 присутствуетлибоустойчи 45 вое состояние единицы, либо устойчивоесостояние нуля в зависимости от значенийвыходных переносов сумматора 1, И в той,и в другой ситуации после перевода триггера 8 в исходное состояние нэ его тактовом50 входе нет перепада из одного состояния вдругов, а значит,на выходе триггера 8 сохраняется значение нуля, это приводит к появлению на выходе элемента ИЛИ 5 значениянуля, которое фиксируется в регистре 6 в55 .момент прихода тактового импульса.В случае наличия двух нулевых значе-ний старших разрядов слагаемых возможныдва варианта: либо аналогичный описанному, когда хотя бы один из тетрадных переносов отсутствует, либо когда все тетрадныепереносы присутствуют, что соответствует получению нулевого результата, Как видно из приведенного числового примера, на первом этапе все младшие (и -1) разрядов результата суммирования принимают значение "1". При этом выходы переносов равны единице(переносы отсутствуют), Старший разряд переноса, равный единице, инвертируется элементом ИЛИ-НЕ 4 и поступает на вход йереноса сумматора 1. Это приводит к тому; что все младшие (и - 1) разрядов суммы принимают значение "0" и появляются все тетрадные переносы (становятся. равными нулю). Старший разряд переноса инвертируется на элементе ИЛИ-НЕ 4 и поступает на вход переноса сумматора 1. При этом сумматор 1 переходит в состояние, аналогичное исходному. Таким образом, возникает ситуация, приводящая к возбуждению схемы. Однако равенство нулю всех тетрадных переносов сумматора 1 приводит к переключению из нуля в единицу выхода элемента ИЛИ-НЕ 7. По фронту этого импульса переключения триггер 8 переводится в единичное состояние, единица поступает на второй вход элемента ИЛИ 5 и с его выхода фиксируется в регистре 6.Возникающие в процессе генерации новые перепады уровня на выходе.элемента ИЛИ-НЕ 7 не вызывают изменения состояния триггера 8. В исходное состояние он переводится лишь при переходе на его вход обнуления импульса начальной установки. Таким образом, независимо о 1 процесса. возбуждения схемы формируется верный результат.Формула изобретения Сумматор по модулю чисел Ферма, содержащий двоичный сумматор, элемент И,блок задания режима, первый элементИЛИ-НЕ и элемент ИЛИ, причем входы разрядов, кроме старших, входов первого ивторого слагаемых сумматора соединены с5 входами соответствующих разрядов входов первого и второго слагаемых двоичного сумматора, выходы разрядов выходасуммы которого являются выходами младших разрядов выхода сумматора. выход10 старшего разряда выхода которого соединен с выходом элемента ИЛИ, первый входкоторого соединен с выходом элемента И,вход старшего разряда входа первого слагаембго сумматора соединен с первыми15 входами элемента И, первого элементаИЛИ-НЕ и блока задания режима, выходкоторого соединен с входом задания режима двоичного сумматора, вход старшегоразряда входа второго слагаемого сумма 20 тора соединен с вторыми входами элемента И, блока задания режима и первогоэлемента ИЛИ-НЕ, выход и третий входкоторого соединены соответственно с входом переноса и выходом старшего разряда25 выхода переноса двоичного сумматора, о тл и ч а ю щи й с ятем, что, с целью повышения надежности, он содержит второй элемент ИЛИ-НЕ и триггер. причем выходыразрядов выхода переноса двоичного сум 30 матора соединены с соответствующими входами второго элемента ИЛИ-НЕ, выходкоторого соединен с входом разрешения записи триггера, выход которого соединен свторым входом элемента ИЛИ, вход началь 35 ной установки и вход логической единицысумматора соединены соответственно с входом установки в "0" и информационным входом триггера,1737446 Пчолинс Коррек Реда кто ерни акэз 1892 Тираж ВНИИПИ Государственного комитета по изоб 113035, Москва, Ж, Рауоизводственно-издательский комбинат "Патент", г. Ужгород, ул.Гага Сост Техр ль А. КлюМоргентал Подписноетениям и открытиям при ГКНТ СССкая наб 4/5

СмотретьЗаявка

4730453, 18.08.1989

ПРЕДПРИЯТИЕ ПЯ А-1772

ЗАХАРОВ ЮРИЙ ИВАНОВИЧ, ОНОКОВ ИГОРЬ ВИКТОРОВИЧ

МПК / Метки

МПК: G06F 7/72

Метки: модулю, сумматор, ферма, чисел

Опубликовано: 30.05.1992

Код ссылки

<a href="https://patents.su/4-1737446-summator-po-modulyu-chisel-ferma.html" target="_blank" rel="follow" title="База патентов СССР">Сумматор по модулю чисел ферма</a>

Предыдущий патент: Генератор линейно зависимых и независимых случайных двоичных кодов

Следующий патент: Устройство для подключения абонентов к общей магистрали

Случайный патент: Способ получения смеси бисфенолов