Устройство для вычисления модуля разности двух чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

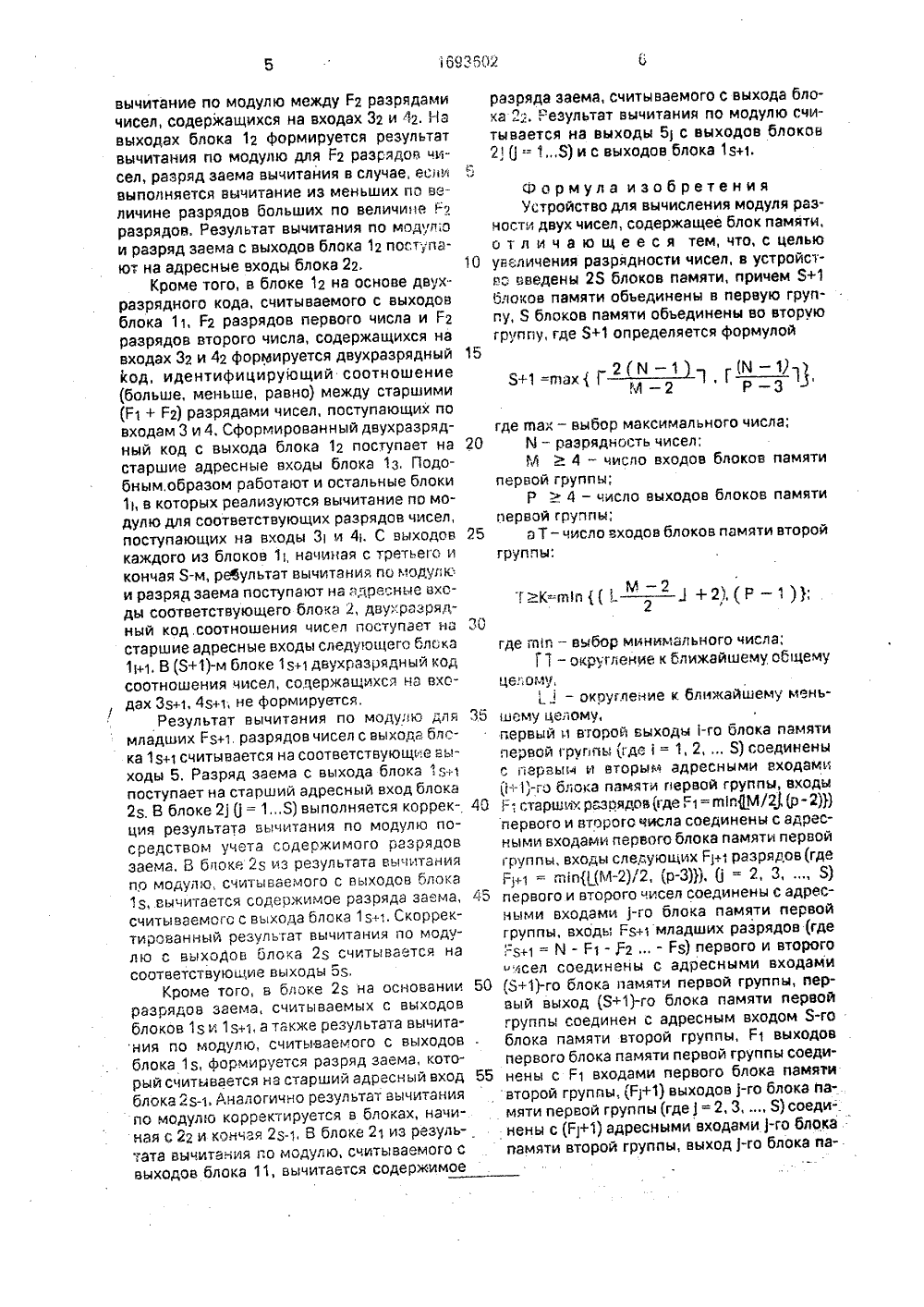

ЕТЕЛЬСТВУ ВТОРСКОМУ Кучеренк ство СССР 50, 1986.БИС запоминаю- . А,Ю, Гордонова и ио и связь, 1986,О ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР ИСАНИЕ И(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ МОДУЛЯ РАЗНОСТИ ДВУХ ЧИСЕЛ(57) Изобретение относится к вычислительной технике и может быть использовано при построении специализированных вычислительных систем для обработки информации в реальном масштабе времени, Цель изобретения - увеличение разрядности чисел, для которых возможно выполнение операции определения модуля разности. В состав устройства входят блоки 11-1 з+1 памяти, объединенные в первую группу, и блоки 21 - 2 з памяти., обьединенные во вторую группу. 1 ил.) Азобреение ОТНОСИ Гя ( ВЬ)ИСИТ 8 ЛЬ" ной техник 6 и мОжет быть спол 3)ванО при ЙОСТР 08 НИИ Спе)5 йа)ИЗИР 5:ВН( ВЬ)ЧИСЛИ" тйльных систем Для Обра:От,(и Р)нфо)мации В реальнОм масштабе Вре:еьи,Цеть изобр 9 тениЯ - у)58) )ценив ьаз)рядНос)И ЧИС 8 Л,На чертеже по(аза нэ б)05("01(ема Грзд" .лагаемОГО устройстваУст 5)ОЙство для Вычисл 8 ния мОдуля раз" ности двух чисел содержит первуго группу из Я+1) блоков 11 - 18+1 памяти и втору)о Группу из Я блоков 21 - 2 Я Г)ам)т, Входь 31 - 33+41 - 43+1 Г)8 рВОГО )1 ВТОрого ЧИСВЛ, Вы"ОДЫ ")1- .) РЕЗУЛ ") 2 И - 1 ), . 1 - 1=+1)=гпах- ) -- . - :-М 25) 3 ГД 6 процедура ьяа:( Означа(т вьбор ь)акс 1 мах)ьного числа;М - разрядность ци;.ел, содержащих наВхДах 3 и 4Д4 . число В.О)у , ж.р-О )г,КОВ 1;Р Я: 4 - число Вьь(бдов (аждОГО йзбЛОКОВ 1.ИС)0 Ь 0 ЦОВ ) КсА 4.- О ) )" "фа" Р- НРДе), ЧИ ЛО ЗР ОВ дДО ( лзблоков 2 щльве или равиО ) -ь,=01)П 1 - : - , - - -"5 Гд.", Г)роцедурз Гя) Оз Чает 55;.б "о , ).и- мальнОГО чиса. С:,Об1) 85 ачак)1 (к ругление дробного ч":" 58 х ).5 Вф)д,.большему .елому числу, С)(с)бсиО: ачагот Оклу.)8 ь)ие драЬН).числа к л.:)са:,- ИВМУ М 8 НЬШ 6 МУ ЦеяИЛУ ЧСЛУ., ",Ра ВЫХОДЗ кажДОГО из Олг)к 08 1 начиная Г, ОЛОка )" и КОнчая )локом 28, сойи:6 ы с Двумя ст:." )НИМИ аРС)М, Вх;:ЗЛИ П(СЛВКЩИ блОкОВ , ),")Ходы 3 Первого исла и Входь 4 ВторОГО чисх 5 а ( == 1, .3+1) сс 58 Ди-зн с ЗД)8 СНЫИИ ВХОдами бЛОКОВ 1 Ь )Ри)8 ВХО" Дц 1 " 41 -арши) - = тп(1"( р - Т разрядов первого и втОро О числ соед;не ны с адресньми аховами п 8 рвОГО блОка 11 памяти, Входы 32 и 42 сладукдих Е; -. =ГП 1 пйМ - 2)/2) (р3 т ра 5 Г)5 Д в з:Ового и ВТОРОГО Чиоел СОВДИН 6) С ВДР)СНЬМ)И вхо-Дами второго бло (а 12, Б хсДы,Зз и 4 з пос )8- ду,ощих г з.= Гл)ПАЕМ - ,)1 2, 5,р 3 разрядо; Й 8 РВОГО И ВТОРОГО ЧИСВЛ "08 ДИНВНЫ С с)Д,)Вснь)ми ВхОДами третьеГО блОка 1, ходь 3 з+1 48+1 -8+1 =- ) - .2 --з) ь)ла;:.Вих : раэрядОВ первого и В)щОГО чисел соеди 16" ны с аДр 8 сными ВхОЦВМИ Я + ")-ГО блОка 1,Один выход каждого блока 2), нач "НЗЯ с второго блока 22 и кончал 2 Я-М, соединен со старшим дцресным ВхОдОм поеды;.шеГО блока 2. Один выход (Я + 1)-го блока 1 З+ с 08 Динен со старшим ВДр 8 сным вхОДОМ блока 2 Я. Р 1 выходов первого блока 1 соединены с -1 адресными входами блока 21, Г 2+ 1) выходов блока 12 соединены с 5,Г 2+ 1) адресными входами блока 22, , .ВЧ 1) вьходов Я-го блока 1 з саадине)ы с,гз+1) адресными входами бло(а 8 ,1 выходов блока 21 ):2 РыхОДОВ блока 22,-.3 ВцхОДОВ Олока 2 з а также Гз+1 ВЫКОДОВ блока3+1 ЯвлякпсЯ Выходами 5 устройства,В качестве блоков памяти ;:, - . 2 Можно использовать серийно выг)ускаемые микро"ъ ТО ГЦ Х За Миф) ЩИУСТ роистР 51 1 у) напри)ер сГии 56 Для ТОГО)тобы 6 ьч(лОаща Рыхоах ПЗУ ДОПОЛНИТ 8 ЛЬНЫ 6 РЕЗИСТОРЫ, СЛВДУ 8 Т ИСпользовать Д 3) с тристабил),чц)1 и выходамив случад использования ПЗ) с выходами в Риде Открытого коллектора требуется вкл 5 оцить допол нительные резисторы).УстОЙство для Вьчисл 8 ния модуля разости двух цисел работае следу)ОЩим ОбраП дБлокреализу 8 т операцик) Вычитания 50 )О 1;,ЛстаоВ)5 Х -1 РЗЗРДОВИСЕЛ поступ эх)щих на соо ветствук)щле входы 31 и 4), Результат ОГ)8 ра.,Ии вычитанлЯ с выхоДов б 50, а ",по(тугае на а)зеснце входы Олока,.:. )Гоме ТОГО, )лок 1, фогИиоуе двухпазряд ьЧ 1 код, идентифи Ир)0 иЯ соО-:-цос)НИВ 0.,Ве. МВНЬШ, Раенс МежДУ СТВРШИЮ(аЗРЯ 1 И ЧИ(;ел, ГОСТУПВ)0",ПОГГТ РЯУ 5,Ь),ОД . .,). И .ф.5, С)ОР).0 еа)НЫИ ДсЗРЯДы КОД С ВЫ хода блз(а 11 ГОстуг эе на ста;шие аДреснь 58 входы блока 12, БЛОХ 12 реализу 8 т пперацик) Вцци Ган,5 я ",О мод 50 для следу;Оших Г 2 Зарядов цис 6 л, поступа)ощих по В" Оам 3 4РИИ ОПВРВОИЯ ВЬЧИТВНИЯ По МГ)ДлК) В ОК 6 )2 ВЫ;ОлнйеТ 5 СчеТОМ соотношения между "Гаршими Г разряда ми чис л, с)део)каихся ),а входах 31 и 4 Если двухрззрЯ,;ны код Гоступая с выхода блока ";На ста,"вшие адресные РхОДЫ Олока 12 Определяет, что старшие 5-1 разряды числа на в:",ОД 8 31 больше сарших Г разрЯДОВ числа на входе 4;, то в блоке 12 выполняется вычитание из Г разрядов числа на входе 32 -2 ОазрЯдсв числа на входе 42. Если старшие Г; разрядов числа на входе 31 меньа 8 стар- )5 их Е 1 р;зрЯдов .числа на входа 4 т то в блоке 12 выполняетсЯ вычитание из г 2 разрядов числа на ьходе 42 "2 разряДОВ числа на Входе 32.сли старшие 1 разрЯДОВ числа на входе 31 равны старшим )-1 разрядам числа на входе 41, то в блоке 12 вцполняетсявычитание по модулю между Е 2 разрядамичисел, содержащихся на входах 32 и 42. Навыходах блока 12 формируется результатвычитания по модулю для Е 2 разрядов чисел, разряд заема вычитания в случае, если 5выполняется вычитание из меньших по величине разрядов больших по величине Е 2разрядов. Результат вычитания по мод,л,:ои разряд заема с выходов блока 12 поступают на адресные входы блока 22, 10Кроме того, в блоке 12 на основе двухразрядного кода, считываемого с выходовблока 11, Е 2 разрядов первого числа и Е 2разрядов второго числа, содержащихся навходах 32 и 42 формируется двухразрядный 15код, идентифицирующий соотношение(Е 1+ Е 2) разрядами чисел, поступающих повходам 3 и 4. Сформированный двухразрядный код с выхода блока 12 поступает на 20старшие адресные входы блока 1 з Подобным,образом работают и остальные блоки1 ь в которых реализуются вычитание по модулю для соответствующих разрядов чисел,поступающих на входы 3 и 4 ь С выходов 25каждого из блоков 11, начиная с третьего икончая Я-м, ребультат вычитания по модулюи разряд заема поступают на ядре:ные входы соответствующего блока 2, двухразрядный код.соотношения чисел поступает на 30старшие адресные входы следующего блока11+1. В (5+1)-м блоке 1 з+1 двухразрядный кодсоотношения чисел, содержащихся на входах 38+1, 48+1, не формируется,Результат вычитания по модулю для 35младших Ез+1. разрядов чисел с выхода блока 1 з+1 считывается на соответствующие вь 1 ходы 5. Разряд заема с выхода блока 1 з+1поступает на старший адресный вход блока2 з. В блоке 2 ( =1.5) выполняется коррекция результата вычитания по модулю посредством учета содержимого разрядовзаема. В блоке 2 з из результата вычитанияпо модулю, считываемого с выходов блока1 з,.вычитается содержимое ргзояда заема, 45считываемого с выхода блока 1 з+1. Скорректированный результат вычитания по модулю с выходов блока 2 з считывается насоответствующие выходы 5 з,Кроме того, в блоке 2 з на основании 50разрядов заема, считываемых с выходовблоков 1 з и 1 з+1, а также результата вычитания по модулю, счить ваемого с выходов .блока 1 з, формируется разряд заема, который считывается на старший адресный вход 55блока 2 з. Аналогично результат вь 1 читанияпо модулю корректируется в блоках, начиная с 22 и кончая 2 з, В блоке 21 из результата вычитания по модулю, считываемого свыходов блока 11, вычитается содержимое разряда заема, считываемого с выхода блока 2.:. Результат вычитания по модулю считывается на выходы 5 с выходов блоков 2== 1,3) и с выходов блока 18+1.Формула изобретения устройство для вычисления модуля разности двух чисел, содержащее блок памяти, о т л и ч а ю щ е е с я тем, что, с целью увеличения разрядности чисел, в устройство введены 23 блоков памяти, причем 5+1 блоков памяти обьединены в первую группу, Я блоков памяти объединены во вторую группу, где 3+1 определяется формулой( г 2 мй - 1)1М - 2Р - 3где аах - выбор максимального числа;Н - разрядность чисел;М4 - число входов блоков памяти первой группы;Р4 - число выходов блоков памяти первой группы;а Т - число входов блоков памяти второй группы:Гк=п 1 и ,." .3 +2), (Р - 1;где гп и - выбор минимального числа;1 - округление к ближайшему общему целому,- окоугление к ближайшему меньшему целому,первый и второй выходы 1-го блока памяти первой группы (где 1= 1, 2, .Я соединены с первым и вторым адресными входами (+1,-го блока памяти первой группы, входы Е 1 старших разрядов(где Е 1= п 1 п 94/2(рпервого и второо числа соединены с адресными входами первого блока памяти первой группы, входы следующих Е 1+1 разрядов(где Е 1+1 =- гппЯМ)/2, (р-З, О = 2, 3, , 5) первого и второго чисел соединены с адресными входами )-го блока памяти первой группы, входы Ез+1 младших разрядов (где ,-3+1 = Й - Е 1 Р 2,. - ЕЯ) пЕрвОгО и втОрОгО1 сел соединены с адресными входами (5+1)-го блока памяти первой группы, первый выход (3+1)-го блока памяти первой группы соединен с адресным входом Я-го блока памяти второй группы, Е 1 выходов первого блока памяти первой группы соединены с Е 1 входами первого блока памяти второй группы, Я+1) выходов )-го блока йа- . мяти первой группы(где =2,3, Я) соеди-. нены с (Е+1) адресными входами )-го блока памяти второй группы, выход )-го блока па/Заказ 4078 Тираж ПодписноеВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР113035, Москва, Ж, Раушская наб., 4/5 Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 мяти второй группы соединен со старшим адресным входом О)-го блока памяти вто, рой группы, Г; выходов -го блока памяти второй группы и Ез+1 выходов(3+1)-го блокапамяти первой группы соединена с выходами устройства.

СмотретьЗаявка

4602002, 04.11.1988

Ю. А. Ганушкин, К. И. Кучеренко и А. В. Никити

ГАНУШКИН ЮРИЙ АЛЕКСАНДРОВИЧ, КУЧЕРЕНКО КОНСТАНТИН ИВАНОВИЧ, НИКИТИН АНДРЕЙ ВЛАДИМИРОВИЧ

МПК / Метки

МПК: G06F 7/50

Метки: вычисления, двух, модуля, разности, чисел

Опубликовано: 23.11.1991

Код ссылки

<a href="https://patents.su/4-1693602-ustrojjstvo-dlya-vychisleniya-modulya-raznosti-dvukh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления модуля разности двух чисел</a>

Предыдущий патент: Конвейерное вычислительное устройство

Следующий патент: Анализатор функций плотности распределения

Случайный патент: Вертикальный центробежный насос для перекачивания высокотемпературных жидкостей