Устройство для анализа логических состояний микропроцессорных систем

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

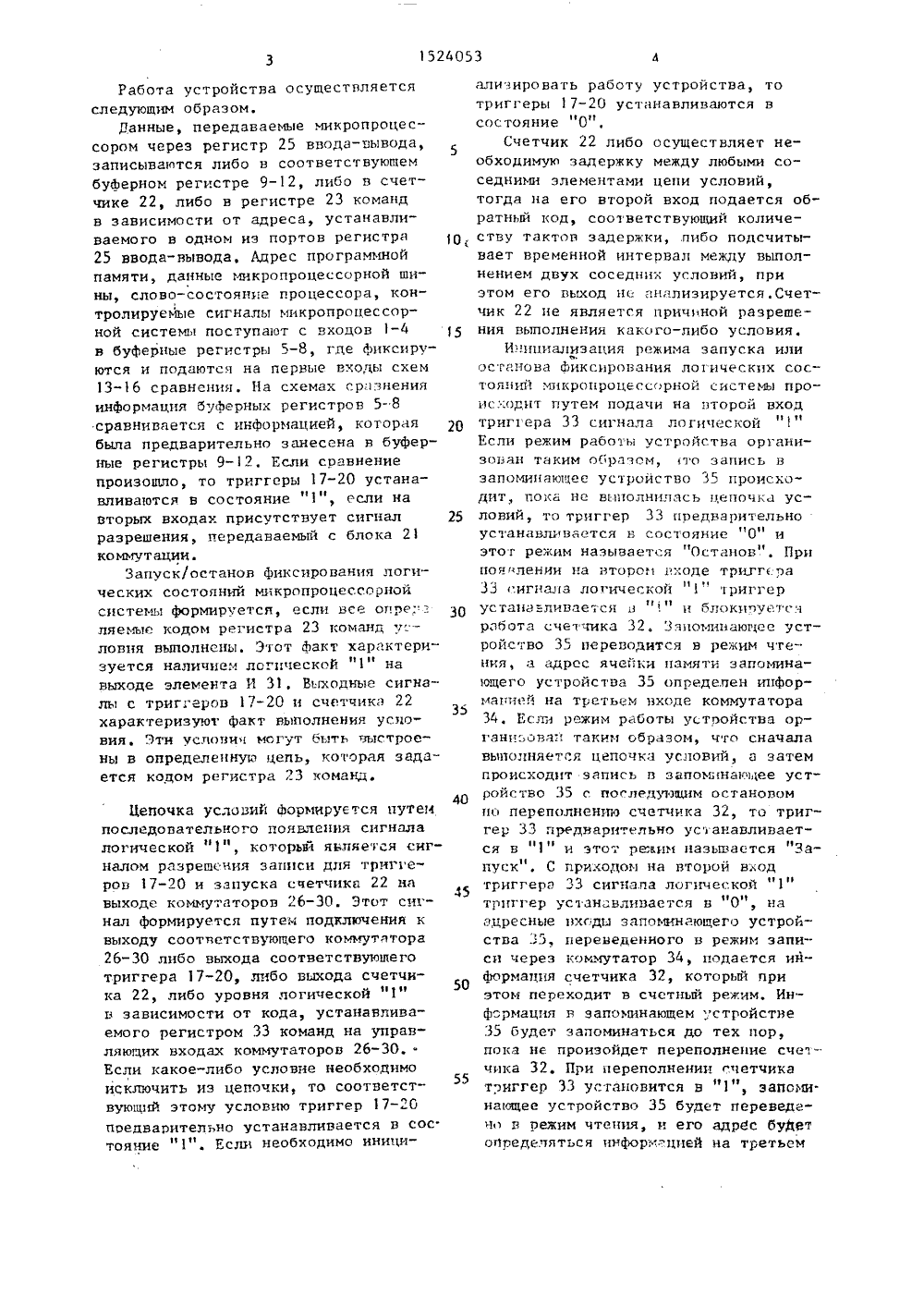

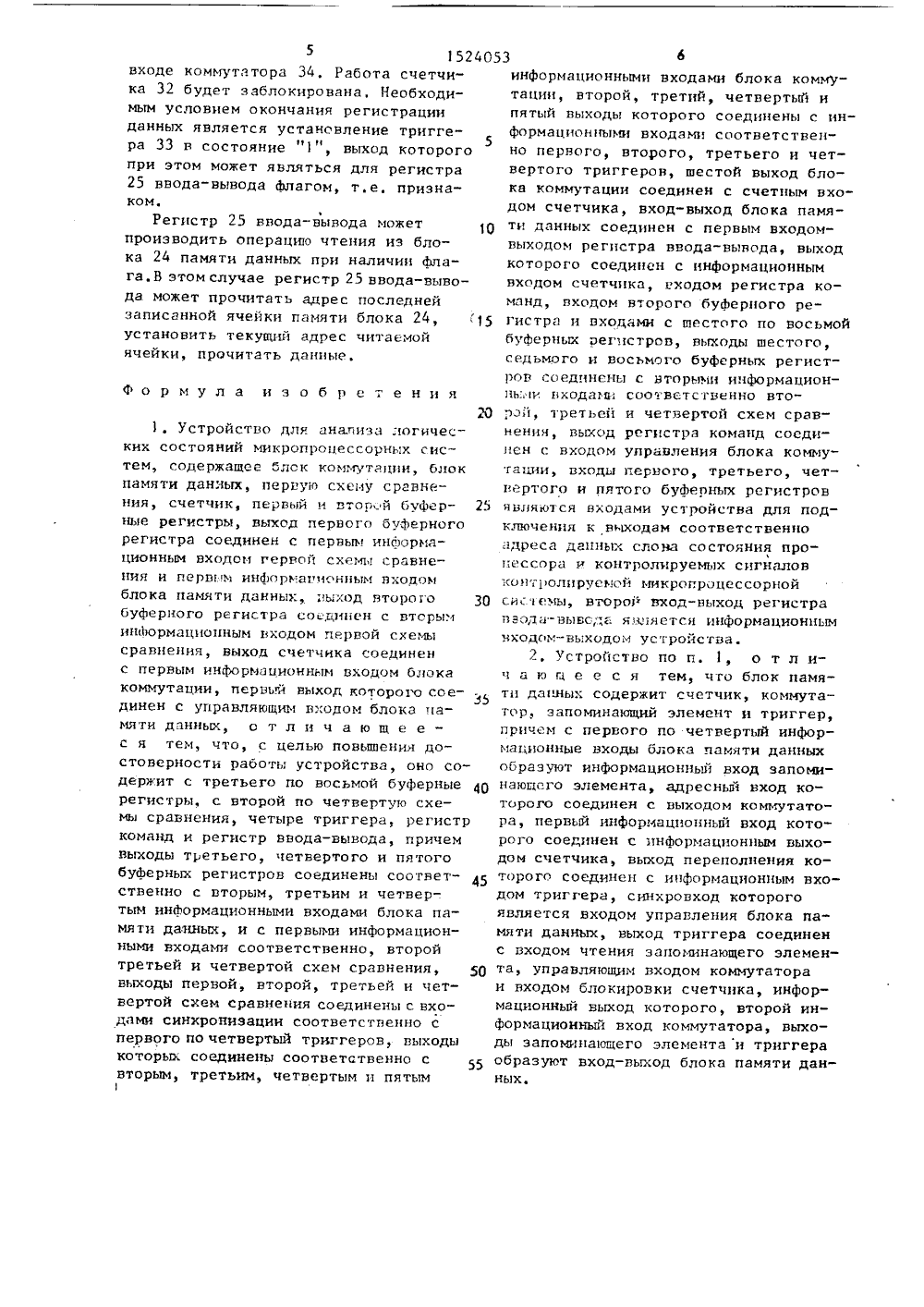

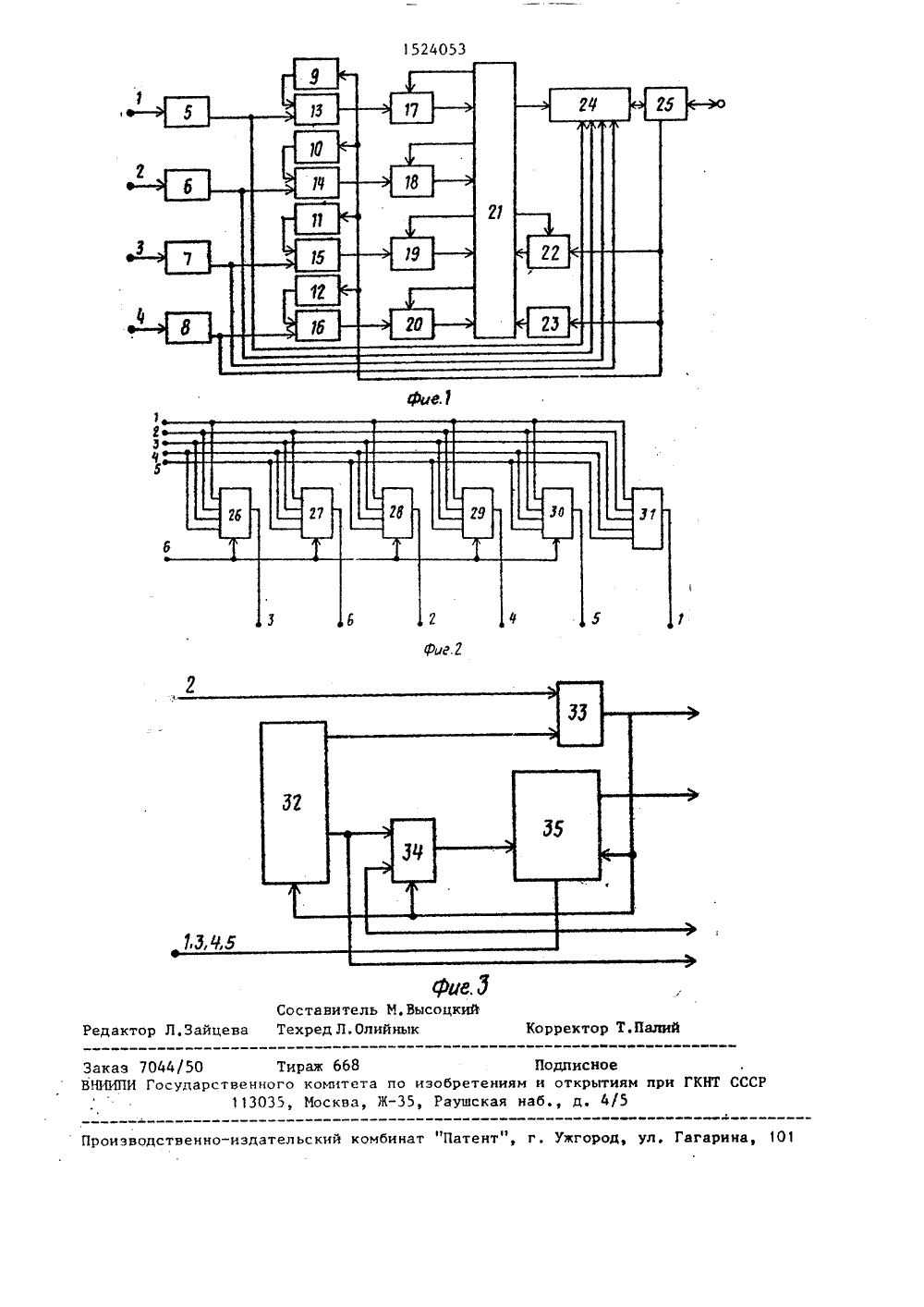

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК И 91 (11) А 1 50 4 С 06 Г 11/00 ОСУДАРСТВЕННЫО ИЗОБРЕТЕНИЯРИ ГКНТ СССР КОМИТЕТОТКРЫТИЯМ ПИСАНИЕ ИЗОБРЕТЕНИ К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ ско-техации тяудованияаков СССР1984. ЛОГИЧЕСНЫХ СИСсь и от я контрх систе ль Цель зобре- верноислительн ия являет овышение до т сьмой2 буферные ре, вторую 14, третью 16 схемы сравнения, ой 18,третий 19 и четгеры, блок 21 коммутарегистр 23 команд, данных, регистр 25 седьмой 11 и вогистры первую15 и четвертуюпервый 17, вторвертый 20 тригции, счетчик 22блок 24 памятиввода-вывода,Блок коммутации (фиг, 2) сопервый 26, второй 27, третий 2вертый 29, пятый 30 коммутаторэлемент И 31.Блок памяти (фиг, 3) содержсчетчик 32, триггер 33, коммут34, запоминающее устройство 35 зобрете тносится к вычис и может быть исп ник но онтроля и отладки ва держит8, четор ды тый(71) Специальное конструктнологическое бюро автоматижелого металлорежущего обо(54) УСТРОЙСТВО ДЛЯ АНАЛИЗ КИХ СОСТОЯНИЙ МИКРОПРОЦЕСС ЕМ57) Изобретение относится кительной технике и может бь лительных систем.Цель изобретения - повьшение достоверности работы устройства.На фиг. 1 представлена структурнасхема устройства для анализа логических состояний микропроцессорных систем; на фиг. 2 - структурная схемаблока коммутации; на фиг. 3 - структурная схема блока памяти,Устройство (фиг. 1) содержит вхо 1-4, первый 5, третий 6, четвер 7, пятый 8, второй 9, шестой 10,сти работы устройства. Устройство содержит восемь буферных регистров, четыре схемы сравнения, четыре триггера, блок коммутации, счетчик, регистр команд, блок памяти данных, регистр ввода-вывода, Данные микропроцессора через регистр ввода-вывода запоминаются или на буферных регистрах, или на счетчике или на регистре команд в зависимости от кода управления на регистре ввода-вывода, Адрес программной памяти, данные микропроцессорной шины, слово-состояние процессора, контролируемые точки микропроцессорной системы также запоминаются на буферных регистрах, На схе- аЮ мах сравнения сравнивается содержимое буферных регистров. При наличии факта сравнения и наличия разрешения с блока коммутации на триггерах запоминается этот факт. 1 э.п. ф-лы, 3 ил.Работа устройства осуществляетсяследующим образом,Данные, передаваемые микропроцессором через регистр 25 ввода-вывода,записываются либо в соатветствуюшембуферном регистре 9-12, либо в счетчике 22, либо в регистре 23 командв зависимости от адреса, устанавливаемого в одном из портов регистра25 ввода-вывода, Адрес программнойпамяти, данные микропроцессорной шины, слово-состояние процессора, контролируемые сигналы микропроцессорной системы поступают с входов 1-4в буферные регистры 5-8, где фиксируются и подаются на первые входы схем13-16 сравнения, На схемах сравненияинформация буферных регистров 5-8сравнивается с информацией, котораябыла предварительно занесена н буферные регистры 9-12, Если сравнениепроизошло, то триггеры 17-20 устанавливаются в состояние , если навторых входах присутствует сигналразрешения, передаваемый с блока 21коммутации.Запуск/останов Фиксирования логических состояний микропроцессорнойсистемы формируется, если все опре,": -ляемые кодом регистра 23 команд условия выполнены. Этот факт характеризуется наличием логической "1" навыходе элемента И 31, Выходные сигналы е триггеров 17-20 и счетчика 22характеризуют факт выполнения усповия, Этн условия могут быть выстроены в определенную цепь, которая задается кадом регистра 23 команд,Цепочка условий формируется путем последовательного появления сигнала логической "1", которьв является сигналом разрешения записи для триггеров 17-20 и запуска счетчика 22 на выходе коммутаторов 26-30. Этот сигнал формируется путем подключения к выходу соответствующего коммутатора 26-30 либо выхода соответствующего триггера 17-20, либо выхода счетчика 22, либо уровня логической "1" в зависимости от кода, устанавливаемого регистром 33 команд на управляющих входах коммутаторов 26-30, Если какое-либо условие необходимо исключить из цепочки, та соответствующий этому условию триггер 17-20 паедварительно устананливается в сос. таяние "1", Если необходимо иници 10 15 20 25 30 35 40 45 50 ализировать работу устройства, то триггеры 17-20 устанавливаются в состояние0".Счетчик 22 либо осуществляет необходимую задержку между любыми соседними элементами цепи условий, тогда на его второй вход подается обратный кад, соответствующий количеству тактов задержки, .либо подсчитывает временной интервал между выполнением двух соседних условий, при этом его выход не нализируется.Счетчик 22 не является причиной разрешения выполнения какого-либо условия.Инициализация режима запуска или осганова фиксирования логических состояний микропроцессорной системы происходит путем подачи на второй вход триггера 33 сигнала логической "1" Если режим работы устройства организован таким образам, гто запись в запоминающее устройство 35 происходит, пока не выполнилась цепочка условий, то триггер 33 предварительно устанавливается в состояние "0" и этог режим называется "Останов". При паяцлении на второгг входе триггера 33 сигнала логической "1" триго ер устаианливае-ся ви блокичуетсз работа счетчика 32, Ззпоггинающее устройство 35 переводится н режим чтения, а адрес ячейки памяти запоминающего устройства 35 определен ипфорг 1 аг 1 ией на третьем входе коммутатора 34, Если режим работы устройства органп.овал таким образом, что сначала выполняется цепочка условий, а затем происходит запись в запоминающее устройство 35 с последующим астаноном по переполнению счетчика 32, та триггер 33 предварительно устанавливается в "1" и этот ров.им называется "Запуск, С приходом на второй вход триггера 33 сигнала логической "1" триггер устанавливается в "01, на ацресные входы запоминающего устройства 35, переведенного в режим записи через комутатор 34, падается ийформагпгя счетчика 32, который при этом переходит в счетный режим, Инф"рмация в запоминающем:стройстве 35 будет запоминаться до тех пор, пока не произойдет переполнение счетчика 32. При переполнении счетчика триггер 33 установится в "1" запоми. нающее ус.тройство 35 будет переведен н режим чтения, и его адрес бу 1 ет определяться информацией на третьем5 15240 входе коммутатора 34. Работа счетчика 32 будет заблокирована. Необходимым условием окончания регистрации данных является установление триггера 33 в состояние 1, выход которого при этом может являться для регистра 25 ввода-вывода флагом, т.е. признаком.Регистр 25 ввода-вывода может1 производить операцию чтения из блока 24 памяти данных при наличии Флага. В этом случае регистр 25 ввода-вывода может прочитать адрес последней записанной ячейки памяти блока 24, 15 установить текущий адрес читаемой ячейки, прочитать данные. 53 бннформационнымн входами блока коммутации, второй, третий, четвертый ипятый выходы которого соединены с инФормационными входами соответственно первого, второго, третьего и четвертого триггеров, шестой выход блока коммутации соединен с счетным входом счетчика, вход-выход блока памяти данных соединен с первым входомвыходом регистра ввода-вывода, выходкоторого соединен с информационнымвходом счетчика, входом регистра команд, входом второго буферного регистра и входами с шестого по восьмойбуферных регистров, выходы шестого,седьмого и восьмого буферных регистров соединены с вторыми информационнь:,и; ходами соответственно второй, третьей и четвертой схем сравнения, выход регистра команд соедимен с входом управления блока комму 201. Устройство для анализа логических состояний микропроцессорных систем, содержащее блок коммутации, блок памяти данных, первую схему сравнения, счетчик, первый и втор й буфер ные регистры, выход первого буферного регистра соединен с первым информационным входом гервой схемы сравнения и первь и инфорл апис нныл 1 входом блока памяти данных, выход второго буферного регистра соединен с вторым информационным входом первой схемы сравнения, выход счетчика соединен с первым информационным входом блока коммутации, первый выход которого сое 35 динен с управляющим входом блока памяти данных, о т л и ч а ю щ е е - с я тем, что, с целью повьппения достоверности работы устройства, оно содержит с третьего по восьмой буферные 4 О регистры, с второй по четвертую схемы сравнения, четыре триггера, регистр команд и регистр ввода-вывода, причем выходы третьего, четвертого и пятого буферных регистров соединены соответ ственно с вторым, третьим и четвертым информационными входами блока памяти данньи, и с первыми информационными входами соответственно, второй третьей и четвертой схем сравнения, 5 О выходы первой, второй, третьей и четвертой схем сравнения соединены с входами синхронизации соответственно с первого по четвертый триггеров, выходы которых соединены соответственно с вторым, третьим, четвертым и пятым 1 Формула изобретения тации, входы первого, третьего, четвертого и пятого буферных регистров являются входами устройства для подключения к выходам соответственно адреса данных слона состояния пропессора и контролируемых сигналов контролируелэй микропроцессорной системы, второй вход-выход регистра ввода-вывода является информационным входсм-вь:ходом устройства.2, Устройство по и. 1, о т л ич а ю щ е е с я тем, что блок памяти данных содержит счетчик, коммутатор, запоминающий элемент и триггер, причем с первого по четвертый информационные входы блока памяти данных образуют информационньп вход запоминающего элемента, адресный вход которого соединен с выходом коммутатора, первый информационньп вход которого соединен с информационным выходом счетчика, выход переполнения которого соединен с информационным входом триггера, синхровход которого является входом управления блока памяти данных, выход триггера соединен с входом Чтения запоминающего элемента, управляющим входом коммутатора и входом блокировки счетчика, информационный выход которого, второй инФормационньп вход коммутатора, выходы запоминающего элемента и триггера образуют вход-выход блока памяти данных.1524053 Составитель М,Высоцкийктор Л.Зайцева Техред Л,Олийнык Корректор Т.Палий Заказ 7044/50 Тираж 668 ПодписноеНИИПИ Государственного комитета по изобретениям и открытиям113035, Москва, Ж, Раушская наб д, 4/5 и ГКНТ ССС Производственно-издательский комбинат "Патент", г, Ужгород, ул. Гагарина, 1 О

СмотретьЗаявка

4277252, 06.07.1987

СПЕЦИАЛЬНОЕ КОНСТРУКТОРСКО-ТЕХНОЛОГИЧЕСКОЕ БЮРО АВТОМАТИЗАЦИИ ТЯЖЕЛОГО МЕТАЛЛОРЕЖУЩЕГО ОБОРУДОВАНИЯ

ВЫСОЦКИЙ МИХАИЛ ЛЕОНИДОВИЧ, РЕЗАКОВ АЛЕКСАНДР АЛЕКСЕЕВИЧ

МПК / Метки

МПК: G06F 11/00

Метки: анализа, логических, микропроцессорных, систем, состояний

Опубликовано: 23.11.1989

Код ссылки

<a href="https://patents.su/4-1524053-ustrojjstvo-dlya-analiza-logicheskikh-sostoyanijj-mikroprocessornykh-sistem.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для анализа логических состояний микропроцессорных систем</a>

Предыдущий патент: Устройство для распределения заданий процессорам

Следующий патент: Сигнатурный анализатор

Случайный патент: Подъемно-мачтовое устройство