Преобразователь двоичных чисел в двоично-десятичные

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1481897

Авторы: Боюн, Малиновский, Реуцкий, Урсу

Текст

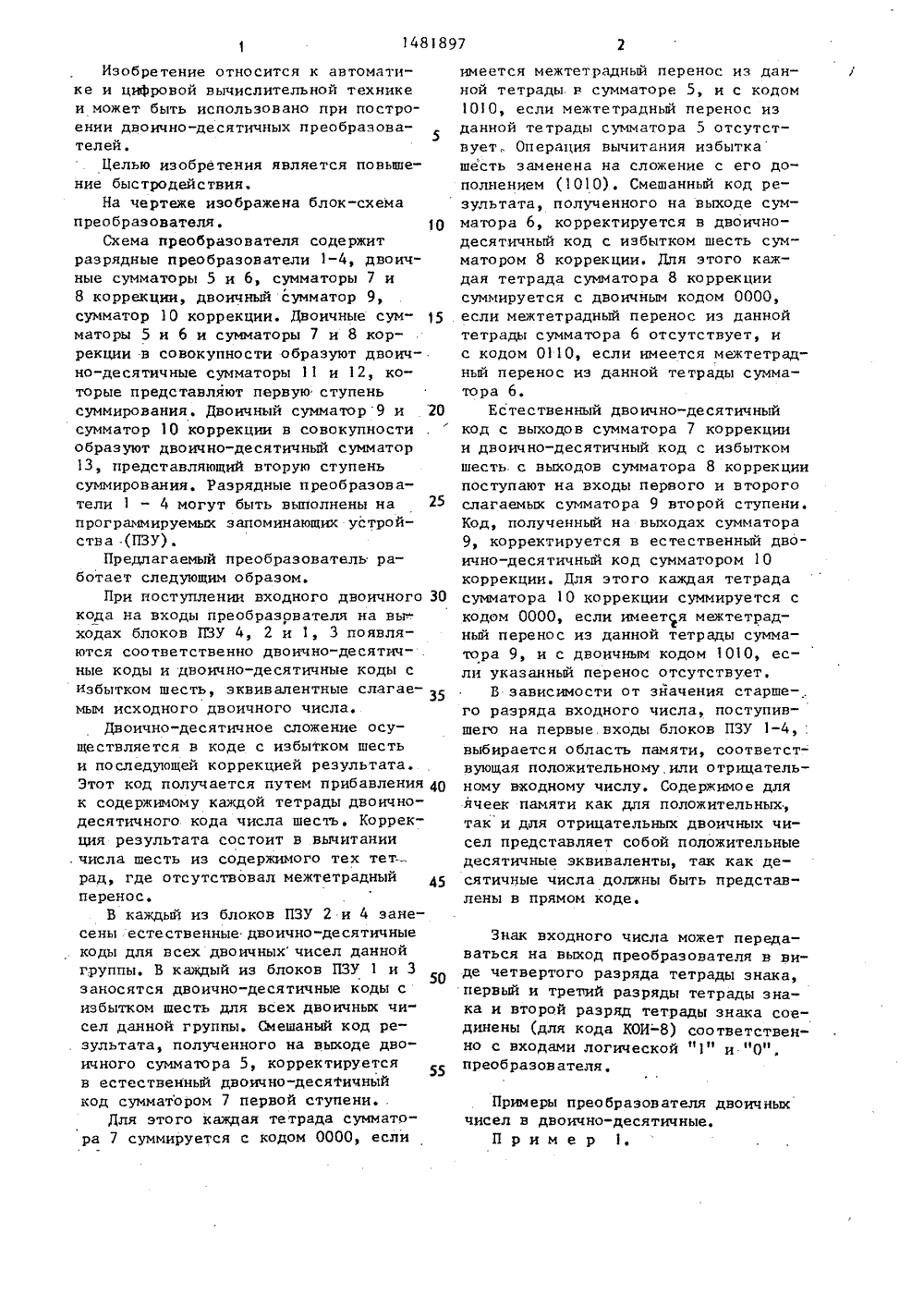

(51)4 Н 03 М 7/1 ОПИСАНИЕ ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ кий,ССС982. выч тения Фоичноб агсо 1 З 1 75)бП)В бб б РЧБ б б О Ф Яйнчно -6 есяаичное число ГОСУДАРСТВЕННЫЙ НОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМПРИ ГКНТ СССР(57) Изобретение относится клительной технике. Целью изоб является повышение быстродействия.Для этого в преобразователе двоичныхчисел в двоично-десятичные, содержащем разрядные преобразователи 1 - 4и двоично-десятичные сумматоры 1113, последние соединены в пирамидальную схему, и выполнены из двоичныхсумматоров 5, 6, 9 и сумматоров 7,8, 10 коррекции, При этом инверсныевыходы переноса нечетных двоичныхсумматоров соединены с входами вычитания (-6) соответствующих сумматоровкоррекции, а прямые выходы переносовчетных двоичных сумматоров соединеныс входами сложения (+6) соответствующих сумматоров коррекции. 1 ил.Изобретение относится к автоматике и цифровой вычислительной техникеи может быть использовано при построении двоично-десятичных преобраэова 5телей.Целью изобретения является повышение быстродействия,На чертеже изображена блок-схемапреобразователя1 ОСхема преобразователя содержитразрядные преобразователи 1-4, двоичные сумматоры 5 и 6, сумматоры 7 и8 коррекции, двоичный сумматор 9,сумматор 10 коррекции. Двоичные сумматоры 5 и 6 и сумматоры 7 и 8 коррекции в совокупности образуют двоично"десятичные сумматоры 11 и 12, которые представляют первую ступеньсуммирования. Двоичный сумматор 9 и 20сумматор 10 коррекции в совокупностиобразуют двоично-десятичный сумматор13, представляющий вторую ступеньсуммирования. Разрядные преобразователи 1 - 4 могут быть выполнены на 25программируемых запоминающих устройства .(ПЗУ),Предлагаемый преобразователь работает следующим образом.При поступлении входного двоичного 30кода на входы преобразователя на вы:"ходах блоков ПЗУ 4, 2 и 1, 3 появляются соответственно двоично-десятич- .ные коды и двоично-десятичные коды сизбытком шесть, эквивалентные слагаемым исходного двоичного числа,Двоично-десятичное сложение осуществляется в коде с избытком шестьи последующей коррекцией результата,Этот код получается путем прибавления 40к содержимому каждой тетрады двоичнодесятичного кода числа шесть. Коррекция результата состоит в вычитании.числа шесть из содержимого тех тет-.рад, где отсутствовал межтетрадныйперенос.В каждый из блоков ПЗУ 2 и 4 занесены естественные двоично-десятичныекоды для всех двоичныхчисел даннойгруппы. В каждый из блоков ПЗУ 1 и 3заносятся двоично-десятичные коды сизбытком шесть для всех двоичных чисел данной группы. Смешаный код ре. зультата, полученного на выходе двоичного сумматора 5, корректируетсяв естественный двоично-десятичныйкод сумматором 7 первой ступениДля этого каждая тетрада сумматора 7 суммируется с кодом 0000, если имеется межтетрадный перенос из данной тетрады. в сумматоре 5, и с кодом1010, если межтетрадный перенос изданной тетрады сумматора 5 отсутствует, Операция вычитания избыткашесть заменена на сложение с его дополнением (1010). Смешанный код результата, полученного на выходе сумматора 6, корректируется в двоичнодесятичный код с избытком шесть сумматором 8 коррекции, Для этого каждая тетрада сумматора 8 коррекциисуммируется с двоичным кодом 0000,если межтетрадный перенос из даннойтетрады сумматора 6 отсутствует, ис кодом 0110, если имеется межтетрадный перенос из данной тетрады сумматора 6,Естественный двоично-десятичныйкод с выходов сумматора 7 коррекциии двоично-десятичный код с избыткомшесть с выходов сумматора 8 коррекциипоступают на входы первого и второгослагаемых сумматора 9 второй ступени.Код, полученный на выходах сумматора9, корректируется в естественный двоично-десятичный код сумматором 10коррекции. Для этого каждая тетрадасумматора 10 коррекции суммируется скодом 0000, если имеетя межтетрадный перенос из данной тетрады сумматора 9, и с двоичным кодом 1010, если указанный перенос отсутствует,В зависимости от зйачения старше-.го разряда входного числа, поступившего на первые входы блоков ПЗУ 1-4,выбирается область памяти, соответствующая положительному или отрицательному входному числу. Содержимое дляячеек памяти как для положительных,так и для отрицательных двоичных чисел представляет собой положительныедесятичные эквиваленты, так как десятичные числа должны быть представлены в прямом коде.Знак входного числа может передаваться на выход преобразователя в виде четвертого разряда тетрады знака,первый и третий разряды тетрады знака и второй разряд тетрады знака соединены (для кода КОИ) соответственно с входами логической "1" и "0"преобразователя,Примеры преобразователя двоичных чисел в двоично-десятичные.Пример 1,Знак числа Исходный код 0Код на выходеПЗУ 4Код на выходеПЗУ 3После суммированияПереносыКоррекция+1000 1011 1110 1011 1100 0000 0011 1001 1 0 0000 0000 3 010 1000 11000 0 1010 1010 Код на выходеПЗУ 2Код на выходеПЗУ 1 1000После суммированияПе реносыКо рр екция 1000 О 00001101 013100000 О 10 1000 1101 1101 1000 1110 1000 1110 0111 1100 1000 1101 11010 0 0 1010 1010 1010 00 0 0131 00111 0011"0000 1000 1000 0101 0010 2 7 7, 3 О 8 8 5 2 Прим ер 2. Двоичное число Знак числа 11000 0111 100 0110 1101 0110 1100 1010 1001 1000 1000 0111 1010 0000 00110 О 0 1 1.0000 0000 0000 0110 0110 1000 0111 1010 0110 100 1010 0110 1000 1000 1030 1000 0111 1010 0110 1001 11000 0 0 0 0 0 1010 1010 1010 1030 1010 1010 1110 1011 1101 11110 0 0 0 10 0 1010 1010 1010 0010 000 03 00 0000 0011 0110 1000 010 03 11 1001 Де ся тично ечисло-2 к 1 4 О, 3 После второгосуммированияПереносыКоррекцияДесятичноечисло +О. Исходный кодКод на выходеПЗУ 4Код на выходеПЗУ 3После суммированияяПереносыКоррекция Код на выходе ПЗУ 2 Код на выходе ПЗУ 1После суммиров ания Переносы Коррекция После второго суммированияяПереносыКоррекция 001 0000 1000 0111 0110 0101 1011 0100 1 1000 00001897 Составитель М. Аршавскийредактор М. Бланар Техред д,0 лийнык Корректор И. ГоРная Заказ 2701/56 Тираж 885 ПодписноеВНИИПИ Государственного комитета по изобретениям и открытиям, при ГКНТ СССР113035, Москва, Ж, Раушская наб., д, 4/5 Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,101 б 148Формула изобретения Преобразователь двоичных чисел в двоично-десятичные, содержащий ступени двоично-десятичных сумматоров и группу разрядных преобразователей, входы младших разрядов которых соединены с входами соответствующих разрядов преобразователя, знаковый вход которого соединен с входами старшего разряда всех разрядных преобразователей и является выходом знака преобразователя,.информационные выходы которого являются выходами последнего . двоично-десятичного сумматора, выходы первого и второго разрядных преобразователей соединены соответственно с первым и вторыми входами первого двоично-десятичного сумматора первой ступени,. выходы первого двоичнодесятичного сумматора каждой ступени соединены с первыми входами первого сумматора соседней старшей ступени о т л и ч а ю щ и й с я тем, что, с целью повышения быстродействия, в нем выходы .-го (1 = 1 - и/ш) нечетного разрядного преобразователя соединены с первыми входами (1+3-)"го двоично-десятичного сумматора первой ступени, а выходы д-го четного разрядного преобразователя соединены с вторыми входами - -го двоично-деся 2тичного сумматора первой ступени, Бгде и ш - разрядности входного кода9и разрядного преобразователя соответственно, выходы нечетных двоично-деЭсятичных сумматоров каждой ступенисоецинены с первыми входами двоично десятичных сумматоров соседней старшей ступени, вторые входы которыхсоединены с выходами четных двоичнодесятичных сумматоров соседней младшей ступени, причем все двоична-десятичные сумматоры содержат разделенные на тетрады сумматор коррекции идвоичный сумматор, инверсные выходыпереноса каждой тетрады нечетных двоичных сумматоров каждой ступени соединены с входами второго и четвертогоразрядов соответствующей тетрады сумматоров коррекции, входы первого итретьего разрядов которых соединеныс входом логического нуля преобразо вателя, прямые выходы переноса каждой тетрады четных двоичных сумматоров соединены с входами второго итретьего разрядов соответствующихсумматоров коррекции, входы первогои четвертого разрядов которых соединены с входом логического нуля преобразователя.

СмотретьЗаявка

4257545, 08.06.1987

ИНСТИТУТ КИБЕРНЕТИКИ ИМ. В. М. ГЛУШКОВА

БОЮН ВИТАЛИЙ ПЕТРОВИЧ, МАЛИНОВСКИЙ БОРИС НИКОЛАЕВИЧ, РЕУЦКИЙ ВАДИМ ЕФИМОВИЧ, УРСУ МИХАИЛ ЕФИМОВИЧ

МПК / Метки

МПК: H03M 7/12

Метки: двоично-десятичные, двоичных, чисел

Опубликовано: 23.05.1989

Код ссылки

<a href="https://patents.su/4-1481897-preobrazovatel-dvoichnykh-chisel-v-dvoichno-desyatichnye.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь двоичных чисел в двоично-десятичные</a>

Предыдущий патент: Преобразователь двоичного кода в унитарный код

Следующий патент: Преобразователь чисел из модулярного кода в позиционный код

Случайный патент: Скородействующий тройной клапан вестингауза