Преобразователь чисел из модулярного кода в позиционный код

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

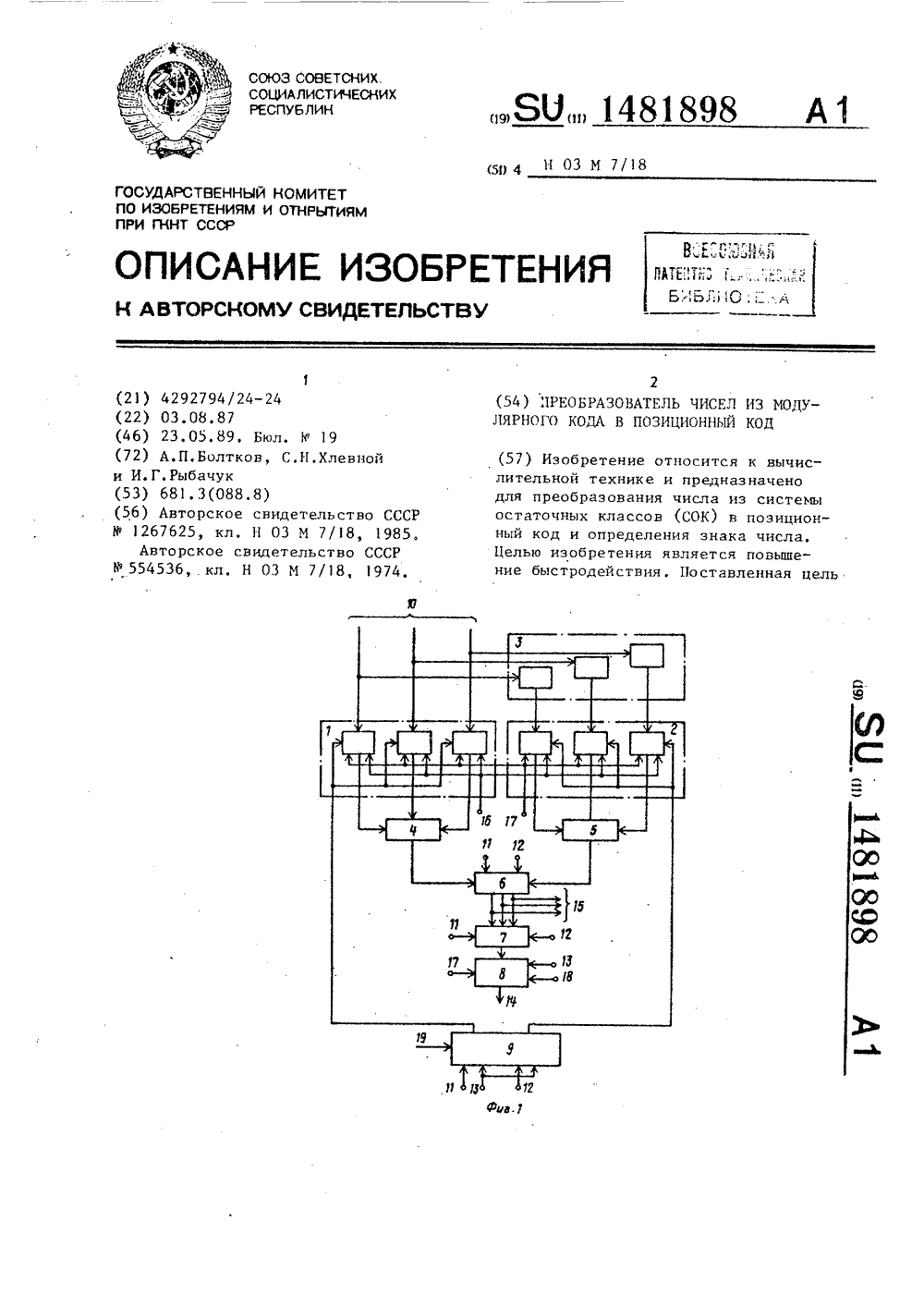

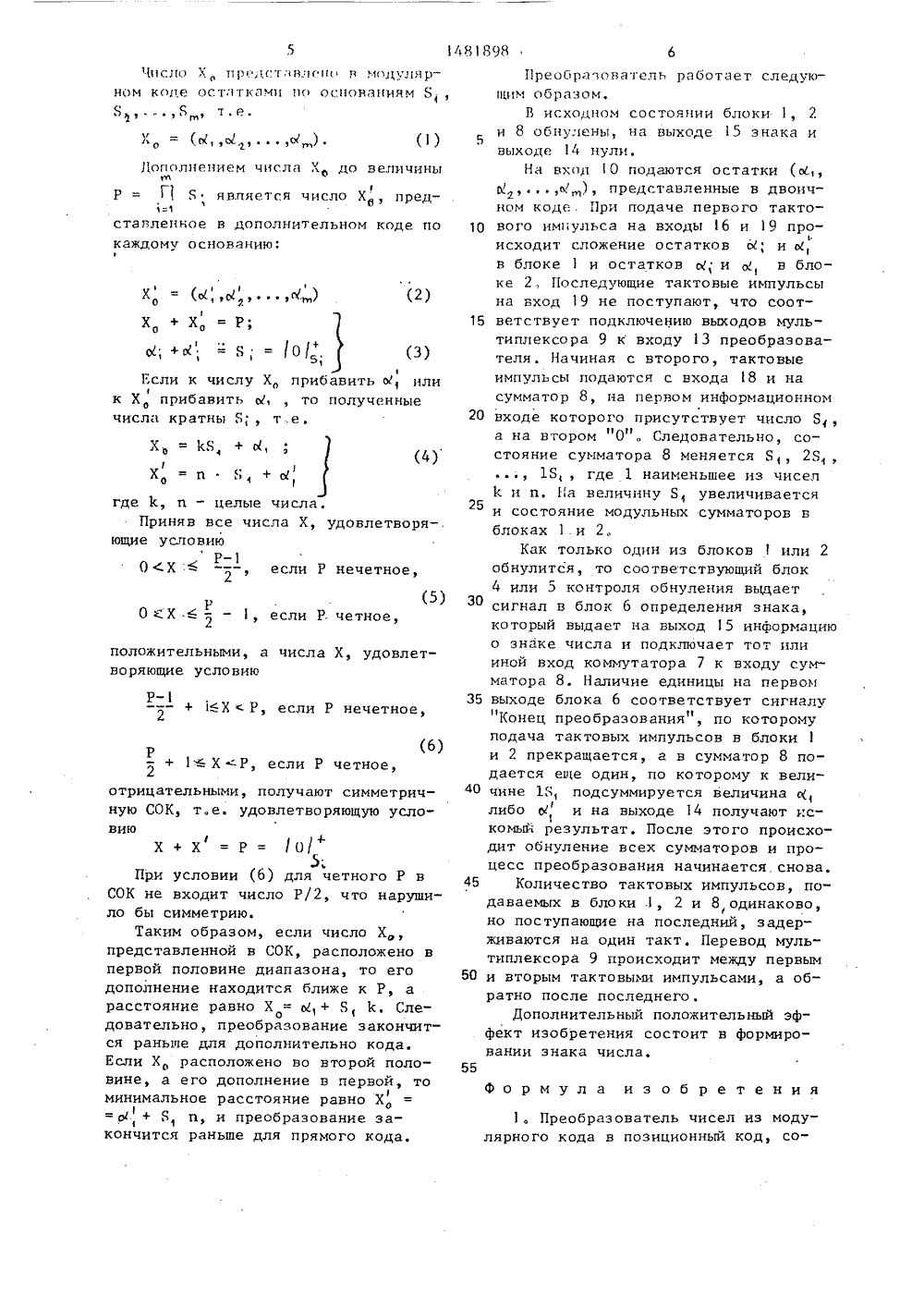

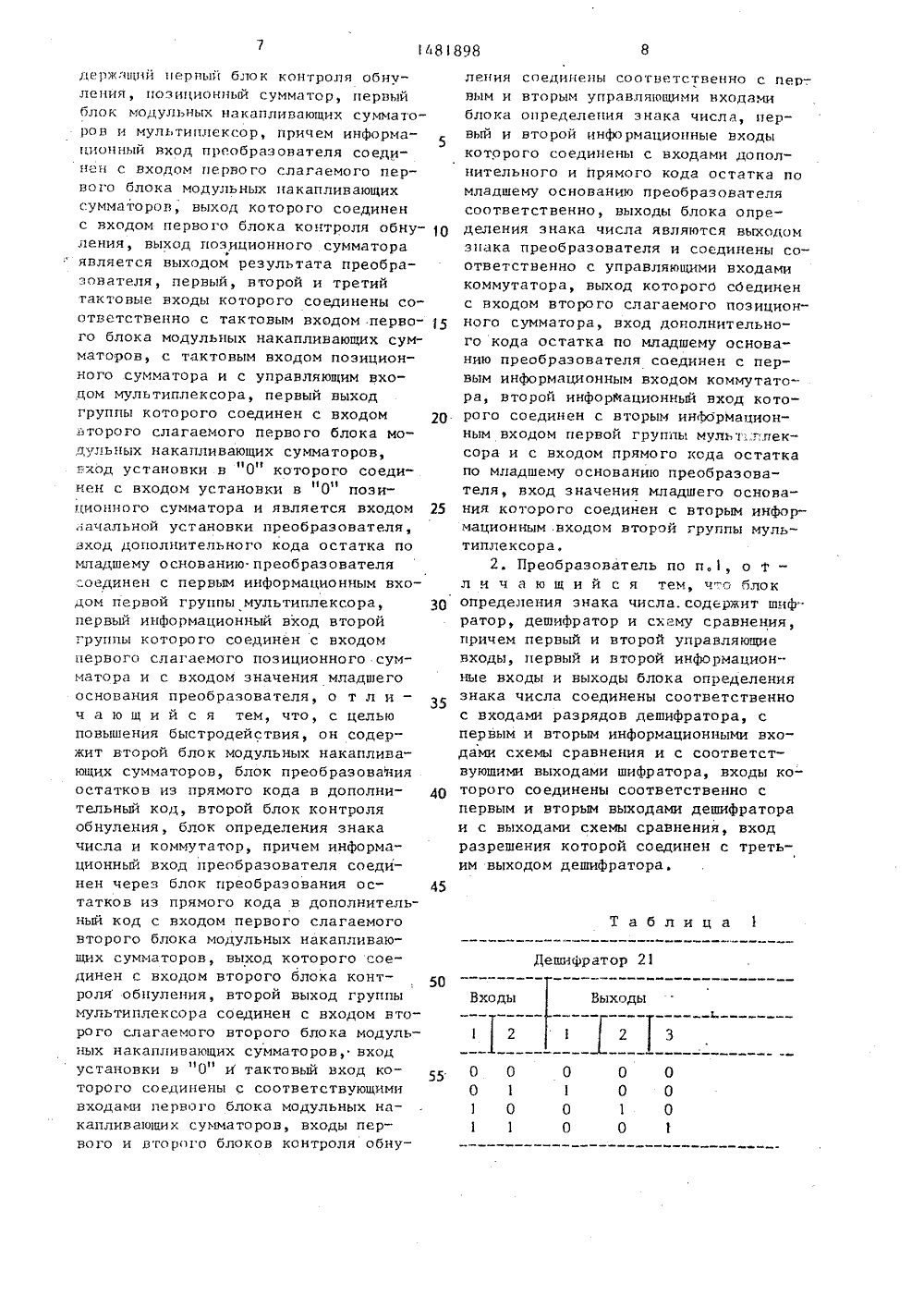

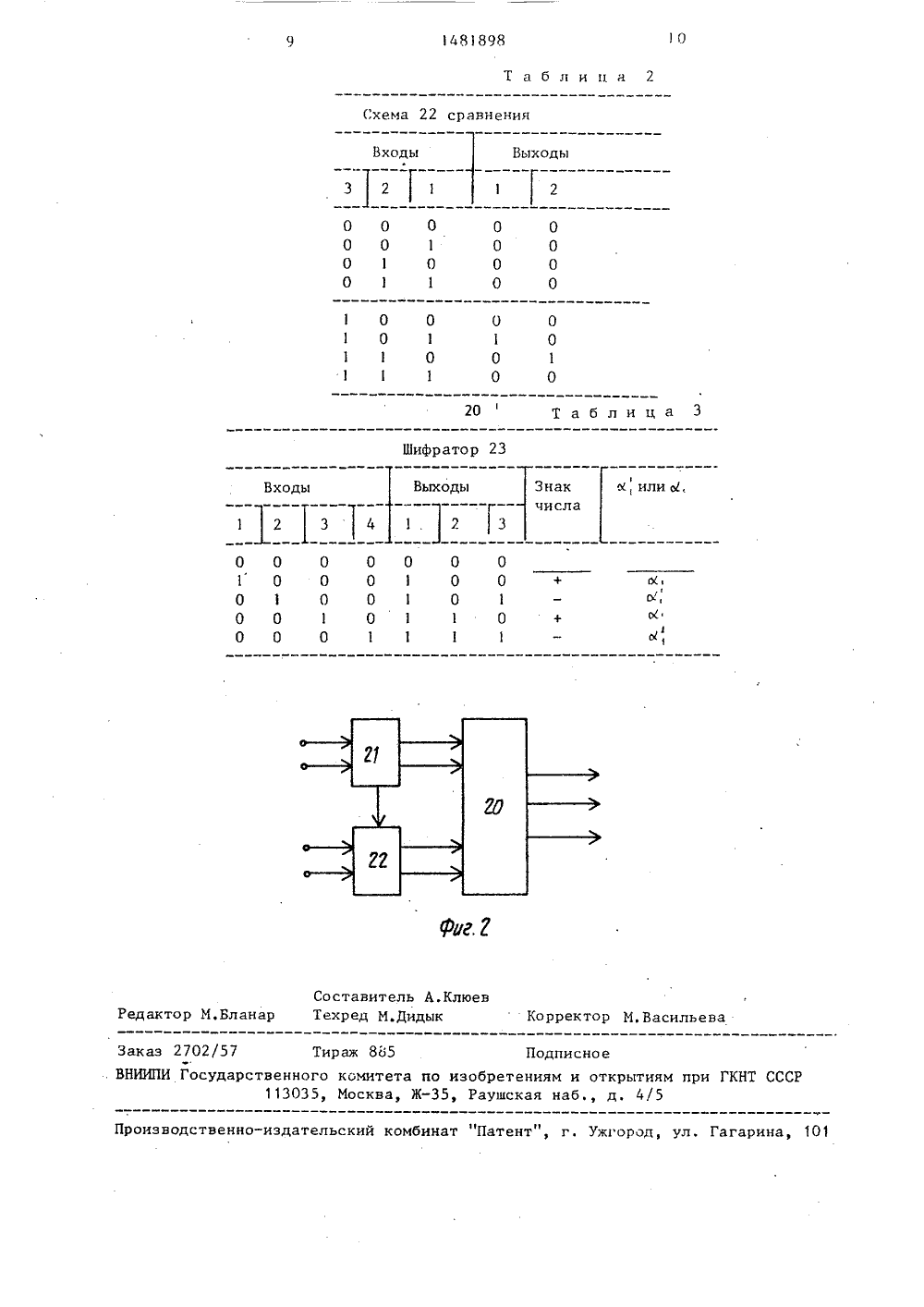

СОЮЗ СОВЕТСКИХ.СОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 114 НОЗМ 7/ ТЕНИ И:, Б:1 Б;1 С" Ф ТВ евноь льство ССС 7/18, 1985 ство СССР /18, 1974. онцель ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР ПИСАНИЕ ИЗ А ВТОРСКОМУ СВИДЕТЕ(54):1 РЕОБРАЗОВАТЕЛЬ ЧИСЕЛ ИЗ МОЛЯРНОГО КОДА В ПОЗИЦИОННЫЙ КОД(57) Изобретение относится к выч лительной технике и предназначен для преобразования числа из сист остаточных классов (СОК) в позиц ный код и определения знака числ Целью изобретения является повьпп ние быстродействия, Поставленная1481898 достигается тем, что преобразователь,содержащий блок 1 модульных накапливающих сумматоров, блок 4 контроляобнуления, позиционный сумматор 8 имультиплексор 9, содержит блок 2 модульных накапливающих сумматоров,блок 3 преобразования остатков иэпрямого кода в дополнительный код,Изобретение относится к вычислительной технике и предназначено дляпреобразования числа из системы остаточных классов (СОК) в позиционныйкод и определения знака числа, 5Цель изобретения - повышение быстродействия.На фиг.1 представлена схема преобразователя чисел из модулярногокода в позиционный код; на фиг,2 - 10схема блока определения знака числа,Преобразователь фиг,1 содержитпервый блок 1 модульных накапливающих сумматоров, второй блок 2 модуль.ных накапливающих сумматоров, блок 3 15преобразования остатков иэ прямогокода в дополнительный код, первый 4и второй 5 блоки контроля обнуления,блок 6 определения знака числа, коммутатор 7, позиционный сумматор 8, 20мультиплексор 9, информационный вход10 преобразователя, входы 11 и 12дополнительного и прямого кода остатка по младшему основанию преобразователя, вход 13 значения младшего ос-нования преобразователя, выход 14результата преобразователя, выход 151знака преобразователя, первый тактовый вход 16 преобразователя, вход 17начальной установки преобразователя,второй тактовый вход 18 преобраэова"теля, Блок 6 определения знака числа(фиг.2) содержит шифратор 20, дешифратор 21 и схему 22 сравнения.Блоки 4 и 5 комбинационные, на их 35выходах появляется сигнал логической"1", если на выходах блоков 1 и 2 нулевые значения,Блок 6 определения знака числапредставляет собой комбинационныйблок. На входы дешифратора 21 подаблок 5 контроля обнуления, блок 6 определения знака числа и коммутатор 7с соответствующими связями. Сущностьизобретения состоит н том, что преобразование в позиционный код происходит по двум каналам в прямом и дополнительном кодах одновременно,1 э,пф-лы, 2 ил., 3 табл. 4ются сигналы с выходов блоков контроля обнуления, а на входы схемы 22 сравнения - остатки о, и Ы . Третий выход дешифратора 21 является уп равляющим для схемы сравнения, при появлении единицы, на котором, что соответствует появлению единицы на обоих входах дешифратора 21 включается в работу схема 22 сравнения,Дешифратор 21, схема 22 сравнения и шифратор 20 для одного двоичного разряда (для других - структура сох-. раняется) описываются соответственно табл,1-3. При одновременном обнулении блоков 1 и 2 определение знака и послед-. него слагаемого о, производится пуГ тем сравнения величин м, и М, ,для которых выполнение условия о, =Ы 1 может быть только при о, = о, = О. Но такая ситуация возникает только при приведении всего преобразователя в исходное состояние обнуление . Логика работы блока 6 исключает ложный сигнал при появлении такого состояния, Из табл1 - 3 видно, что если ы =Ы, = 0 и на входах дешифратора две единицы, соответствующие одновременно обнуленным блокам 1 и 2, то на выходах дешифратора все нули.Коммутатор 7 выполнен любым известным способом, вариант соответствия управляющего кода и коммутируемых входов представлен в табл.3, так как выходы шифратора являются управляющими входами коммутатора.Сумматор 8 накапливающего типа тактируемый,В преобразователе (фиг.1) реализуется следующий алгоритм работы.30 держащий перный блок контроля Обнуления, позиционный сумматор, первый блок модульных накапливающих сумматоров и мультиплексор, пРичем информационный вход преобразователя соединен с входом первого слагаемого первого блока модульных накапливающих сумматоров, выход которого соединен с входом первого блока контроля обну ления, выход позиционного сумматора является выходом результата преобразователя, первый, второй и третий гактовые входы которого соединены соответственно с тактовым входом перво го блока модульных накапливающих сумматоров, с тактовым входом позиционного сумматора и с управляющим входом мультиплексора, первый выход группы которого соединен с входом 20. второго слагаемого первого блока модульных накапливающих сумматоров, вход установки в ПО" которого соединен с входом установки в "Оп позиционного сумматора и является входом 25 ;ачальной установки преобразователя, вход дополнительного кода остатка по младшему основанию-преобразователя соединен с первым информационным входом первой группы мультиплексора, первый информационный вход второй группы которого соединен с входом первого слагаемого позиционного сумматора и с входом значения младшего основания преобразователя, о т л и - ч а ю щ и й с я тем, что, с целью повышения быстродействия, он содержит второй блок модульных накапливающих сумматоров, блок преобразования остатков из прямого кода в дополни тельный код, второй блок контроля обнуления, блок определения знака числа и коммутатор, причем информационный вход преобразователя соединен через блок преобразования ос татков из прямого кода в дополнительный код с входом первого слагаемого второго блока модульных накапливающих сумматоров, выход которого соединен с входом второго блока контроля обнуления, второй выход группы мультиплексора соединен с входом второго слагаемого второго блока модульных накапливающих сумматоров, входустановки в Оп и тактовый вход которого соединены с соответствующими входами первого блока модульных накапливающих сумматоров, входы первого и второго блоков контроля обнуления соединены соответственно с пер-. вым и вторым управляющими входами блока определения знака числа, первый и второй информационные входы которого соединены с входами дополнительного и прямого кода остатка по младшему основании преобразователя соответственно, выходы блока определения знака числа являются выходом знака преобразователя и соединены соответственно с управляющими входами коммутатора, выход которогО сбединен с входом второго слагаемого позиционного сумматора, вход дополнительного кода остатка по младшему основанию преобразователя соединен с первым информационным входом коммутатора, второй информационный вход которого соединен с вторым инфбрмационным входом первой группы муль г; ллексора и с входом прямого кода остатка по младшему основанию преобразователя, вход значения младшего основания которого соединен с вторым информационным .входом второй группы мультиплексора,2. Преобразователь по п,1, о л и ч а ю щ и й с я тем, ч О блок определения знака числа. содержит шиф" ратор, дешифратор и схему сравнения, причем первый и второй управляющие входы, первый и второй информационные входы и выходы блока определения знака числа соединены соответственно с входами разрядов дешифратора, с первым и вторым информационными входами схемы сравнения и с соответствуюшими выходами шифратора, входы которого соединены соответственно с первым и вторым выходами дешифратора и с выходами схемы сравнения, вход разрешения которой соединен с третьим выходом дешифратора,ТаблицаДешифратор 21 Входы Выходы 1 2 1 2 3 О О О О О О 1 1 О О 1 О О 1 О 1 1 О О. ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж, Раушская наб., д. 4/5

СмотретьЗаявка

4292794, 03.08.1987

СТАВРОПОЛЬСКОЕ ВЫСШЕЕ ВОЕННОЕ ИНЖЕНЕРНОЕ УЧИЛИЩЕ СВЯЗИ ИМ. 60-ЛЕТИЯ ВЕЛИКОГО ОКТЯБРЯ

БОЛТКОВ АЛЕКСАНДР ПАВЛОВИЧ, ХЛЕВНОЙ СЕРГЕЙ НИКОЛАЕВИЧ, РЫБАЧУК ИГОРЬ ГЕННАДЬЕВИЧ

МПК / Метки

МПК: H03M 7/18

Метки: код, кода, модулярного, позиционный, чисел

Опубликовано: 23.05.1989

Код ссылки

<a href="https://patents.su/5-1481898-preobrazovatel-chisel-iz-modulyarnogo-koda-v-pozicionnyjj-kod.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь чисел из модулярного кода в позиционный код</a>

Предыдущий патент: Преобразователь двоичных чисел в двоично-десятичные

Следующий патент: Кодирующее устройство

Случайный патент: Датчик тока на герконах