Параллельный накапливающий сумматор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

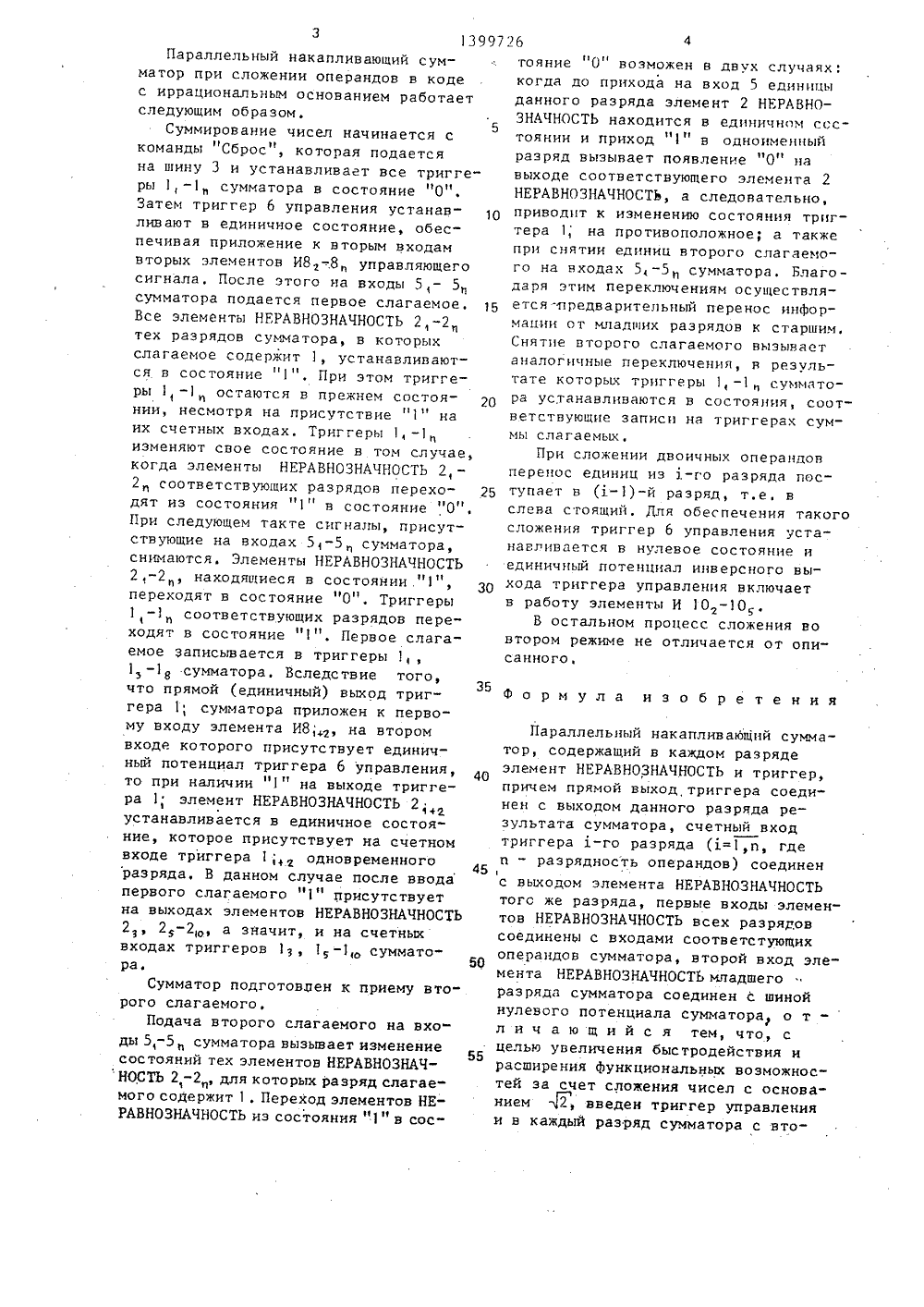

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСНРЕСПУБЛИК А 1 19) (И) Р 7/ ЕНИЯ ь.ЙЬ 1(Ма 4155165/24-24 02,12.8630.05.88. Бюл. 9 Винницкий полите ическ и к ложении в кодах с ирра,2. Сумматор ющихся СССР982,СР984,элемент ину 3 с дов перандов,мами работе 8-8 эл(57) Ительнозовано ЛЛЕЛЬНЫЙ НАКАПЛИ 9 -9 нак таб ыч исл в ходы аЮ пливающеполь" ннь специалиэиро ч ислиОСУДАРСТВЕННЫЙ НОМИТЕТ СССР О ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЬ 1 Т(56) Авторское свидетельство11 1 083182, кл. С 06 Р 7/49,Авторское свидетельство СВ 1166099, кл. С 06 Р 7/50,бретение относитсятехнике и может быт ельных машинах и цифровых средстваоботизированных систем управленияля сложения чисел с иррациональнымснованием и обработки векторной инормации. Цель изобретения - увелиение быстродействия и расширениеункциональных возможностей, эаклюциональным основанием содержит триггеры 1, -1 НЕРАВНОЗНАЧНОСТЬ 2,-2 са, выходы 4-4 разря входы 5,-5 разрядов о геры 6 управления режи первые 1 О -10 и вторь менты И, элементы ИЛИ 11 и 12 режимов работь го сумматора. 1 ил., 1Изобретение относится к вычислительной гехнике и может быть использовано в специализированных вычислительных машинах и цифровых устройст 5 вах роботизированных систем управ.ления для сложения чисел с иррациональными основаниями и обработки векторной информации,Цель изобретения - унеличение быстродействия и расширение функциональных воэможностей сумматора за счет сложения чисел с основанием -2.На чертеже представлена функциональная схема пяти разрядов параллельного накапливающего сумматораПараллельный накапливающий суматор содержит триггеры 1, элементы ЕРАВНОЗНАЧНОСТЬ 2, вход 3 сброса умматора, выходы 4 результата, вхоы 5 операндов, триггер 6 управления, коммутаторы 7, состоящие кз элеМентов И 8, элементов ИЛИ 9 и элементов И 10, а также первый и второй входы 11 и 12 задания режимов работы 25 сумматора.Параллельный накапливающий сумматор предназначен для суммирования ЭектороВ, представленных в двоичнокодированной позиционной системе 30 счисления с основанием 42.В позиционной системе счисления сОснованием 42 любой вектор Х пред"Ставляется в видеХ щ Хп.(42)"+Хо,(42) +ффф ++ Х,(42) +Х, (42) +Х,(Г 2) , (1)Учитывая, что веса разрядов данноо кода являются последовательностьюстепеней основания 4216"Г 2 16 82 8 4 Г 2 42 Г 2 2 Г 2 1,Четные степени которой представляк 1 т веса разрядов двоичного кода, а Нечетные - веса разрядов двоичного кода, умноженные на Г 2, то выражение (1) можно записать так;50И.1, ИГ 2 Х;2 +Х г 1 :0 где величины принимают следующизначения:55Первый член формулы (2) составляет сумму нечетных разрядов кода, а второй член - сумму четных разрядов кода с основанием -12.Выражение (2) позволяет любой вектор на плоскости изобразить в виде двух составных векторов, направление одного из которых. совпадает с координатой прямоугольной системы, а его1 величина равнаХ;2 . Направление=О другого вектора состанляет с коордио натами угол 45 , и его значение представляется н виде2Х 2Особенностью такого изображения является то, что код с основанием-12, используемый для записи вектора, единый ин то же время члены выражения (2) независимы друг от друга. Зто позволяет при сложении двух некторов осуществлять параллельное и не- независимое сложение составных частей векторов, в результате увеличивается в дна раза быстродействие сумматоров с двоичным представлением информации. Сложение двух одноименных разрядов в двоичной системе счисления с иррациональным основанием 2 выполняется согласно таблице.Если в -х разрядах (четных или нечетных) слагаемых имеются единицы, то, как это следует иэ таблицы, единица переноса поступает в (1+2)-й разряд кода в отличие от традиционной двоичной системы счисления, где единица поступает в (1+1)-й разрядПараллельный накапливающий сумматор может работать в двух режимах; режиме сложения операндов, представленных в коде с основанием Г 2, и режиме суммирования при двоичном представлении операндов. Первый режим обеспечивается устанонкой триггера 6 управления в единичное состояние, для чего на первый вход 12 задания режима работы подается сигнал, а нторой режим задается сигналом, поступающим на второй вход 1 задания режима работы.з 13997Параллельный накапливающий сумматор при сложении операндов в кодес иррациональным основанием работаетследующим образом,5Суммирование чисел начинается скоманды "Сброс", которая подаетсяна шину 3 и устанавливает все триггеры 1, - 1 сумматора в состояние нО.Затем триггер 6 управления устанавливают в единичное состояние, обеспечивая приложение к вторым входамвторых элементов И 8-.8 управляющегосигнала, После этого на входы 5- 5сумматора подается первое слагаемое.Все элементы НЕРАВНОЗНАЧНОСТЬ 2-2тех разрядов сумматора, в которыхслагаемое содержит 1, устанавливаются в состояние1". При этом триггеры 1, -1 остаются в прежнем состоянии, несмотря на присутствие "1" наих счетных входах. Триггеры 1, -1изменяют свое состояние в том случае,когда элементы НЕРАВНОЗНАЧНОСТЬ 2, -2соответствующих разрядов переходят из состояния "1" в состояние "0 .При следующем такте сигналы, присутствующие на входах 5,-5, сумматора,снимаются. Элементы НЕРАВНОЗНАЧНОСТЬ2,-2, находящиеся в состоянии.,переходят в состояние "0", Триггеры1,-1 соответствующих разрядов переходят в состояние 1". Первое слагаемое записывается в триггеры 11 -1 а сумматора. Вследствие того,35что прямой (единичный) выход триггера 1, сумматора приложен к первому входу элемента И 8;, на второмвходе которого присутствует единичный потенциал триггера 6 управления, 40то при наличии "1" на выходе триггера 1; элемент НЕРАВНОЗНАЧНОСТЬ 2;устанавливается в единичное состояние, которое присутствует на счетномвходе триггера 1;, одновременного 45разряда. В данном случае после вводапервого слагаемого "1" присутствуетна выходах элементов НЕРАВНОЗНАЧНОСТЬ2 , 2-2 ю а значит, и на счетныхвходах триггеров 1 з 1 -1, суммато 50ра.Сумматор подготовлен к приему второго слагаемого,Подача второго слагаемого на входы 5,-5 сумматора вызывает изменениесостояний тех элементон НЕРАВНОЗНАЧНОСТЬ 2,-2, для которых разряд слагаемого содержит 1. Переход элементов НЕРАВНОЗНАЧНОСТЬ из состояния "1" в сос 264 тояние 0 возможен в двух случаях;когда до прихода на вход 5 единицыданного разряда элемент 2 НЕРАВНОЗНАЧНОСТЬ находится в единичном ссстоянии и приход "1" н одноименныйразряд вызывает появление "0" навыходе соответствующего элемента 2НЕРАВНОЗНАЧНОСТЬ, а следовательно,приводит к изменению состояния тригтера 1; на противоположное; а такжепри снятии единиц второго слагаемого на входах 5, -5сумматора. Благодаря этим переключениям осуществляется.предварительный перенос информации от младших разрядов к старшим.Снятие второго слагаемого вызывает аналогичные переключения, в результате которых триггеры 1 -1сумматора устанавливаются в состояния, соответствующие записи на триггерах суммы слагаемых.При сложении двоичных операндов перенос единиц из 1-го разряда поступает в (1-1)-й разряд, т.е, в слева стоящий. Для обеспечения такого сложения триггер 6 управления устанавливается в нулевое состояние и единичный потенциал инверсного выхода триггера управления включает в работу элементы И 10-10.В остальном процесс сложения но втором режиме не отличается от описанного,Формула изобретения Параллельный накапливающий сумматор, содержащий в каждом разряде элемент НЕРАВНОЗНАЧНОСТЬ и триггер, причем прямой выход триггера соединен с выходом данного разряда результата сумматора, счетный вход триггера 1-го разряда (ь=1 п где и - разрядность операндов) соединен с выходом элемента НЕРАВНОЗНАЧНОСТЬ того же разряда, первые входы элементов НЕРАВНОЗНАЧНОСТЬ всех разрядов соединенш с входами соответстующих операндов сумматора, второй вход элемента НЕРАВНОЗНАЧНОСТЬ младшего разряда сумматора соединен с шиной нулевого потенциала сумматора о т -Р личающийся тем что, с целью увеличения быстродействия и расширения Функциональных возможностей за счет сложения чисел с основанием -12, введен триггер управления и н каждый разряд сумматора с вто1399726 Составитель М, ЕсенинаТехред Л.Сердюкова Корректор М. Максимишинец Редактор А. Огар Заказ 2666/48 Тираж 704 ПодписноеВНИИПИ Государственного комитета. СССРпо делам изобретений и открытий113035, Москва, Ж, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 оОго по п-й введен коммутатор, причем первый информационный вход коммутатора "го разряда соединен с прямым выходом триггера (1-1) -го разряда, второй информационный входкоммутатора второго разряда соединенс шиной нулевого потенциала, вторыеинформационные входы коммутатороввсех разрядов, кроме второго, соединены соответственно с прямыми вьходами триггеров (1-2)-х разрядов,первый и второй управляющие входы коммутаторов -го разряда соединены соответственно с инверсным и прямым выходами триггера управления, с единичным и нулевым входами которого соединены соответственно первый и второй входы задания режимов сумматора, вторые входы элементов НЕРАВ НОЗНАЧНОСТЬ всех разрядов, кроме пер"ваго, соединены с выходами коммутаторов соответствующих разрядов,

СмотретьЗаявка

4155165, 02.12.1986

ВИННИЦКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

СТАХОВ АЛЕКСЕЙ ПЕТРОВИЧ, КВИТКА НИКОЛАЙ АНДРЕЕВИЧ, ЛУЖЕЦКИЙ ВЛАДИМИР АНДРЕЕВИЧ

МПК / Метки

МПК: G06F 7/49

Метки: накапливающий, параллельный, сумматор

Опубликовано: 30.05.1988

Код ссылки

<a href="https://patents.su/4-1399726-parallelnyjj-nakaplivayushhijj-summator.html" target="_blank" rel="follow" title="База патентов СССР">Параллельный накапливающий сумматор</a>

Предыдущий патент: Параллельно-последовательное устройство для умножения в конечных полях

Следующий патент: Устройство для двоичного деления

Случайный патент: Счетчик импульсов