Устройство микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1381505

Автор: Пшеницын

Текст

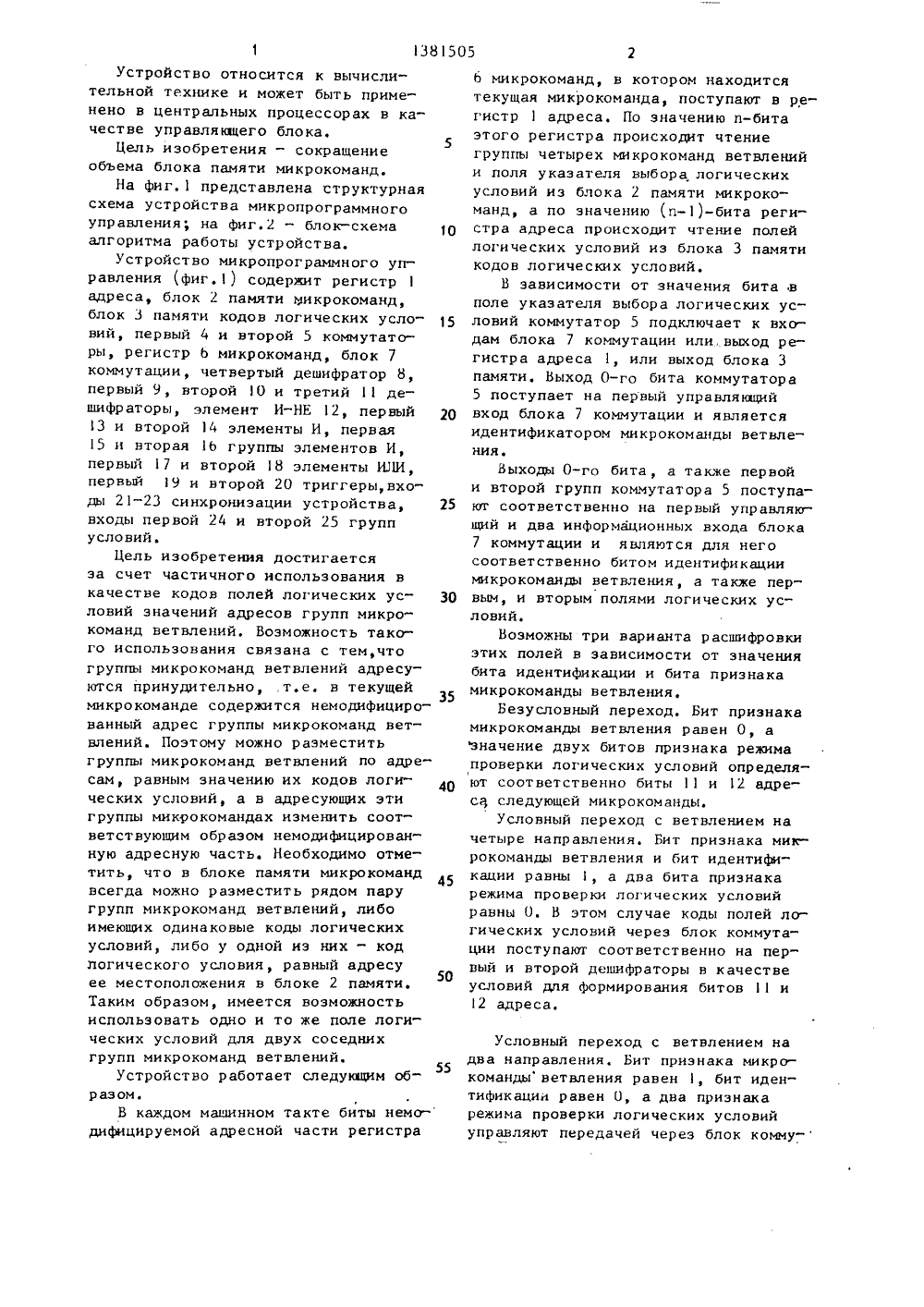

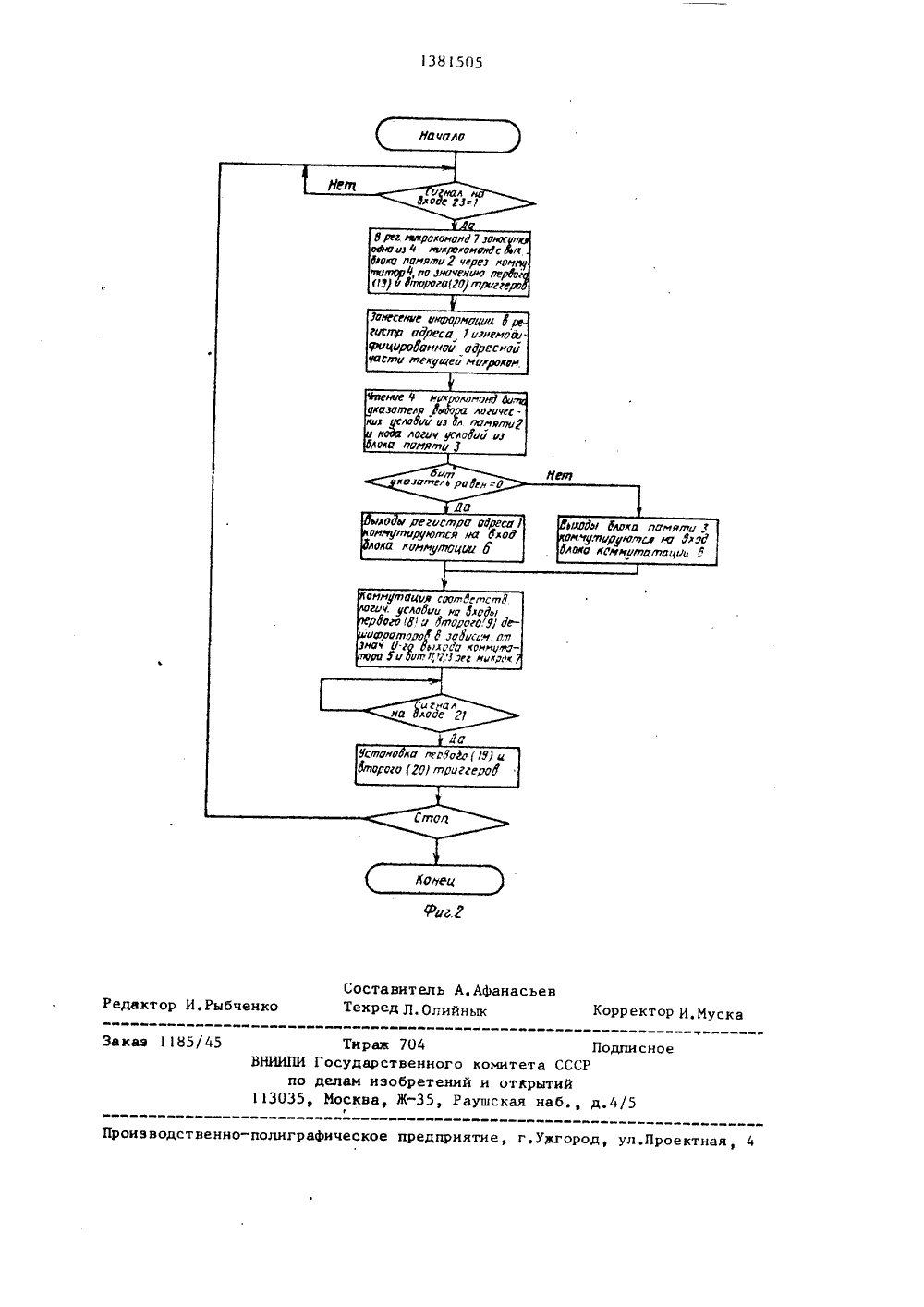

(19 06 У 9 22 юу твг,С"ту - е ПИСАНИЕ ИЗОБРЕТЕНИ ЫНМ.;" 4Ф ельство СССР 9/22, 1985. ого управле ание ЩК,относится к вычиси может быть приных процессорах в ГОсудАРстВенный нОмитет сссР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИ А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ(57) Изобретениелительной техникеменено в централь качестве управляющего блока. Цельизобретения - сокращение объема блока памяти микрокоманд. Устройствосодержит регистр 1 адреса, блок 2памяти микрокоманд, блок 3 памятикодов логических условий, коммутаторы 4 и 5, регистр 6 микрокоманд,блок 7 коммутации, дешифраторы 8,9, О и 1, элемент И-НЕ 2, элементы И 13 и 4, группы 15 и 16 элементов И, элементы ИЛИ 17 и 18, триггеры 19 и 20. Введение блока 3 памятикодов логическихусловий и коммутатора 5 приводит к достижению цели.Устройство относится к вычислительной технике и может быть применено в центральных процессорах в качестве управляющего блока.5Цель изобретения - сокращениеобъема блока памяти микрокоманд,На фиг.1 представлена структурнаясхема устройства микропрограммногоуправления; на Фиг.2 - блок-схемаалгоритма работы устройства.Устройство микропрограммного управления (фиг.1) содержит регистр 1адреса, блок 2 памяти Юикрокоманд,блок 3 памяти кодов логических условий, первый 4 и второй 5 коммутаторы, регистр Ь микрокоманд, блок 7коммутации, четвертый дешифратор 8,первый 9, второй 10 и третий 11 дешифраторы, элемент И-НЕ 12, первый 2013 и второй 14 элементы И, первая15 и вторая 1 Ь группы элементов И,первый 17 и второй 18 элементы ИЛИ,первый 19 и второй 20 триггеры,входы 21-23 синхронизации устройства, 25входы первой 24 и второй 25 группусловий.Цель изобретения достигаетсяза счет частичного использования вкачестве кодов полей логических условий значений адресов групп микрокоманд ветвлений, Воэможность такого использования связана с тем,чтогруппы микрокоманд ветвлений адресуются принудительно, т,е. в текущеймикрокоманде содержится немодифицированный адрес группы микрокоманд ветвлений. Поэтому можно разместитьгруппы микрокоманд ветвлений по адресам, равным значению их кодов логических условий, а в адресующих этигруппы микрокомандах изменить соответствующим образом немодифицированную адресную часть. Необходимо отметить, что в блоке памяти микрокоманд 45всегда можно разместить рядом паругрупп микрокоманд ветвлений, либоимеющих одинаковые коды логическихусловий, либо у одной из них - кодлогического условия, равный адресу50ее местоположения в блоке 2 памяти,Таким образом, имеется возможностьиспольэовать одно и то же поле логических условий для двух соседнихгрупп микрокоманд ветвлений.Устройство работает следукюцим образом.В каждом машинном такте биты немо-дифицируемой адресной части регистра Ь микрокоманд, в котором находится текущая микрокоманда, поступают в регистр 1 адреса. По значению и-бита этого регистра происходит чтение группы четырех микрокоманд ветвлений и поля указателя выбора логических условий из блока 2 памяти микрокоманд, а по значению (п)-бита регистра адреса происходит чтение полей логических условий из блока 3 памяти кодов логических условий.В зависимости от значения бита в поле указателя выбора логических условий коммутатор 5 подключает к входам блока 7 коммутации или,выход регистра адреса 1, или выход блока 3 памяти. Выход 0-го бита коммутатора 5 поступает на первый управляющий вход блока 7 коммутации и является идентификатором микрокоманды ветвленияВыходы 0-го бита, а также первой и второй групп коммутатора 5 поступают соответственно на первый управляющий и два информационных входа блока 7 коммутации и являются для него соответственно битом идентификации микрокоманды ветвления, а также первым, и вторым полями логических условий.Возможны три варианта расшифровки этих полей в зависимости от значения бита идентификации и бита признака микрокоманды ветвления.Безусловный переход. Бит признака микрокоманды ветвления равен О, а значение двух битов признака режима проверки логических условий определяют соответственно биты 11 и 12 адреса следующей микрокоманды,Условный переход с ветвлением на четыре направления. Бит признака микрокоманды ветвления и бит идентификации равны 1, а два бита признака режима проверки логических условий равны О, В этом случае коды полей логических условий через блок коммутации поступают соответственно на первый и второй дешифраторы в качестве условий для Формирования битов 11 и 2 адреса. Условный переход с ветвлением на два направления, Бит признака микро- команды ветвления равен 1, бнт идентификации равен О, а два признака режима проверки логических условий управляют передачей через блок коммутации полей логических условий надешифраторы,Формула изобретения5Устройство микропрограммного управления, содержащее регистр адреса, блок памяти микрокоманд, первый коммутатор, регистр микрокоманд, с пер вого по четвертый дешифраторы, блок коммутации, первый и второй элементы ИЛИ, первый и второй элементы И, первую и вторую группы элементов И, элемент И-НЕ, первый и второй тригге ры, информационные входы которых соединены соответственно с выходами первого и второго элементов Ю 1 И,первый и второй информационные входы третьего дешифратора соединены с выходами первого и второго триггеров, выход третьего дешифратора соединен с управляющим входом первого коммутатора, с первого по четвертый информационные входы и выход которого 25 соединены соответственно с выходами полей с первого по четвертый типов микрокоманд блока памяти микрокоманд и с информационным входом регистра микрокоманд, выход поля немодифицируемой части адреса следующей микро- команды которого соединен с информационным входом регистра адреса, выходы которого соединены с адресными входами блока памяти микрокоманд, выходы первого и второго признаков35 проверки логических условий регистра микрокоманд соединены соответственно с первыми входами первого и второго элементов И, а также с информацион ными входами четвертого дешифратора, с первого по четвертый выходы которого соединены соответственно с первого по четвертый управляющими входами блока коммутации, причем четвер тый выход четвертого дешифратора соединен с первым входом элемента И-НЕ, выход поля признака микрокоманды ветвления регистра микрокоманд соединенс первым стробирукщим входом блокакоммутации и вторым входом элементаИ-НЕ, выход которого соединен с вторыми входами первого и второго элементов И, выходы которых соединенысоответственно с первыми входами первого и второго элементов ИЛИ,. с второго по (М+1)-й входы которых (гдеМ - количество входов логических условий устройства) соединены с выхсгдами элементов И первой и второйгрупп соответственно, первые входыкотрых соединены соответственно свходами первой и второй групп логических условий устройства, вторыевходы элементов И первой и второйгрупп соединены срответственно с выходами первого и второго дешифраторов, входы которых соединены соответственно с первым и вторым выходамиблока коммутации, с первого по третий входы синхронизации устройствасоединены соответственно с входамисинхронизации первого и второго триггеров, регистра адреса и регистрамикрокоманд, о т л и ч а ю щ е е с ятем, что, с целью сокращения объемаблока памяти микрокоманд, оно содержит блок памяти кодов логических условий и второй коммутатор, первые ивторые информационные входы которогосоединены с выходами блока памяти кодов логических условий и с выходамирегистра адреса, Кстарших разрядов выхода которого (К-разрядностьрегистра адреса) соединены с адреснымивходами блока памяти кодов логических условий, выход поля выборакода логических условий блока памятимикрокоманд соединен с входом управления второго коммутатора, с первогопо третий выходы второго коммутаторасоединены соответственно с первым ивторым информационными входами и вторым стробируяцим входом блока коммутации,ЗИ 505 начало иглал олоае гЗ=7бит лозотель родги -оДа игалиа лоде 27 устина ла оеодоЬ ( 1 У) а оторого (20( триггерами 7(анец Составитель А.Афанасьев Техред Л. Олийнык Корректор И.МускаЮ Редактор И,Рыбченко Заказ 85/45 Тирюк 704 ПодписноеВНИИПИ Государственного комитета СССРпо делам изобретений и открытий3035, Москва, Ж, Раушская наб., д.4/5 Производственно-полиграфическое предприятие, г.ужгородь ул.Проектная, 4 В рог никролононд 7 зоьску оьОю из Н ггикрогаиолдс ьььа дюка ланями 2 через лонгьо еотоаН, оо зяачению яердои ц О дторого(30) триггера Уояеселце цкцюрнааии оггисипп адреса 1 изяеноЬЧицироцоанной адреснойчасти текущей лгигролон сиге Ф яикролонаяд ои, казотело .омЬра логичесз услодии из дл оанягои 2 кода логич услодий из ола оаияти Ю ыло ы регистра адреса 7оютутируются яа Глодлола лоинутаигог б оннутаиия иол детстд гич. услодио но Ходы р 3 сго Ю и дтроку, деирраторо д зофьи. от знак д.го дылода лонмцкьора Хи Нот/17,узгг нигоогьиоды 5 юка лаияти у он;утируютсо ю длод длока яоннцтатации л

СмотретьЗаявка

4100263, 04.08.1986

ПРЕДПРИЯТИЕ ПЯ Р-6380

ПШЕНИЦЫН ЮРИЙ МИХАЙЛОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммного

Опубликовано: 15.03.1988

Код ссылки

<a href="https://patents.su/4-1381505-ustrojjstvo-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Микропрограммное устройство управления

Случайный патент: Устройство для определения и индикации вектора крена сельскохозяйственных и строительно-дорожных машин