Аналого-цифровой вычислитель логарифмической функции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1247904

Автор: Козлов

Текст

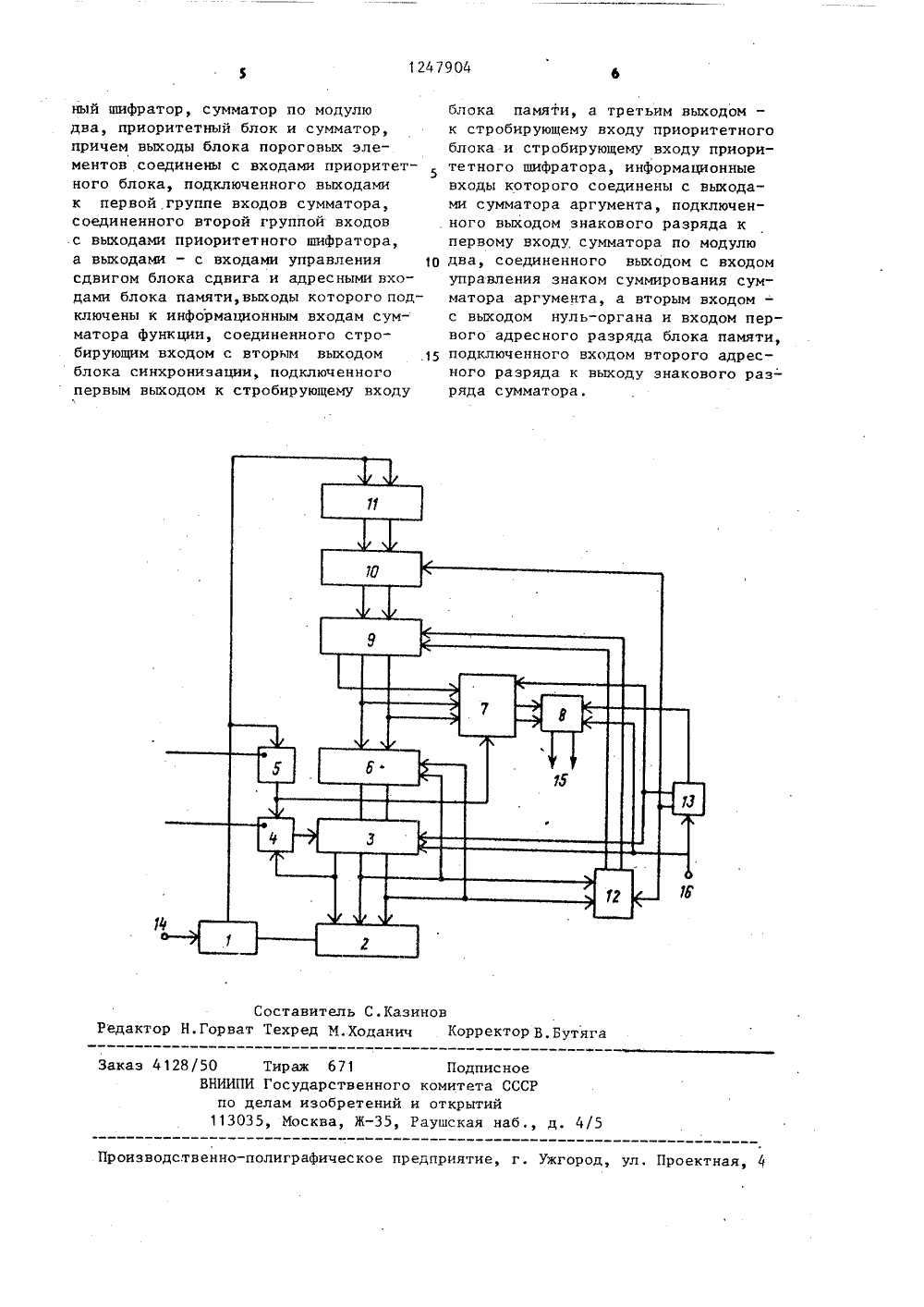

,80124 4, С 06 Р 7/5 94 С ЗОБРЕТЕНИ ОП ИДЕТЕПЬ ВТОРСК(72) Л.Г.Козло (53) 681.335(0 4 Бюл, У 28нина институт кибелушковав88.8) Авторское 011, кл, торское с110, кл, едение вОбработка бщей редКиев: Наукрис. 67.(54) АНАЛОГО-ЦИ ЛОГАРИФМИЧЕСКО ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ свидетельство СССР С 06 С 7/24, 1979.видетельство СССР С 06 С 7/24, 1981, кибернетическую технифизической информации. акцией Б.Н.Малиновскоова думка, 1979, с.166(57) Изобретение относится к областиавтоматики и вычислительной техники.Вычислитель содержит вычитающий узел,цифроаналоговый преобразователь,сумматор аргумента, сумматор по модулюдва, нуль-орган, блок сдвига, блокпамяти, сумматор функции, сумматор,приоритетный блок,блокпороговых элементов, приоритетный шифратори блоксинхронизации. Повышение быстродействия и расширение частотного диапазона обрабатываемых сигналов достигается на основе использования переменного шага уравновешивания входногоаналогового сигнала, что позволяетобеспечить вычисление значений аргумента и функции с точностью до младшего разряда 2 (и-разрядность вычислителя) за время не более 3 и ов работы вычислителя. 1 ил.1 124Изобретение относится к автоматике и вычислительной технике и можетнайти применение в управляющих системах и гибридных вычислительных.устройствах для вычисления в следящем режиме логарифмической функции1 (1 + х) от аналогового сигчалаис представлением результата в цифровой форме,Целью изобретения является повышение быстродействия и расширениечастотного диапазона обрабатываемыхсигналов.На чертеже изображена блок-схемааналого-цифрового вычислителя лога-рифмической функции.Аналого-цифровой вычислитель логарифмической функции содержит вычитающий узел 1, цифроаналоговыйпреобразователь 2, сумматор 3 аргумента, сумматор по модулю два 4,нульорган 5, блок 6 сдвига, блок 7 памяти, сумматор 8 Функции, сумматор 9,приоритетный блок 10, блок 11 пороговых элементов, приоритетный шифратор12, блок 13 синхронизации информационный вход 14, выходы 15 вычислите.ля и вход 16 запуска.Вычислитель работает следующимобразом.Перед началом работы на вход 16подается сигнал, который обнуляетсумматор 8 функции и устанавливаеткод "1" в сумматор 3 аргумента, т.е.п разрядов (где и - разрядность преобразователя 2) младший и и разрядов старшей части сумматора 3 обнуляются, а в младший разряд целой частиэтого сумматора заносится единица.Таким образом, для нулевого значения аргумента х = О сумматор 3 аргумента устанавливается в единичноезначение, так как вычисляется Функция 1 (1-х,) для /х/ ( 1. Блок 7 памяти содержит 4 и слов для выбранной разрядности устройства п,причемв первой половине (странице) блока7 памяти записаны коды функции 1 п(1 + и) для значений аргументах = 2 , 1 = 1, 2 п, а вовторой половине этого блока записаны коды функции Хп (1 - х) для техже значений аргумента, Адресация ктой же или иной половине блока памяти осуществляется сигналом с выхода нуль-органа 5 (первый адресныйразряд блока 7), а адресация внутрикаждой половины блока 7 происходит7904 2 20 рс 50 да (позиционный код). В этом же таку цы из кода старших и разрядов числав сумматоре 3 аргумента и двоичноекодирование его номера. В качествешифратора 12 может использоваться 30 35 40 по сигналам с выхода знакового разряда сумматбра 9 (второй адресныйразряд блока 7) и с остальных выходов сумматора 9 (младшие разряды адреса блока 7).Сигнал, поступающий по входу 16,запускает блок 13 синхронизации,который выдает три серии и импульсовосновная серия - по третьему выходу, задержанная на время ( ,) переходного процесса в приоритетном блоке 1 О, кодирующем элементе 12 и сумматоре 9 - по первому выходу и вторая, задержанная на время ( ) переходного процесса в сумматоре 3 аргумента и блоке 7 памяти - по второмувыходу блока 13,Напряжение ( Л У) рассогласования (между входным напряжением аналогового сигнала (1+х) по входу 14 и напряжением. обратной связи с выхода цифроаналогового преобразователя 2 с выхода вычитающего узла 1 подается на вход нуль в орга 5 и входы блока 11 пороговых элементов. Пороговые элементы блока 11 срабатывают при достижении напряжением рассогласования значений порогов, на которые настроены соответствующие пороговые элементы (например, по двоичному заЬ кону: 1,2, 4 2 условных единиц младшего разряда 2 сумматора 8 функции). В первом такте приоритетный блок 10 в момент времени, определяемые тактовыми импульсами с третьего выхода блока синхронизации, определяет старший по весу пороговый элемент блока 11 из числа сработавших и выдает сигнал на соответствующие выходы, где формируется номер позиции (разряда) в котором находится единица в позиционном коде старшего сработавшего порогового элемента блока 11. Этот позиционный двоичный код представляет собой приращения входного сигнала, округленныедо значения, кратного степени двойки, т.е. представляют собой однуединицу в соответствующем разряде коте шифратор 12определяет аналогичным образом номер старшей единицы вкоде сумматора 3 аргумента, т.е.производится выделение старшей едини 3стандартная микросхема типа 100 ИВ 165 или К 500 ИВ 165 - кодирующий элемент с приоритетом. Из двоичного кода номера позиции с выходов приоритетного блока 10 вычитается код, сформированный шифратором 12, и результат поступает на входы управления сдвигом блока 6 сдвига, который осуществляет передачу содержимого сумматора 3 аргумента на вход того же сумматора 3 со сдвигом на соответствующее число разрядов для суммирования или вычитания с предыдущим значением функции, причем выбор операции суммирования или вычитания производится сумматором 4 по модулю два в зависимости от знака приращения лБ, поступающего с выхода нуль-органа 5, и знака сумматора 3 аргумента функции, т,е. производится операция суммирования, если оба эти знака одинаковы, или операция вычитания для разных знаков, причем операция эта выполняется во втором такте в моменты времени, определяемые тактовыми импульсами с первого выхода блока синхронизации 13, задержанными относительно первого выхода блока синхронизации 13, задержанными относительно первой основной :серии на время , . По этой же серии производится считывание с блока 7 кода функции 1 (1 + ь х) ячейки, адрес которой определяется знаком приращения с выхода нуль-органа 5 (выбирается соответствующая половина блока памяти, где записана функция 1 п (1 + Ах) или 1 п (1 - Ах) в качестве старшего разряда адреса и кодом с выхода сумматора 9 в качестве младших разрядов адреса, причем знаковый разряд сумматора 9 подается на вход второго адресного разряда блока памяти 7 т.е. для приращения сигнала ьх =+2 выбирается функция 1 г. (1 ++ 2 ), записанная по адресу 1 в соответствующей половине блока памяти 7, при этом в каждой половине блока памяти 7 есть две части - для положительных и отрицательных значений показателя степени приращения(2= ) и адресация к соответствующей части производится вторым старшим адресным разрядом блока памяти 7, Код+функции 1 п (1 + 2 ) с выхода блока памяти 7 поступает на вход сумматора 8 функции, где он суммируется247904 5 10 15 20 25 35 40 45 50 55 с предыдущим содержимым сумматора 8 функции. Эта операция выполняется в третьем такте по сигналу с второго выхода блока синхронизации 3, на котором формируется серия импульсов, задержанная относительно предыдущИ серии по первому выходу блока 13 на времяопределяемое временем считывания кода с блока памяти 7.Полученный код. с выхода сумматора 3 аргумента поступает на вход цифроаналогового преобразователя 2, где он преобразуется в аналоговую величину и подается в качестве сигнала обратной связи на второй вход вычитающего узла 1.Вычисление текущих цифровых значений аргумента и функции производится за три такта, причем величина возможных приращений .аргумента и соответственно функции может быть весьма большой. Для максимального. значения входного сигнала вычисление значений аргумента и функции с точ-л ностью до младшего разряда 2 выполняется не более чем за Зп тактов, что обеспечивает повышение быстро 2 Ь действия в среднем в - -2 и3 расширение частотного диапазона вв 2 и/3 раэ. Формула изобретения Аналого-цифровой вычислитель логарифмической функции, содержащий вычитающий узел, подключенный первым входом к информационному входу вычислителя, вторым входом - к выхо-ду цифроаналогового преобразователя, а выходом - к входу нуль-органа и входам блока пороговых элементов, сумматор аргумента, соединенный выходами с входами цифроаналогового преобразователя и информационными входами блока сдвига, а информационными входами - с выходами блока сдвига, и блок синхронизации, подключенный первым выходом к стробирующему входу сумматора аргумента, а входом - к входу запуска вычислителя и входам начальной установки сумматора аргумента и сумматора Функции выходы которого являются выходами вычислителя, о т л и ч а ю щ и й с я тем, что, с целью повышения быстродействия и расширения частотного диапазона обрабатываемых сигналов, в него введены блок памяти, приоритетв Корректор В, Бутяга Заказ 4128/50 Тираж 67ВНИИПИ Государст по делам изобр 113035, Москва,Подписноеомитета СССРоткрытийушская наб., д. 4/5 енног тенин Ж,Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная ный шифратор, сумматор по модулюдва, приоритетный блок и сумматор,причем выходы блока пороговых элементов соединены с входами приоритетного блока, подключенного выходамик первой группе входов сумматора,соединенного второй группой входов.с выходами приоритетного шифратора,а выходами - с входами управления 1 Осдвигом блока сдвига и адресными входами блока памяти, выходы которого подключены к информационным входам сумматора функции, соединенного стробирующим входом с вторым выходом 1блока синхронизации, подключенногопервым выходом к стробирующему входу блока памяти, а третьим выходом -к стробирующему входу приоритетногоблока и стробирующему входу приоритетного шифратора, информационныевходы которого соединены с выходами сумматора аргумента, подключенного выходом знакового разряда кпервому входу сумматора по модулюдва, соединенного выходом с входомуправления знаком суммирования сумматора аргумента, а вторым входом -с выходом нуль-органа и входом первого адресного разряда блока памяти,подключенного входом второго адресного разряда к выходу знакового разряда сумматора.

СмотретьЗаявка

3863974, 27.02.1985

ОРДЕНА ЛЕНИНА ИНСТИТУТ КИБЕРНЕТИКИ ИМ. В. М. ГЛУШКОВА

КОЗЛОВ ЛЕОНИД ГРИГОРЬЕВИЧ

МПК / Метки

МПК: G06F 7/556, G06G 7/24

Метки: аналого-цифровой, вычислитель, логарифмической, функции

Опубликовано: 30.07.1986

Код ссылки

<a href="https://patents.su/4-1247904-analogo-cifrovojj-vychislitel-logarifmicheskojj-funkcii.html" target="_blank" rel="follow" title="База патентов СССР">Аналого-цифровой вычислитель логарифмической функции</a>

Предыдущий патент: Логарифмический преобразователь

Следующий патент: Функциональный генератор

Случайный патент: Устройство для циклового программного управления манипуляторами