Сумматор слагаемых аргумента периодической функции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 617775

Автор: Абрамович

Текст

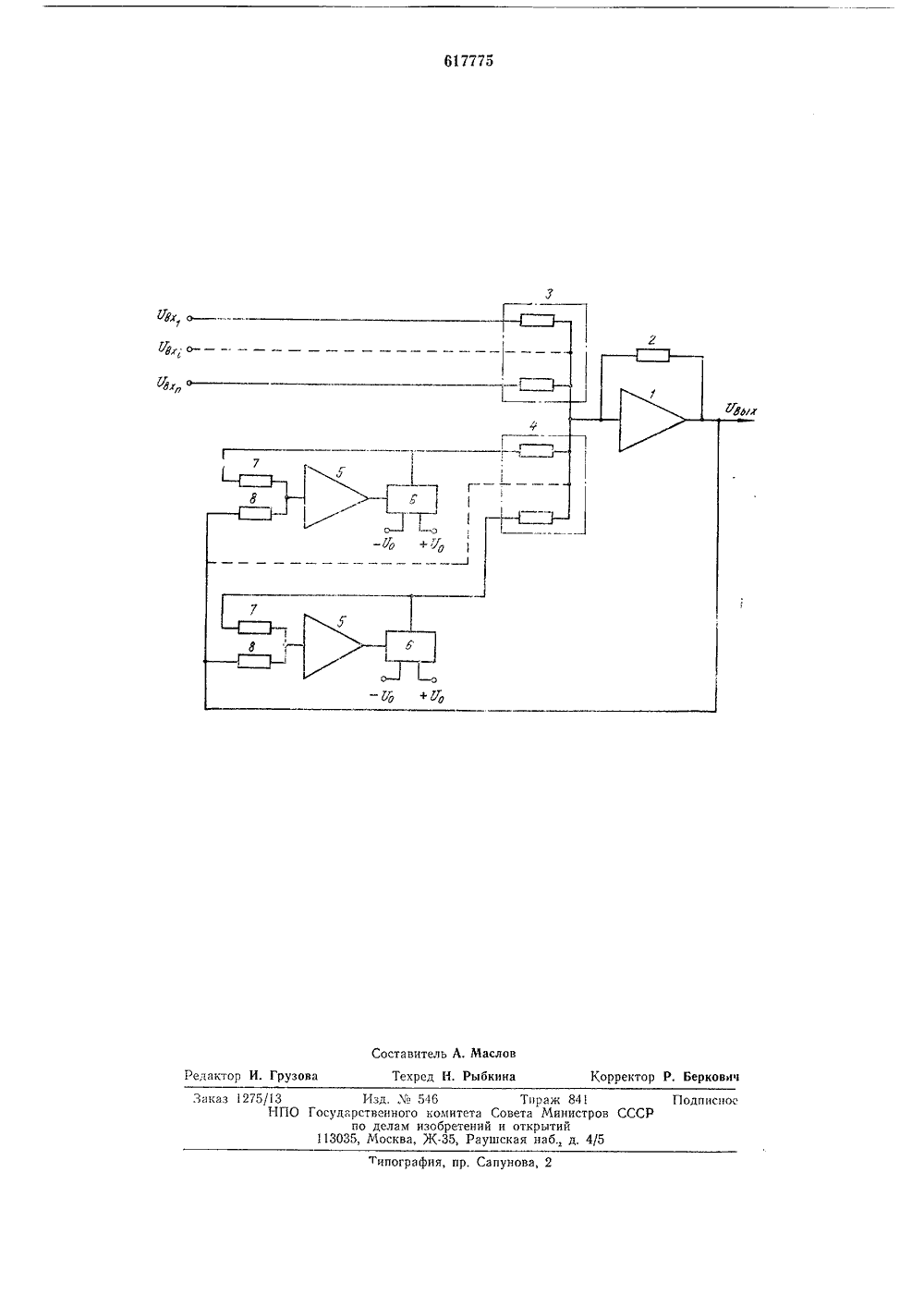

Союз Соеетскик Социалистических Республик1) Дополнительное к авт. свид-ву 36984/18-2 1, Кл.2 б 0667/14 2) Заявлено 02.03. ки М с присоединением з осударственныи комитет оеета Министров СССР по делам изобретенийи открытий рио,ритет(54) СУММАТОР СЛАГАЕМЫХ АРГУМЕНТА ПЕРИОДИЧЕСКОЙ ФУНКЦИИго н зоне выходного м больше диаемой величины, х, тем меньше 25 то увеличивает ости. Кроме тоаче увеличение вызывает сущести значительное 30 Изобретение относится к аналоговым средствам автоматики и вычислительной техники и может использоваться в электронных моделирующих устройствах и системах автоматического управления, например, движущихся объектов, когда требуется определить значение периодической функции, аргумент которой является суммой нескольких слагаемых.Известны сумматоры слагаемых аргумен та периодической функции, представленных сигналами в аналоговой форме, содержащие суммирующий усилитель с входным узлом суммирования из а ветвей 11.В таких сумматорах диапазон изменения 1 результата суммирования - значения аргумента х - составляет +п(и+Ь), где б - возможное превышение слагаемыми значений пределов периода + и, т. е. не меньше п периодов функции. 2 Г 1 ри располагаемом диапа напряжения сумматора че пазон изменения представля в данном случае аргумента электрический масштаб, ч инструментальные погреши го,в рассматриваемой зад диапазона изменения х вь венное усложнение задачи понижение точности последующе фу кционального преобразования.Наиболее близким техническим решением к изобретению является сумматор слагаемых аргумента периодической функции, содержащий суммирующий усилитель, первая группа входов и выход которого служат соответственно группой входов и выходом сумматора, и п переключателей, входы которых подключены к двум источникам эталонных сигналов противоположных знаков, а выходы подсоединены к второй группе входов суммирующего усилителя 21.К недостаткам прототипа следует отнести малый запас устойчивости, большую нагрузку на источники суммируемых сигналов и относительную сложность.Цель изобретения - повышение устойчивости работы, увеличение входного сопротивления и упрощение сумматора.Поставленная цель достигается тем, что сумматор содержит п компараторов с последовательно возрастающими по отношению к полупериоду функции порогами срабатывания, измерительный вход каждого из которых подключен к выходу сумматора, а установочный вход и выход подсоединены к выходу и управляющему входу соответствующего переключателя.На чертеже приведена схема суммазора.Сумматор содержит суммирующий усилител, сосОящ 1 Из операционного усилителя 1 с резистором 2 Обратной связи, входи:ми резисторами 3 (для входных сигналов У 1=1 - п) и 4, а также необходимое число компараторов 5 с управляевсыми переключателями 6. Установочным входом каждого компаратора является резистор 7. Измерительным входом каждого компаратора служит резистор 8.На измерительный вход - резистор 8 - каждого компаратора 5 подается выходной сигнал суммирующего усилителя 1, а на установочный вход - резистор 7 - поступает напряжение с выхода переключателя 6, пропускающего опорное напряжение + с.о той полярности, которая совпадает с полярностью на входе усилителя компаратора 5. Одновременно опорное напряжение той же полярности подается и на один из входных резисторов 4 суммирующего усилителя. Тем самым обеспечивается переключение знака дополнительного сигнала на входе суммирующего усилителя 1 при переходе выходного напряжения сумматора за пределы полупериода какого-либо знака, а поскольку абсолютная величина дополнительного сигнала также соответствует полупериоду (за счет подбора величины сопротивления резисторов 4), то значение выходного сигнала У изменяется сразу на величину одного периода.Фазировка элементов сумматора такова, что внешние контуры (усилитель - компаратор - переключатель) образуют отрицательную обратную связь, а внутренние контуры (компаратор переключатель) - положительнуюю.Таким образом, автоматически, в зависимости от суммы исходных сигналов, определенное число переключателей 6 выдает сигналы одной полярности, а остальные - другой полярности, обеспечивая нужный знак и величину результирующего сигнала, приводящие любое значение суммьс кодных сигналов У,с к одному периоду.Если специально скорректировать уровни срабатывания компараторов, чтобы они были больше величины полупериода на малые величины Л;, то устойчивость работы (исключение зуммерного режима) повышается, так как гарантируется, что при переключении каждого переключателя 6 не возникнет состояния, при котором, за счет неточности элементов, не создадутся условия обратного переключения.Однако может случиться и так, что переключаются сразу два переключателя или более, тогда они сразу же дол.кны возвратиться в прежнее состояние, такой процесс 5 10 15 20 25 30 35 40 45 50 55 60 может повторяться. Для устранения этой возможности и обеспсчеипя гарантированной устойчиоси раб 7 суммаОра нужно сделать волиины Л рс 3 ыми для каждого компаратора 5, В этом случае, по мере изменения первичной суммы, всегда первыми срабатывают компараторы, скорректированные па меньшие значения Л а затем следующие в псрядке возрастания (или убывания, если абсолютное значение суммарного сигнала уменьшается) значений их Л Диапазон значений выходного сигнала сумматора, по мере подхода значения первичной суммы к границам своего диапазона, расширяется, но нс превышает в каждую сторону полупериода, увеличенного на максимальную величину ЛКорректировка уровней срабатывания компараторов 5 проводится измепснием соотношения сопротиьлепий резисторов 7 и 8. Сумматор слагаемых аргу.;сента пер иодической фус.кц 1 позволсСт 1 Сза исимо От диапазона нзмснения суммы слагаемых, при распсласаемом диапазоне 1 мсе 11 я выходного напряжения суммируюцего усилителя, получить ыходной сигнал в наибольшем масштабе, что обеспечивает повышение точности его вычисления и предопределяет упрощение с одноремеым значительньсм повышением точности последующего оспроизедения псриодической функции,Формула изобретенияСумматор слагаемых аргумента периодической функции, содержащий суммирующий усилитель, первая группа входов и выход которого являотса соответственно группой входов и выходом сус.1;."Ора, и и сс 17 еключасслс;, ходы:оторых иодклочены к двум источникам эталонных сигналов противоположных знаков, а выходы подсоединены к второй группе входов суммирусощего усилителя, отличающийся тем, что, с целью повышения устойчивосси работы, увеличеия входного сопротивления и упрощения сумматора, он содержит 17 компараторов с последовательно возрастающими по отношению к полупериоду функции порогами срабатывания, измерительный вход какдого из которых подключен к выходу сумматора, а установочный вход и выход подсоединены к выходу и управляющему входу соответствующего переключателя.Источники информации,принятые по внимание при экспертизе 1, Справочник по аналоговой вычислительной технике. Под ред. Г. Б, Пухова, Киев, 1975.2. Коган Б. Я. Электронные моделирующие устройства и их применение для исследовас;ия систем автоматического регулирован 11 я, М Физматизд, 1959, с, 234 - 237,, д Редактор И. Грузова ставитель А. Маслов род И. Рыбки Из.,цп 545 ударственного комитета по делам изобретении 13035, Москва, Ж, РауТираовета Ми открьская на типография, пр, Сапунова,ж 841инистротий ПодписноеССР

СмотретьЗаявка

2336984, 02.03.1976

ПРЕДПРИЯТИЕ ПЯ А-1427

АБРАМОВИЧ МАРК СЕМЕНОВИЧ

МПК / Метки

МПК: G06G 7/14

Метки: аргумента, периодической, слагаемых, сумматор, функции

Опубликовано: 30.07.1978

Код ссылки

<a href="https://patents.su/3-617775-summator-slagaemykh-argumenta-periodicheskojj-funkcii.html" target="_blank" rel="follow" title="База патентов СССР">Сумматор слагаемых аргумента периодической функции</a>

Предыдущий патент: Устройство для обработки информации, зарегистрированной на магнитном носителе

Следующий патент: Устройство запоминания и многократного воспроизведения электрических импульсов

Случайный патент: 354204