Блок вычисления логических функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1800465

Авторы: Зарембовская, Мельников, Новиков, Фадеева

Текст

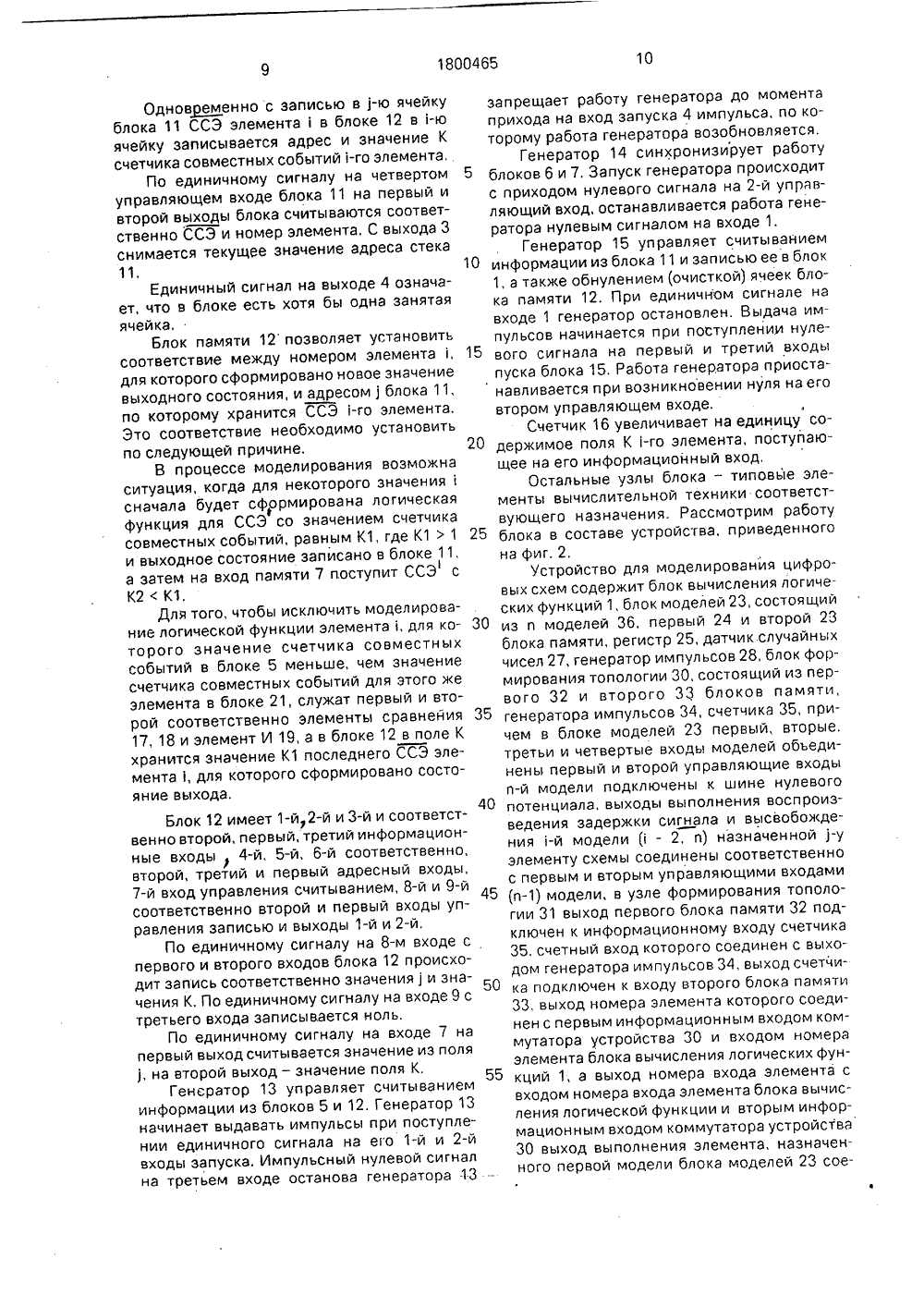

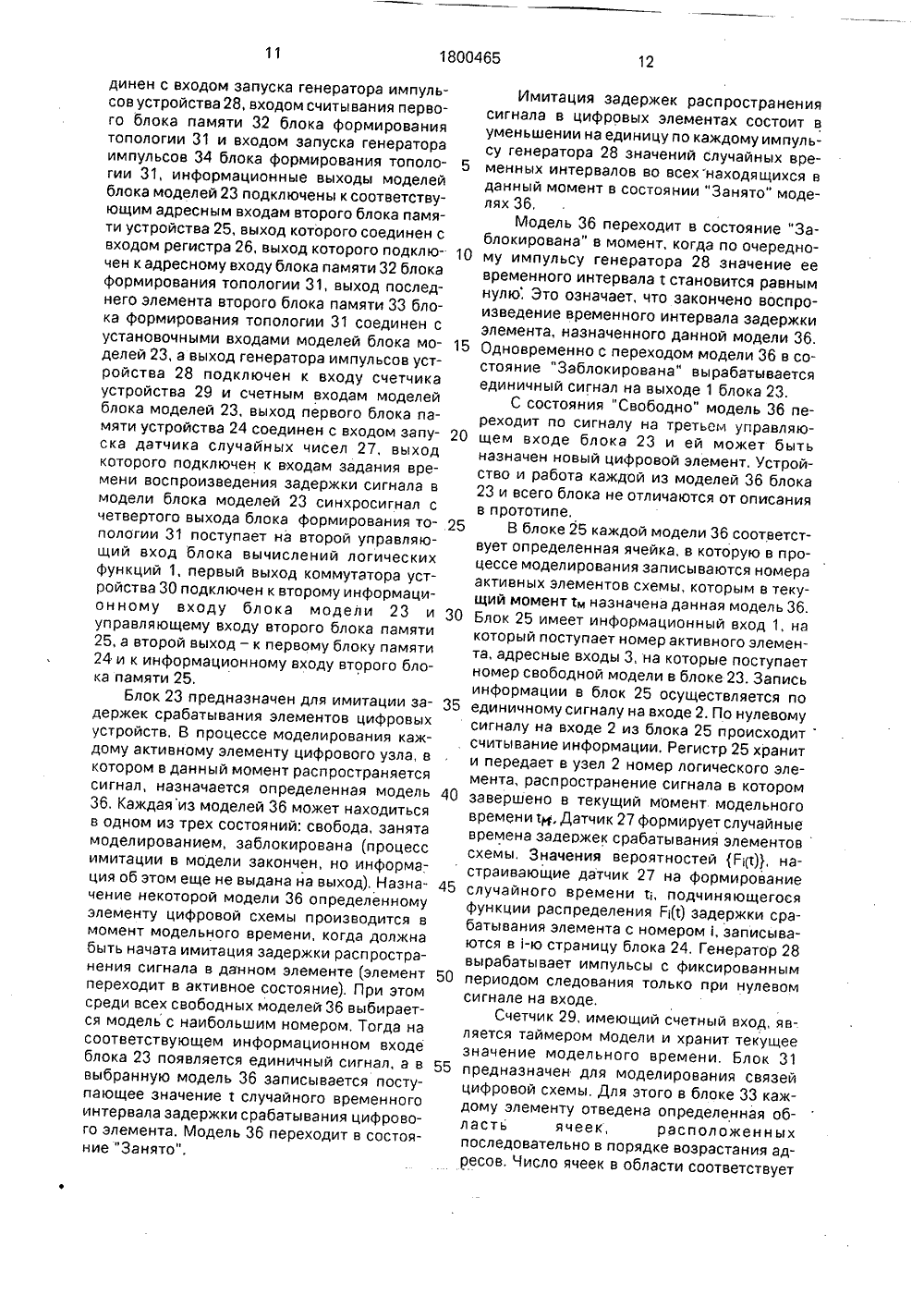

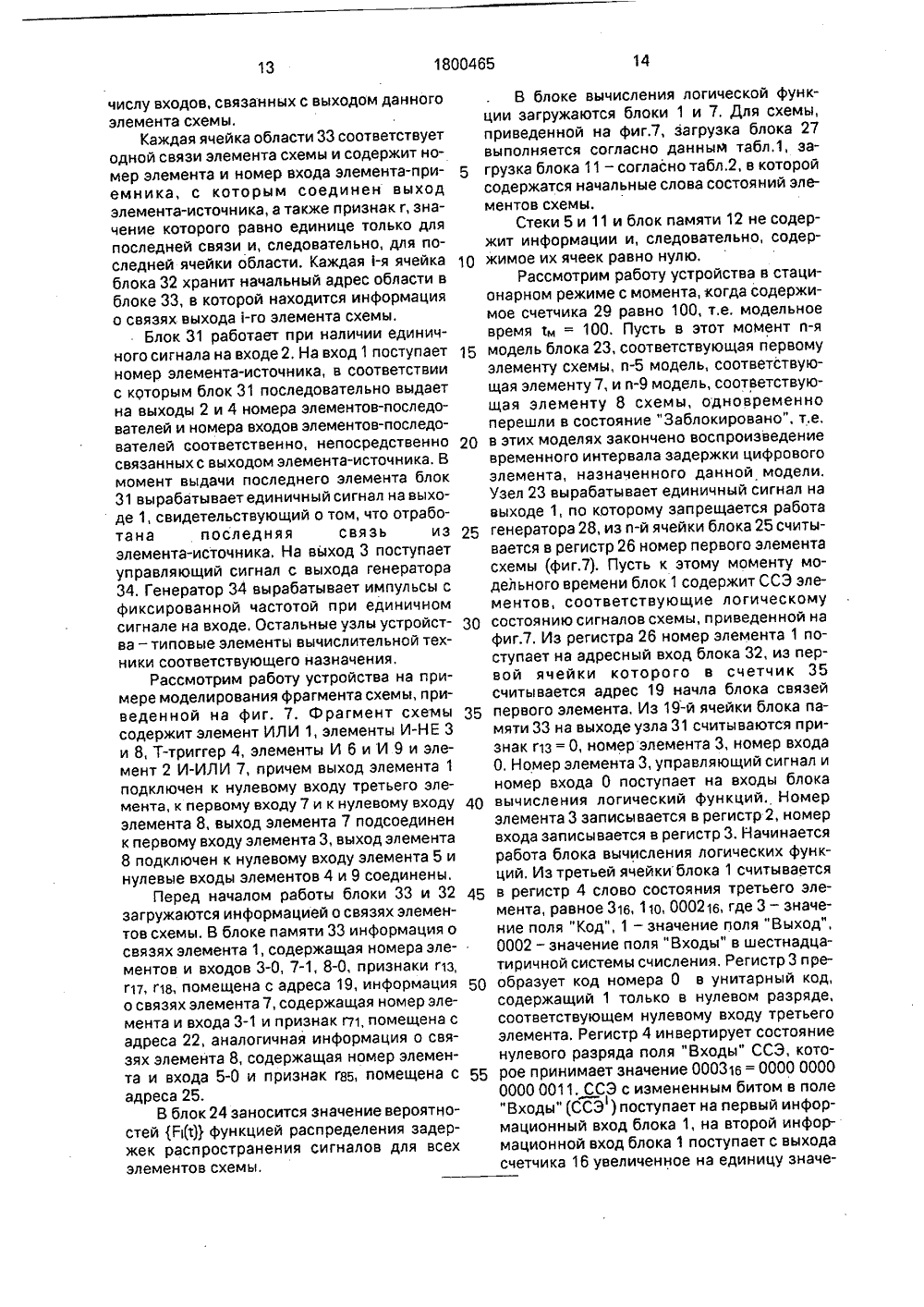

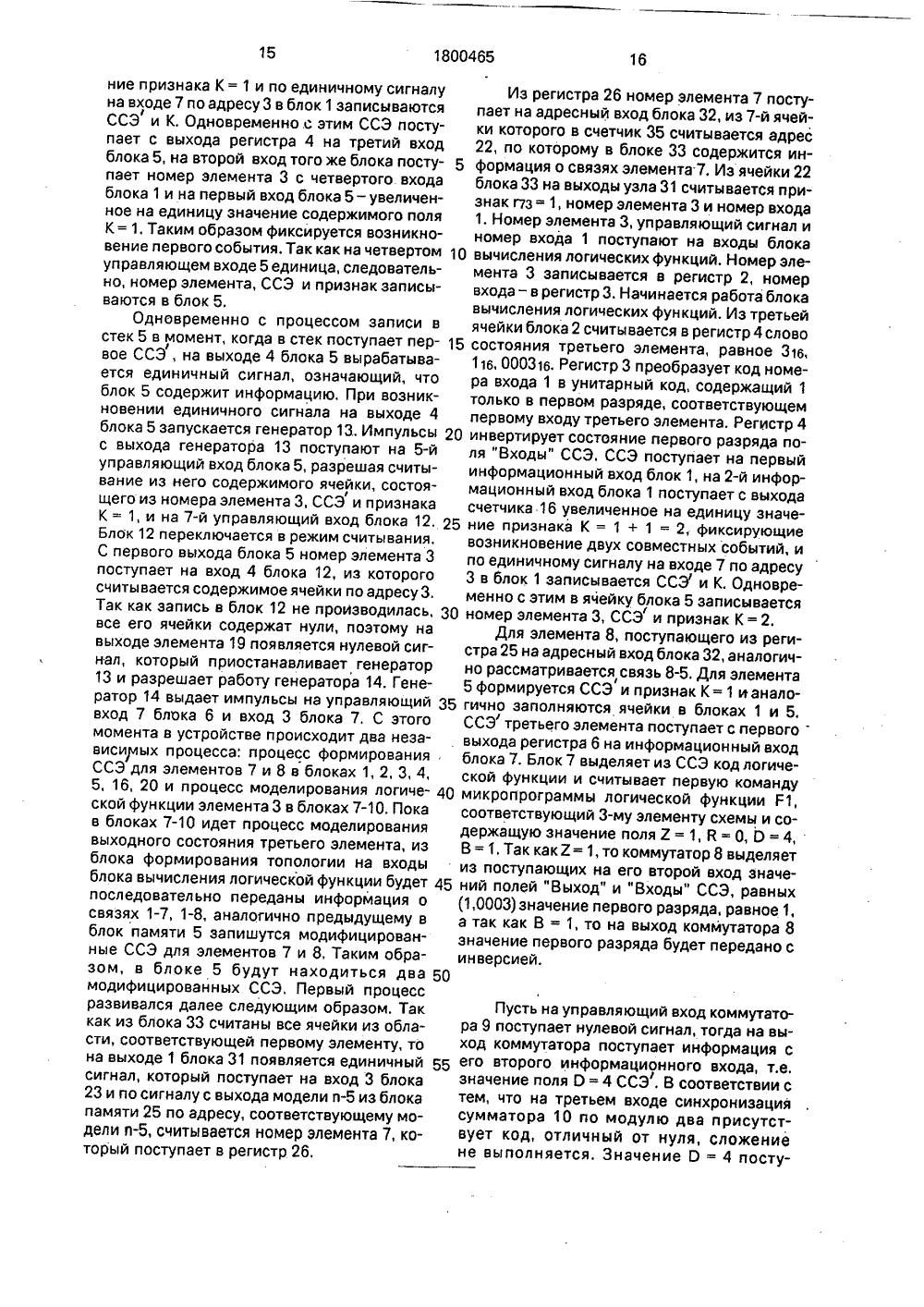

(57) Изобретен ной технике, а ным стохастиче использовано ретных устройс рования средс Цель изобрете Для этого допо памяти, один ре сравнения, три мент И, два эле ЧЕ КИ ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕВЕДОМСТВО СССР(71) Минский радиотехнический институт(54) БЛОК ВЫЧИСЛЕНИЯ ЛОГИФУНКЦИЙ Изобретение относится к вычислительной технике, а именно к специализированным стохастическим моделям, и может быть использовано в системах испытания дискретных устройств и автоматизации проектирования средств вычислительной техники.Цель изобретения - повышение точности вычислений.На фиг, 1 приведена структурная схема предлагаемого блока вычисления логических функций; на фиг, 2 - структурная схема устройства, в составе которого рассматривается работа блока вычисления логических функций; на фиг, 3 - структурная схема блока формирования топологии; на фиг. 4 - функциональные обозначения некоторых цифровых одновыходных элементов; на фиг.5 - графы микропрограмм; на фиг. 6 - структура слова состояния элемента; на фиг, 7 - фрагмент цифровой схемы, на примере моделирования которой рассматривается функционирование устройства, приведенного на фиг. 2.Блок вычисления логических функций, содержащий первый 1, второй 7 блоки памяти, первый 2, второй 3, третий 4 регистры,2ие относится к вычислитель- именно к специализированским моделям, и может быть в системах испытания дисктв и автоматизации проектитв вычислительной техники. ния - повышение точности, лнительно введены три блока гистр, счетчик, два элемента генератора импульсов, элемента задержки, 7 ил., 2 табл дешифратор 20, первый 9 и второй 8 коммутаторы, сумматор 10 по модулю два, причем информационный вход первого регистра 2 является первым входом блока, входы управления записью первого 2 и второго 3 регистров подключены к второму входу блока, информационный вход второго регистра 3 является третьим входом блока, а его выход подключен к входу дешифратора 20, выход которого соединен с входом управления словом состояния элемента третьего регистра 4, информационный вход которого соединен с первым выходом первого блока памяти 1, а выход - с первым информационным входом первого блока памяти 1, выход первого регистра 2 подключен к первоМу адресному входу первого блока памяти 1. вход управления считыванием второго блока. памяти 7 соединен с выходом первого коммутатора 9 и с первым входом сумматора 10 по модулю два, первый и второй выходы второго блока памяти 7 соединены соответственно с первым и вторым управляющими входами второго коммутатора 8, выход которого подключен к управляющему входу первого коммутатора 9 и к второму10, Для минимизации таких ситуаций и тем самым для повышения бьстродействия устройства в блоке 5 принята дисциплина ЬГО, которая позволяет при одновременном хранении в блоке памяти 20 ССЭ с одним измененным битом и ССЭ с двумяизмененными битами выбрать первым на обработку ССЭ с двумя измененными битами, а ССЭ с одним измененным битом не обрабатывать,Пусть первым в регистр 6 записывается информация, соответствующая связи (1-7), Блок 7 последовательно выдает микрокоманды для выполнения микропрограммыфункции Г 4, которая соответствует элементу 7. Пусть за время, пока идет процесс форми 45 50 55 третьего элемента в момент модельноговремени 100 уже вычислялось значение выхода, На первый вход схемы сравнения 18поступает значение признака К = 2 из блока5 на вход 2 - значение К =1 с выхода 2 блока 512, Так как поступившее на первый входблока 16 значение больше, чем значение К,поступившее на вход 2, то на выходе блока18 - единица, на выходе элемента 19 возникает единичный сигнал, который запретит 10работу генератора 13, разрешит выдачу импульсов генератору 14 и, следовательно, дляэлемента 3 будет моделироваться значениевыходного состояния. Это выполняется потому, что в ССЭ, поступающем из блока 5, 15учтены два события и именно это ССЭ порождаетдостоверное состояние выхода элемента,По окончании выполнения всех командмикропрограммы логической функции элемента 3 выше описанным способом, выход3-го элемента изменяет состояние (становится единичным), Теперь и блок 11 для элемента 3 запишется ССЭ с состояниемвыхода, полученным с учетом всех измененных битов в поле "Входы", а в блок 12 поадресу = 3 запишется значение адреса )з =23 и К=2.Для элемента 5 будут проведены такиеже операции, выход элемента 5 при поступлении единицы с выхода элемента 8 на вход1 элемента 5 изменяет свое состояние и длянего в блоке 11 заполняется ячейка по адресу ) = 24, а в блоке 12 по адресу= 5 запишется)5=24 и К=1. 35Вышебыл рассмотрен случай для 3-гоэлемента, когда в блоке 7-10 два раза вычислялось новое состояние выхода, причем достоверным оказалось только второгосостояние в ССЭ. Эта ситуация возникла 40потому, что к моменту формирования входови записи ССЭ для 3-го элемента в стек 20предыдущее ССЭ для этого же элементауже поступило на обслуживание в блоке 7 рования состояние выхода элемента 7, в стек 5 заполняются ячейки; ССЭ для треть-. его элемента, соответствующее связи (1-3), ССЭ для восьмого элемента, соответствующее связи (1-8), ССЭ для третьего элемента, соответствующее связи (7-3) с учетом измененного бита для связи (1-3). Таким образом в стек 5 последовательно записаны ССЭ для третьего элемента с К = 1, ССЭ для восьмого элемента с К = 1 и ССЭдля третьего элемента с К = 2, Так как стек 5 считывает информацию по принципу ЬРО, то в момент завершения вычисления состояния выхода для элемента 7 в блоках 7-10 первым на выполнение логической функции из блока 5 будет считано ССЭ третьего элемента с К = =2, содержащее достоверную информацию о всех измененных битах в поле "Входы". В блок 11 запишется ССЭ третьего элемента с измененным состоянием выхода и в блок 12 по адресу 3 запишется )з и К = 2.Когда по очередному импульсу генератора 13 на выходе блока 5 появится ССЭ третьего элемента= 3 и К =- 1, по адресу 3 из блока 12 считывается значение)з, отличное от нуля, на 1 и 2 входы схемы сравнения 18 поступит соответственно К = 1 и К = 2, на выходе схемы 18 появится ноль, который поступит на вход 2 элемента 19. Нулевой сигнал с выхода блока 19 не разрешает работу генератора 14, сбрасывает в ноль регистр 6 и разрешает генератору 13 выдачу импульса для считывания очередной ячейки из блок 5. ССЭ с признаком К = 1 не передается на моделирование логической функции, т,к. модифицированный разряд ССЭ с . признаком К = 1 уже учтен и ССЭ с признаком К.= 2 и состояние выхода элемента 3. записанное в блоке 11 определено уже с учетом связи 1-3,Кода все ячейки стека 5 отработаны, на его четвертом выходе появляется нулевой сигнал, что означает, что все ячейки блока 5, содержащие модифицированные ССЭ -х элементов, считаны и последнее ССЭ/передано на выполнение логической функции, Нулевой сигнал с выхода 4 блока 5 поступает на первый управляющий вход генератора 13. запрещает его работу и этот ке единичный сигнал на входе 3 генератора 15, свидетельствует о том, что к моменту запуска генератора 15 состояние выхода последнего элемента, для которого выполнялась микропрограмма логической функции, определено и информация, соответствующая этому элементу, записана в блоке 11 и 12, На третьем управляющем входе генератора 15 должен быть нулевой сигнал.Генератор 15 управляет считыванием информации из блока 11, обнулением ячеек10 блока 12 и записью считанных ячеек из блока 11 в блок 1, а также выдает управляющий сигнал на вход блока 23, где осуществляется назначение элементу свободной модели для временного моделирования в блоке 23, По каждому импульсу генератора 15 из блока 11 считывается информация. На выходе 2 блока 11 появляется номер элемента,который поступает на первый адресный вход 6 блока 12 и на второй адресный вход 5 блока 1. ССЭ, соответствующее (для первого рассмотренного случая) 3-му элементу, с первого выхода блока 11 поступает на информационный вход 3 блока 1, Этот же импульс поступает через элемент задержки 22 на входы 8 и 9 блока 1 и 12 соответственно, и разрешает запись информация в эти блоки,На вход 3 блока 1, поступает ССЭ, запись которого осуществляется по адресу 3 на входе 5, В блок 12 по этому же адресу поступит,О с третьего информационного входа, т.е; ячейка обнулится, Коммутатор 30 передает информацию с выходов блока вычисления логической функции на входы блока 24, 25 и блока 23. Блок 25 переключается в режим записи, В блоке 23 отыскивается свободная (и)-я модель и на (и)-м выходе блока 23 вырабатывается сигнал, по которому в (и)-ю ячейку блока 25 запишется номер элемента 3, которому назначается (и)-я модель. Из 3-й страницы блока 24 в датчик 27 считвыается значение вероятностей (Гз(т по которым датчик 27 формирует случайную временную задержку элемента тз. Значение 1 записывается в (и)-ю модель 11.Для элементов 7, 6 и 5 по очередным импульсам генератора 13 будут последовательно выполнены шаги, аналогичные тем, которые описаны для элемента 3. В результате этого в блок 1 произойдет запись информации по адресам 7, 8 и 5, поступающей из блока 11, по этим же адресам в блоке 12 обнулится содержимое ячеек, В блоке 23 элементам 7, 8 и 5 назначатся свободные модели, а датчиком 27 сформируются случайные временные задержки элементов, В момент, когда вся информация из блока 11 будет переписана в блок 1, на выходе 4 блока 11 появится нулевой сигнал, который запретит генератора 15 выдачу импульсов, К этому времени произойдет обнуление содержимого всех занятых ячеек в блоке 12 и назначение всем элементам свободных моделей в блоке 23.В блоке 23 не больше моделей 11 в состоянии "Заблокировано", на его выходе выполнения вершины сбрасывается сигнал, по которому запрещается работа генератора 15 20 25 30 35 40 45 50 55 34, разрешается работа генератора 28, импульсы которого начинают поступать на входы моделей 11 блока 12, Дальнейшая работа устройства аналогична.Таким образом, предлагаемый блок обладает рядом преимуществ перед прототипом, основным из которых является повышение точности моделирования цифровых схем, Повышение точности достигается за счет учета ситуации возникновения совместных событий, часто встречающейся в процессе моделирования цифровых схем и оказывающей большое влияние на достоверность результатов моделирования,Предложенный блок обладает также хорошим быстродействием, которое обеспечивается за счет совмещения в устройстве двух независимых, параллельных процессов: процесса накапливания модифицированных слов состояний элементов и процесса вычисления. Это приводит к сокращению времени моделирования и позволяет экономно использовать оборудование. В структуре устройства использованы типовые элементы вычислительной техники, что облегчает конструирование.Формула изобретения Блок вычисления логических функций, содержащий первый, второй блоки памяти, первый, второй, третий регистры, дешифратор, первый и второй коммутаторы, сумматор по модул ю два, причем информационный вход первого регистра является первым входом блока, входы управления записью первого и второго регистров подключены к второму входу блока, информационный вход второго регистра является третьим входом блока, а его выход подключен к входу дешифратора, выход которого соединен с входом управления словом состояния регистра, информационный вход которого соединен с первым выходом первого блока памяти, а выход - с первым информационным входом первого блока памяти, выход первого регистра подключен к первому адресному входу первого блока памяти, вход управления считыванием второго блока памяти соединен с выходом первого коммутатора и с первым входом сумматора по модулю два, первый и второй выходы второго блока памяти соединены соответственно с первым и вторым управляющими входами второго коммутатора, выход которого подключен к управляющему входу первого коммутатора и к второму входу сумматора, по модулю два, третий и четвертый выходы второго блока памяти соединены соответственно с первым и вторым информационными входами первого коммутатора. о т л и ч а ю щ и й с я тем, что, с целью5 10 15 20 25 30 35 40 45 50 повышения точности, дополнительно введены третий, четвертый и пятый блоки памяти, четвертый регистр, счетчик, первый и второй элементы сравнения, первый, второй и третий генераторы импульсов, элемент И, первый и второй элементы задержки, причем второй информационный вход первого блока памяти соединен с первым информационным входом третьего блока памяти и с выходом счетчика, вход которого подключен к второму выходу первого блока памяти, третий информационный вход первого блока памяти соединен с первым выходом четвертого блока памяти, второй адресный вход первого блока памяти подключен к первому адресному входу пятого блока, к второму выходу четвертого блока памяти и является первым выходом блока, вход управления считыванием первого блока памяти соединен с входом первого элемента задержки и с вторым входом блока, выход первого элемента задержки соединен с первым входом управления записью первого блока памяти, с первым входом запуска первого генератора импульсов и с входом управления записью третьего элемента памяти, второй вход управления записью первого блока подключен к выходу второго элемента задержки и к первому входу управления записью пятого блока памяти, второй информационный вход третьего блока памяти соединен с выходом первого регистра, а третий информационный вход - с выходом третьего регистра, вход управления считыванием третьего блока памяти подключен к выходу первого генератора импульсов и к входу управления считыванием пятого блока памяти, первый выход третьего блока памяти. соединен с первым информационным входом четвертого регистра и с первым адресным входом пятого блока памяти, второй выход третьего блока памяти подключен к второму информационному входу четвертого регистра, а третий выход - к третьему информационному входу четвертого регистра и к первому входу второго элемента сравнения, четвертый выход третьего блока памяти соединен с вторым входом запуска первого генератора импульсов. с входом останова третьего генератора импульсов и является вторым выходом блока, вход сброса в ноль четвертого регистра соединен с входами останова и запуска соответственно первого и второго генератора импульсов и с выходом элемента И, четвертый информационный вход четвертого регистра подключен к управляющему входу первого коммутатора, а вход управления записью соединен с выходом сумматора по модулю два, с входом управления записью четвертого блока памяти, с вторым входом управления записью пятого блока памяти, вход управления считыванием четвертого регистра подключен к входу управления записью второго блока памяти и к выходу второго генератора импульсов, вход останова которого соединен с входом управления считыванием второго блока памяти и с входом пуска первого генератора импульсов, первый выход четвертого регистра соединен с информационным входом второго блока памяти, с вторым информационным входом второго коммутатора, с третьим входом сумматора по модулю два и с первым информационным входом четвертого блока памяти, второй выход четвертого регистра подключен к второму информационному входу четвертого блока памяти и к третьему адресному входу пятого блока памяти, первый информационный вход которого соединен с третьим выходом четвертого регистра, вход управления считыванием четвертого блока памяти подключен к выходу третьего генератора импульсов и к входу второго элемента задержки, третий выход четвертого блока памятисоединен с вторым информационным входом пятого блока памяти, а четвертый выход четвертого блока памяти подключен к первому входу пуска третьего генератора импульсов. второй вход пуска которого соединен с первым входом сумматора по модулю два, третий информационный вход пятого блока памяти подключен к шине нулевого потенциала, первый выход пятого блока памяти соединен с входом первого элемента сравнения, выход которого подключен к первому входу элемента И, а второй выход пятого блока памяти соединен с вторым входом второго элемента сравнения, выход которого подключен к второму входу элемента И.з 1166 ВНИИП Составитель И.ЗарембовскТехред М,Моргентал Тираж Подписноеосударственного комитета по изобретениям и открытиям при ГКНТ С 113035, Москва, Ж, Раушская наб., 4/55 10 15 20 30 35 40 45 50 55 входу сумматора 10 по модулю два, третий и четвертый выходы второго блока памяти 7 соединены соответственно с первым и вторым информационными входами первого коммутатора 9, дополнительно введены третий 5, четвертый 11 и пятый 12 блоки памяти, четвертый регистр 6, счетчик 16, первый 17 и второй 18 элементы сравнения, первый 13, второй 14 и третий 15 генераторы импульсов, элемент И 19, первый 21 и второй 22 элементы задержки, причем второй информационный вход первого блока памяти 1 соединен с первым информационным входом третьего блока памяти 5 и выходом счетчика 16, вход которого подключен к второму выходу первого блока памяти 1, третий информационный вход первого блока памяти 1 соединен с первым выходом четвертого блока памяти 11, второй адресный вход первого блока памяти 1 подключен к первому адресному входу пятого блока памяти 12, к второму выходу четвертого блока памяти 11 и является первым выходом блока, вход управления считыванием первого блока памяти 1 соединен с входом первого элемента .25 задержки 21 и с вторым входом блока, выход первого элемента задержки 21 соединен с первым входом управления записью первого блока памяти 1, первым входом запуска первого генератора импульсов 13 и входом управления записью третьего блока памяти 5, второй вход управления записью первого блока памяти 1 подключен к выходу второго элемента задержки 22 и к первому входу управления записью пятого блока памяти 12, второй информационный вход третьего блока памяти 5 соединен с выходом первого регистра 2, а третий информационный вход - с выходом третьего регистра 4, вход управления считыванием третьего блока памяти 5 подключен к выходу первого генератора импульсов 13 и входу управления считыванием пятого блока памяти 12, первый выход третьего блока памяти 5 соединен с первым информационным входом четвертого регистра 6 и с вторым адресным входом пятого блока памяти 12, второй выход третьего блока памяти 5 подключен к второму информационному входу четвертого регистра 6, а третий выход - к третьему информационному входу четвертого регистра 6 и к первому входу второго элемента сравнения 18, четвертый выход третьего блока памяти 5 соединен с вторым входом запуска первого генератора импульсов 13, с входом останова третьего генератора импульсов 15 и является вторым выходом блока, вход сброса в ноль четвертого регистра 6 соединен с входами останова и запуска соответственно первого 13 и второго 14 генераторов импульсов и с выходом элемента И 19, четвертый информационный вход четвертого регистра 6 подключен к управляющему входу первого коммутатора 9, а вход управления записью соединен с выходом сумматора 10 по модулю два, с входом управления записью четвертого блока памяти 1.1, с вторым входом управления записью пятого блока памяти 12, вход управления считыванием четвертого регистра 6 подключен к входу управления записью второго блока памяти 7 и к выходу второго генератора импульсов 14, вход останова которого соединен с входом управления считыванием второго блока памяти 7 и с входом пуска первого генератора импульсов 13, первый выход четвертого регистра 6 соединен с информационным входом второго блока памяти 7, вторым информационным входом второго коммутатора 8, с третьим входом сумматора 10 по модул:о два и с первым информационным входом четвертого блока памяти 11, второй выход четвертого регистра 6 подключен к второму информационному входу четвертого блока памяти 11 и к третьему адресному входу пятого блока памяти 12, первый информационный вход которого соединен с третьим выходом четвертого регистра 6, вход управления считыванием четвертого блока памяти 11 подключен к выходу третьего генератора импульсов 15 и к входу второго элемента задержки 22, третий выход четвертого блока памяти 11 соединен с вторым информационным входом пятого блока памяти 12, а четвертый выход четвертого блокапамяти 11 подключен к первому входу пуска третьего генератора импульсов 15, второй вход пуска которого соединен с первым входом сумматора 10 по модулю два, третий информационный вход пятого блока памяти 12 подключен к шине нулевого потенциала,первый выход пятого блока памяти 12 соединен с входом первого элемента сравнения 17, выход которого подключен к первому входу элемента И 19, а второй выход пятого блока памяти 12 соединен с вторым входом второго элемента сравнения 18, выход которого подключен к второму входу элемента И 19.БлОк предназначен для вычисления значения логической функции элемента схемы в соответствии с текущими состояниями сигналов на его входах, Текущие состояния элементов схемы хранятся в блоке 1. Для этого в блоке 1 каждому -му элементу схемы отводится 1-я ячейка, содержащая поле текущего слова состояния 1-го элемента (ССЭ) и поле счетчика совместных событий -го элемента (К).Структура слова состояния элемента (ССЭ) приведена на фиг.б. ССЭ содержит поля "Код", "Входы", "Выход". В поле "Код" записан адрес входа в микропрограмму моделирования логической функции элемента. Каждому входу элемента соответствует свой бит в поле "Входы" ССЭ. В поле "Выход" хранится текущее двоичное значение выходного сигнала элемента,Блок 1 имеет 1-й, 2-й и 3-й информационные входы, 4-й и 5-й - соответственно, первый и второй адресные входы, б-й вход управления считыванием, 7-й и 8-й - соответственно, первый и второй входы управления записью, а также 1-й и 2-й выходы, По единичному - сигналу на седьмом управляющем входе блока 1 с его первого информационного входа выполняется запись в поле ССЭ, а с второго - запись в поле К, По единичному сигналу на восьмом входе с третьего входа в поле слова состояния 1-го элемента записывается слово состояния 1-го элемента.По единичному сигналу на шестом входе блока 12 из 1-й его ячейки происходит считывание содержимого поля состояния 1- го элемента на первый выход и содержимого поля счетчика совместных событий на Второй ВЫХОД,Регистр 2 и регистр 3 имеют первые информационные входы и вторые входы управления записью, Запись информации в эти регистры осуществляется по единичному сигналу на управляющем входе,Регистр 4 выполняет операции модификации отдельных разрядов ССЭ, поступающего на его первый информационный вход из блока 1, Инвертирование значения 1-го разряда поля "Входы" в регистр 4 производится по сигналу на 1-шине его второго адресного входа, управления словом состояния элемента.Блок памяти 5 - это стек, предназначенный для хранения слов состояний тех элементов, у которых в данный момент модельного времени произошло изменение состояния хотя бы одного из входов ССЭ. Блок 5 имеет 1-й, 2-й, 3-й информационные входы, 4-й вход управления записью и 5-й вход управления считыванием и 1-й, 2-й, 3-й и 4-й выходы, Каждая ячейка блока 5 содержит следующие поля; поле номера элемента, поле слова состояния элемента с модифицированными входами (ССЭ) и поле счетчика совместных событий К, Содержимое поля счетчика совместных событий показывает количество входов 1-го элемента, для которых в данный момент модельного времени произошло изменение состояний. Например, при первом обращении к 1-й5 10 15 20 25 3035 40 45 50 55 ячейке блока 1 в блок 5 будет записано ССЭ 1-го элемента с одним измененным битом в поле "Входы" ССЭ и счетчик совместных событий будет равен единице,При втором обращении к 1-й ячейке блока 1 в блоке 5 будет записано ССЭ уже с 2-я модифицированными битами и счетчик совместных событий будет равен двум. При третьем обращении к 1-й ячейке блока 1 в блок 5 будет записано ССЭ с тремя изменениями битами в поле "Входы" и счетчик совместных событий будет равен трем и т.д. Очевидно, что наиболее достоверная, полная информация о выходном состоянии 1-го элемента в данный момент модельного времени может быть получена при моделировании логической функции 1-го элемента, у которого ССЭ содержит все измененные на данный момент биты в полеВходы ССЭ.По единичному сигналу на четвертом входе в ячейку блока 5 в поле номера элемента с первого входа записывается номер 1-го элемента, с второго входа в поле слова состояние записывается ССЭ, с третьего входа в поле счетчика совместных событий записывается значение счетчика совместных событий,По единичному сигналу на входе 5 на первый вход блока считывается значение из поля номера элемента, на второй выход блока - значение поля счетчика совместных событий. Единичный сигнал на выходе 4 блока 5 означает,что хотя бы одна ячейка блока содержит информацию,Регистр 6 имеет 1-й, 2-й, З-й, 4-й информационные входы, 5-й вход сброса в ноль, б-й вход управления записью и 7-й вход управления считыванием,При единичном сигнале на б-м управляющем входе блока 6 в поле Выходы" слова состояния, хранящегося в регистре, записывается новое значение с его четвертого входа, Единичный сигнал на входе 7 разрешает выдачу на 1, 2 и 3 выходы кода логической функции 1-го элемента, номера элемента и значения счетчика совместных событий соответственно,. Блоки 7-10 служат для вычисления новых выходных состояний элементов, у которых в данный момент модельного времени произошло изменение входных сигналов. Каждому типу логической функции элемента в блоке 7 соответствует микропрограмма.Микропрограмма функции элемента представляется в виде ориентированного графа, в котором из каждой вершины выходят две дуги, Вершины графа взвешены булевыми переменными (с инверсией или без нее), соответствующими входам и выходуВесовыми переменными вершин графа могут быть не только входы моделируемого графом элемента, но и его выход (фиг,4,е, 5,г),На фиг,4-5 приведен случай, когда все 25 элементы моделируемой схемы имеют не более 15 входов (номера входных переменных от О до Е в шестнадцатиричной системе счисления) и один выход (номер выходной переменной Е). Одним графом можно пред ставить несколько булевых функций, используя различные точки входа в граф (фиг,4,а,б и в,ж, фиг,5,а),Для хранения микропрограмм в блоке 7 каждой вершины графа микропрограммы 35 отводится отдельная ячейка, которая содержит следующие поля: Е - код весовой пере 40 50 55 элемента. Значение весовой переменной 2 при заданной вершине графа однозначно определяет направление выхода из этой вершины, примем условно направо при Е = 1 и вниз 2 = О. Тогда каждому набору значений весовых переменных Е всегда соответствует в .графе один и только один путь, выходящий направо из графа или вниз.Можно любому графу сопоставить некоторую булевую функцию так, чтобы вершины графа были взвешены аргументами функции, а значение функции при зададанных аргументах определялось движением по графу из начальной вершины к тому или иному выходу графа и принимало значение единицы при выходе из графа направо (й), а значение нуля - при выходе вниз (О).Примеры графов микропрограмм для некоторых логических элементов, изображенных на фиг, 4, представлены на фиг.5. менной; В - признак инверсии весовой переменной; й, О - адреса перехода соответственно право и вниз.При В = 1 переменная Ъ инвертируется. Если значение Е с учетом значения В равно 1, то выбирается адрес Я и по нему производится обращение к следующей микрокоманде или в графической форме - переход направо к следующей вершине графа элемента.Если Ъ с учетом В равно О, то выбирается адрес О и по нему выполняется переход,что в графической форме означает переход вниз к очередной вершине. Если значение В или О равно нулю, то это означает окончание микропрограммы элементы (выход из графа), а булевой функции и соответственно сигналу на выходе логического элемента присваивается значение весовой переменной Ъ с учетом В.Структура загрузки 7 для элементов, изображенных на фиг.4, приведена в табл.1. Структура загрузки блока 1 для 5 10 15 20 фрагмента схемы на фиг.7 приведена в табл,2, при этом предполагается, что в данный момент состояние входов элементов схемы 3-0, 7-1, 8-0, 5-0, 4-1, 9-1 - логический "0", а входов 3-1, 7-0, 7-2, 7-3, 5-1, 4-0, 9-0 - логическая "1",Блок 7 имеет 1-й вход управления считыванием, 2-й информационный вход и 3-й вход управления записью. По единичному сигналу на третьем входе на вход 2 блока 7 поступает ССЭ, из которого блок 7 выделяет код логической функции, которая будет выполняться. По единичному сигналу на первом входе блока 7 выполняется очередная команда микропрограммы логической функции. На 1-й, 2-й, 3-й и 4-й выходы блока 7 поступают соответственно значения 2, й, О, В, Коммутатор 8 имеет 1-й и 3-й соответственно, первый и второй управляющие входы и 2-й информационный вход, Коммутатор 8 служит для выделения одного из разрядов полей "Входы" и "Выход", поступающих на его информационный вход 1, в соответствии с номером весовой переменной Е, поступающим на его третий управляющий вход. В зависимости от значения поля В на втором управляющем входе коммутатора 8 передается значение выделенного разряда либо в прямом коде (В = 0), либо с инверсией (В = 1), коммутатор 9 при единичном сигнале на управляющем входе 3 передает на выход значение поля В со своего первого информационного входа, при нулевом сигнале - значение поля О со своего второго информационного входаСумматор 10 по модулю два при поступлении нулевого кода на вход синхронизации 1 выполняет операцию сложения по модулю два "старого" значения логической функции, поступающего на второй информационный вход сумматора по модулю два, и нового значения логической функции, поступающего на третий информационный вход.Блок памяти 11 - это стек, предназначенный для хранения слов состояний элементов, для которых найдено новое значение логической функции. Ячейка блока 11 имеет поля: поле слова состояния элемента, для которого найдено значение состояния выхода (ССЭ) и поле номера элемента.Блок 11 имеет 1-й и 2-й информационные входы, 3-й вход управления записью и 4-й вход управления считыванием, выходы - 1-й, 2-й, З-й, 4-й, По единичному сигналу на третьем управляющем входе в блок 11 происходит запись ССЭ, поступающего с первого входа и номера элемента с второго входа,Одное)еменно с записью в )-ю ячейку блока 11 ССЭ элемента 1 в блоке 12 в 1-ю ячейку записывается адрес и значение К счетчика совместных событий 1-го элемента.По единичному сигналу на четвертом управляющем входе блока 11 на первый и второй выходы блока считываются соответственно ССЭ и номер элемента. С выхода 3 снимается текущее значение адреса стека 11,Единичный сигнал на выходе 4 означает, что в блоке есть хотя бы одна занятая ячейка,Блок памяти 12 позволяет установить соответствие между номером элемента 1, для которого сформировано новое значение выходного состояния, и адресом ) блока 11, по которому хранится ССЭ 1-го элемента. Это соответствие необходимо установить по следующей причине,В процессе моделирования возможна ситуация, когда для некоторого значения 1 сначала будет сформирована логическая функция для ССЭ со значением счетчика совместных событий, равным К 1, где К 11 и выходное состояние записано в блоке 11. а затем на вход памяти 7 поступит ССЭ с К 2 К 1,Для того, чтобы исключить моделирование логической функции элемента 1, для которого значение счетчика совместных событий в блоке 5 меньше, чем значение счетчика совместных событий для этого же элемента в блоке 21, служат первый и второй соответственно элементы сравнейия 17, 18 и элемент И 19, а в блоке 12 в поле К хранится значение К 1 последнего ССЭ элемента 1, для которого сформировано состояние выхода.Блок 12 имеет 1-й 2-й и 3-й и соответственно второй, первый, третий информационные входы 4-й, 5-й, 6-й соответственно,)второй, третий и первый адресный входы, 7-й вход управления считыванием, 8-й и 9-й соответственно второй и первый входы управления записью и выходы 1-й и 2-й.По единичному сигналу на 8-м входе с первого и второго входов блока 12 происходит запись соответственно значения 1 и значения К, По единичному сигналу на входе 9 с третьего входа записывается ноль.По единичному сигналу на входе 7 на первый выход считывается значение из поля ), на второй выход - значение поля К,Генсратор 13 управляет считыванием информации из блоков 5 и 12. Генератор 13 начинает выдавать импульсы при поступлении единичного сигнала на его 1-й и 2-й входы запуска. Импульсный нулевой сигнал на третьем входе останова генератора -135 10 15 20 25 30 35 40 45 50 55 запрещает работу генератора до моментаприхода на вход запуска 4 импульса, по которому работа генератора возобновляется,Генератор 14 синхронизирует работублоков 6 и 7, Запуск генератора происходитс приходом нулевого сигнала на 2-й управляющий вход, останавливается работа генератора нулевым сигналом на входе 1.Генератор 15 управляет считываниеминформации из блока 11 и записью ее в блок1, а также обнулением (очисткой) ячеек блока памяти 12. При единичном сигнале навходе 1 генератор остановлен. Выдача импульсов начинается при поступлении нулевого сигнала нэ первый и третий входыпуска блока 15, Работа генератора приостанавливается при возникновении нуля на еговтором управляющем входе,Счетчик 16 увеличивает на единицу содержимое поля К 1-го элемента, поступающее на его информационный вход,Остальные узлы блока - типовые элементы вычислительной техники соответствующего назначения. Рассмотрим работублока в составе устройства, приведенногона фиг. 2.Устройство для моделирования цифровых схем содержит блок вычисления логических функций 1, блок моделей 23, состоящийиз и моделей 36, первый 24 и второй 23блока памяти, регистр 25, датчик случайныхчисел 27, генератор импульсов 28, блок формирования топологии 30, состоящий из первого 32 и второго 33 блоков памяти,генератора импульсов 34, счетчика 35, причем в блоке моделей 23 первый, вторые,третьи и четвертые входы моделей объединены первый и второй управляющие входыи-й модели подключены к шине нулевогопотенциала, выходы выполнения воспроизведения задержки сигнала и высвобождения 1-й модели (1 - 2, п) назначенной )-уэлементу схемы соединены соответственнос первым и вторым управляющими входами(и) модели, в узле формирования топологии 31 выход первого блока памяти 32 подключен к информационному входу счетчика35, счетный вход которого соединен с выходом генератора импульсов 34, выход счетчика подключен к входу второго блока памяти33. выход номера элемента которого соединен с первым информационным входом коммутатора устройства 30 и входом номераэлемента блока вычисления логических функций 1, а выход номера входа элемента свходом номера входа элемента блока вычисления логической функции и вторым информационным входом коммутатора устройства30 выход выполнения элемента, назначенного первой модели блока моделей 23 сое 1800465 12четвертого выхода блока формирования то 30 35 40 50 55 динен с входом запуска генератора импульсов устройства 28, входом считывания первого блока памяти 32 блока формирования топологии 31 и входом запуска генератора импульсов 34 блока формирования топологии 31, информационные выходы моделей блока моделей 23 подключены к соответствующим адресным входам второго блока памяти устройства 25, выход которого соединен с входом регистра 26, выход которого подключен к адресному входу блока памяти 32 блока формирования топологии 31, выход последнего элемента второго блока памяти 33 блока формирования топологии 31 соединен с установочными входами моделей блока моделей 23, а выход генератора импульсов устройства 28 подключен к входу счетчика устройства 29 и счетным входам моделей блока моделей 23, выход первого блока памяти устройства 24 соединен с входом запуска датчика случайных чисел 27, выход которого подключен к входам задания времени воспроизведения задержки сигнала в модели блока моделей 23 синхросигнал с пологии 31 поступает на второй управляющий вход блока вычислений логических функций 1, первый выход коммутатора устройства 30 подключен к второму информационному входу блока модели 23 и управляющему входу второго блока памяти 25, а второй выход - к первому блоку памяти 24 и к информационному входу второго блока памяти 25,Блок 23 предназначен для имитации задержек срабатывания элементов цифровых устройств, В процессе моделирования каждому активному элементу цифрового узла, в котором в данный момент распространяется сигнал, назначается определенная модель 36, Каждаяиз моделей 36 может находиться в одном из трех состояний: свобода, занята моделированием, заблокирована (процесс имитации в модели закончен, но информация об этом еще не выдана на выход), Назначение некоторой модели 36 определенному элементу цифровой схемы производится в момент модельного времени, когда должна быть начата имитация задержки распространения сигнала в данном элементе (элемент переходит в активное состояние). При этом среди всех свободных моделей 36 выбирается модель с наибольшим номером. Тогда на соответствующем информационном входе блока 23 появляется единичный сигнал, а в выбранную модель 36 записывается поступающее значение т случайного временного интервала задержки срабатывания цифрового элемента. Модель 36 переходит в состояние "Занято". 5 10 15 20 Имитация задержек распространениясигнала в цифровых элементах состоит вуменьшении на единицу по каждому импульсу генератора 28 значений случайных временных интервалов во всехнаходящихся вданный момент в состоянии "Занято" моделях 36,Модель 36 переходит в состояние "Заблокирована" в момент, когда по очередному импульсу генератора 28 значение еевременного интервала 1 становится равнымнулю. Это означает, что закончено воспроизведение временного интервала задержкиэлемента, назначенного данной модели 36.Одновременно с переходом модели 36 в состояние "Заблокирована" вырабатываетсяединичный сигнал на выходе 1 блока 23,С состояния "Свободно" модель 36 переходит по сигналу на третьем управляющем входе блока 23 и ей может бытьназначен новый цифровой элемент, Устройство и работа каждой из моделей 36 блока23 и всего блока не отличаются от описанияв прототипе,В блоке 25 каждой модели 36 соответствует определенная ячейка, в которую в процессе моделирования записываются номераактивных элементов схемы, которым в текущий момент 1 м назначена данная модель 36.Блок 25 имеет информационный вход 1, накоторый поступает номер активного элемента, адресные входы 3, на которые поступаетномер свободной модели в блоке 23. Записьинформации в блок 25 осуществляется поединичному сигналу на входе 2. По нулевомусигналу на входе 2 из блока 25 происходитсчитывание информации. Регистр 25 хранити передает в узел 2 номер логического элемента, распространение сигнала в которомзавершено в текущий момент модельноговремени 1, Датчик 27 формирует случайныевремена задеожек срабатывания элементовсхемы, Значения вероятностей (Р;р, настраивающие датчик 27 на формированиеслучайного времени сь подчиняющегосяфункции распределения Р(т) задержки срабатывания элемента с номером , записываются в-ю страницу блока 24. Генератор 28вырабатывает импульсы с фиксированнымпериодом следования только при нулевомсигнале на входе.Счетчик 29, имеющий счетный вход, яв-.ляется таймером Модели и хранит текущеезначение модельного времени. Блок 31предназначен для моделирования связейцифровой схемы. Для этого в блоке 33 каждому элементу отведена определенная область ячеек, расположенныхпоследовательно в порядке возрастания адресов, Число ячеек в области соответствуетчислу входов, связанных с выходом данногоэлемента схемы. Каждая ячейка области 33 соответствуетодной связи элемента схемы и содержит номер элемента и номер входа элемента-приемника, с которым соединен выходэлемента-источника, а также признак г, значение которого равно единице только для последней связи и, следовательно, для последней ячейки области. Каждая 1-я ячейка блока 32 хранит начальный адрес области в 10 блоке 33, в которой находится информацияо связях выхода -го элемента схемы.Блок 31 работает при наличии единичного сигнала на входе 2, На вход 1 поступает 15номер элемента-источника, в соответствиис которым блок 31 последовательно выдаетна выходы 2 и 4 номера элементов-последователей и номера входов элементов-последователей соответственно, непосредственно 20связанных с выходом элемента-источника. Вмомент выдачи последнего элемента блок31 вырабатывает единичный сигнал на выходе 1, свидетельствующий о том, что отработана последняя связь из 25элемента-источника. На выход 3 поступаетуправляющий сигнал с выхода генератора34. Генератор 34 вырабатывает импульсы сфиксированной частотой при единичномсигнале на входе. Остальные узлы устройства - типовые элементы вычислительной техники соответствующего назначения,Рассмотрим работу устройства на примере моделирования фрагмента схемы, приведенной на фиг. 7. Фрагмент схемы 35содержит элемент ИЛИ 1, элементы И-НЕ 3и 8, Т-триггер 4, элементы И 6 и И 9 и элемент 2 И-ИЛИ 7, причем выход элемента 1подключен к нулевому входу третьего элемента, к первому входу 7 и к нулевому входу 40элемента 8, выход элемента 7 подсоединенк первому входу элемента 3, выход элемента8 подключен к нулевому входу элемента 5 инулевые входы элементов 4 и 9 соединены,Перед началом работы блоки 33 и 32 45загружаются информацией о связях элементов схемы, В блоке памяти 33 информация освязях элемента 1, содержащая номера элементов и входов 3-0, 7-1, 8-0, признаки гз,гц, гав, помещена с адреса 19, информация 50о связях элемента 7, содержащая номер элемента и входа 3-1 и признак гтрк, помещена садреса 22, аналогичная информация о связях элемента 8, содержащая номер элемента и входа 5-0 и признак гав, помещена с 55адреса 25,В блок 24 заносится значение вероятностей (Р(т функцией распределения задержек распространения сигналов для всехэлементов схемы. В блоке вычисления логической функции загружаются блоки 1 и 7. Для схемы, приведенной на фиг.7, загрузка блока 27 выполняется согласно данным табл,1, загрузка блока 11 - согласно табл,2, в которой содержатся начальные слова состояний элементов схемы.Стеки 5 и 11 и блок памяти 12 не содержит информации и, следовательно, содержимое их ячеек равно нулю.Рассмотрим работу устройства в стационарном режиме с момента, когда содержимое счетчика 29 равно 100, т,е. модельное время тм = 100. Пусть в этот момент п-я модель блока 23, соответствующая первому элементу схемы, имодель, соответствующая элементу 7, и имодель, соответствующая элементу 8 схемы, одновременно перешли в состояние "Заблокировано", т.е, в этих моделях закончено воспроизведение временного интервала задержки цифрового элемента, назначенного данной модели. Узел 23 вырабатывает единичный сигнал на выходе 1, по которому запрещается работа генератора 28, из и-й ячейки блока 25 считывается в регистр 26 номер первого элемента схемы (фиг,7), Пусть к этому моменту модельного времени блок 1 содержит ССЭ элементов, соответствующие логическому состоянию сигналов схемы, приведенной на фиг.7. Из регистра 26 номер элемента 1 поступает на адресный вход блока 32, из первой ячейки которого в счетчик 35 считывается адрес 19 начла блока связей первого элемента. Из 19-й ячейки блока памяти 33 на выходе узла 31 считываются признак г 1 з = О, номер элемента 3, номер входа О, Номер элемента 3, управляющий сигнал и номер входа 0 поступает на входы блока вычисления логический функций. Номер элемента 3 записывается в регистр 2, номер входа записывается в регистр 3, Начинается работа блока вычисления логических функций, Из третьей ячейкиблока 1 считывается в регистр 4 слово состояния третьего элемента, равное Зы, 11 о, 0002 ы, где 3 - значение поля "Код", 1 - значение поля "Выход", 0002 - значение поля "Входы" в шестнадцатиричной системы счисления, Регистр 3 и реобразует код номера 0 в унитарный код, содержащий 1 только в нулевом разряде, соответствующем нулевому входу третьего элемента. Регистр 4 инвертирует состояние нулевого разряда поля "Входы" ССЭ, которое принимает значение 000316 = 0000 0000 0000 0011, ССЭ с измененным битом в поле "Входы" (ССЭ) поступает на первый информационный вход блока 1, на второй информационной вход блока 1 поступает с выхода счетчика 16 увеличенное на единицу значение признака К = 1 и по единичному сигналу на входе 7 по адресу 3 в блок 1 записываются ССЭ и К, Одновременно с этим ССЭ поступает с выхода регистра 4 на третий вход блока 5, на второй вход того же блока поступает номер элемента 3 с четвертого входа блока 1 и на первый вход блока 5 - увеличенное на единицу значение содержимого поля К = 1, Таким образом фиксируется возникновение первого события. Так как на четвертом управляющем входе 5 единица, следовательно, номер элемента, ССЭ и признак записываются в блок 5.Одновременно с процессом записи в стек 5 в момент, когда в стек поступает первое ССЭ, на выходе 4 блока 5 вырабатывается единичный сигнал, означающий, что блок 5 содержит информацию. При возникновении единичного сигнала на выходе 4 блока 5 запускается генератор 13 Импульсы с выхода генератора 13 поступают на 5-й управляющий вход блока 5, разрешая считывание из него содержимого ячейки, состоящего из номера элемента 3, ССЭ и признака К = 1, и на 7-й управляющий вход блока 12, Блок 12 переключается в режим считывания. С первого выхода блока 5 номер элемента 3 поступает на вход 4 блока 12, из которого считывается содержимое ячейки по адресу 3, Так как запись в блок 12 не производилась, все его ячейки содержат нули, поэтому на выходе элемента 19 появляется нулевой сигнал, который приостанавливает генератор 13 и разрешает работу генератора 14. Генератор 14 выдает импульсы на управляющий вход 7 блока 6 и вход 3 блока 7. С этого момента в устройстве происходит два независимых процесса: процесс формирования ССЭ для элементов 7 и 8 в блоках 1, 2, 3, 4, 5, 16, 20 и процесс моделирования логической функции элемента 3 в блоках 7-10, Пока в блоках 7-10 идет процесс моделирования выходного состояния третьего элемента, из блока формирования топологии на входы блока вычисления логической функции будет последовательно переданы информация о связях 1-7, 1-8, аналогично предыдущему в блок памяти 5 запишутся модифицированные ССЭ для элементов 7 и 8. Таким образом, в блоке 5 будут находиться два модифицированных ССЗ. Первый процесс развивался далее следующим образом. Так как из блока 33 считаны все ячейки из области, соответствующей первому элементу, то на выходе 1 блока 31 появляется единичный сигнал, который поступает на вход 3 блока 23 и по сигналу с выхода модели пиз блока памяти 25 по адресу, соответствующему модели п, считывается номер элемента 7, который поступает в регистр 26. Из регистра 26 номер элемента 7 поступает на адресный вход блока 32, из 7-й ячейки которого в счетчик 35 считывается адрес 22, по которому в блоке 33 содержится ин формация о связях элемента 7. Из ячейки 22блока 33 на выходы узла 31 считывается п ризнак газ=1, номер элемента 3 и номер входа 1. Номер элемента 3, управляющий сигнал и номер входа 1 поступают на входы блока 10 вычисления логических функций. Номер элемента 3 записывается в регистр 2, номер входа - в регистр 3. Начинается работа блока вычисления логических функций. Из третьей ячейки блока 2 считывается в регистр 4 слово 15 состояния третьего элемента, равное Зы,1 ы, 0003 ы, Регистр 3 преобразует код номера входа 1 в унитарный код, содержащий 1 только в первом разряде, соответствующем первому входу третьего элемента, Регистр 420 инвертирует состояние первого разряда поля "Входы" ССЭ. ССЭ поступает на первый информационный вход блок 1, на 2-й информационный вход блока 1 поступает с выхода счетчика 16 увеличенное на единицу значе ние признака К = 1 + 1 = 2, фиксирующиевозникновение двух совместных событий, и по единичному сигналу на входе 7 по адресу 3 в блок 1 записывается ССЗ и К. Одновременно с этим в ячейку блока 5 записывается 30 номер элемента 3, ССЗ и признак К=2.Для элемента 8, поступающего из регистра 25 на адресный вход блока 32, аналогично рассматривается связь 8-5. Для элемента 5 формируется ССЗ и признак К=1 ианало гично заполняются ячейки в блоках 1 и 5.ССЭ третьего элемента поступает с первого выхода регистра 6 на информационный вход блока 7. Блок 7 выделяет из ССЭ код логической функции и считывает первую команду 40 микропрограммы логической функции Р 1,соответствующий 3-му элементу схемы и содержащую значение поля 2 = 1, й = О, О = 4,В =1. Так какЕ= 1, то коммутатор 8 выделяет из поступающих на его второй вход значе 45 ний полей "Выход" и "Входы" ССЭ, равных(1,0003) значение первого разряда, равное 1,а так как В = 1, то на выход коммутатора 8 значение первого разряда будет передано с инверсией. 50 Пусть на управляющий вход коммутатора 9 поступает нулевой сигнал, тогда на выход коммутатора поступает информация с 55 его второго информационного входа, т.е.значение поля О = 4 ССЗ . В соответствии с тем, что на третьем входе синхронизация сумматора 10 по модулю два присутствует код, отличный от нуля, сложение не выполняется. Значение О = 4 поступает на адресный вход блока 7, из которого считывается очередная команда микропрограммы логической функции Е 7, содержащая значение Е = О, Я = О, О = О, В = 1. В графической форме на фиг.5,а это означает переход по графу микропрограммы из вершины 3 в вершину 4,Так как Е = О, то коммутатор 8 выделяет в полях "Выход" и "Входы" ССЭ, равные (1,0003), значение нулевого разряда, равное 1, и так как В = 1, на выход коммутатора 8 значение нулевого разряда будет передано с инверсией, Тем самым на управляющий вход коммутатора 9 подается нулевой сигнал и на его выход поступает информация с второго информационного входа, т.е. значение поля О = 0 ССЭ, В графической форме это означает выход из вершины графа 4 микропрограммы вниз с присвоением логической функции значения О.Так как на вход синхронизации 1 сумматора 10 по модул ю два поступает нулевой код О = О, то сумматор 10 выполняет операцию сложения по модулю два, поступающего в регистр 6 старого состояния поля "Выход" ССЭ элемента 3, равного 1 и поступающего через коммутатора 8 нового состояния выхода элемента, равного О, На выходе сумматора 10 по модулю два вырабатывается единичный сигнал, означающий, что выход 3-го элемента изменил состояние (в данном случае перешел в нулевое состояние). При поступлении единичного сигнала с выхода блока 10 на вход 6 блока 6 в поле "Выход" ССЭф третьего элемента осуществляется-запись нового значения, равного О, которое поступает с выхода. коммутатора 8 и этот же сигнал пеоеключает в режим записи блоки 11 и 12, ССЭ с новым полем "Выход" с первого выхода блока 6 поступает на первый информационный вход блока 11, на второй информационный вход блока 11 поступает номер элемента= 3 с выхода 2 блока 6 и этот же номер элемента поступает на третий адресный вход 5 блока 12, Значение признака К = 1 с третьего выхода блока 6 передается на первый информационный вход 2 блока 12, на первый вход этого же блока поступает значение адреса ) (примем его для примера равным 20) свободной ячейки стека 11, в которую производится запись и его ССЭ с измененным выходом соответствующего номера элемента, В блок 12 по адресу= 3 записывается информация, содержащая значение адреса ) = 20, по котором в блоке 11 находится ССЭ третьего элемента с изменением выходом и признак К = 1. Тем самым завершается обработка одного ССЭ. Нулевой сигнал с выхода блока 9 завершает работу блока 7, приостанавливает генератор 14 и разрешает работу генератора 13. По импульсу генератора 13 на вход 5 блока 5 из,стека считывается номер элемента=7, ССЭэлемента 7 и признак К = 1, Блок 12 находи г 5 ся в режиме считывания. Из седьмой ячейкиблока 12 считывается информация, т.е, ) и =О, Кт = О, то на выходе элемента 19 появляется нулевой сигнал, который запустит генератор 13, Аналогично предыдущему случаю10 блок 7 выделяет код логической функцииэлемента 7 и считывает первую командумикропрограммы логической функции Р,соответствующей 7-му элементу схемы, Команда содержит 2 = О, й = 6, О = 7, В =, О. Так15 как 7 = О, то коммутатор 8 выдает значениенулевого разряда поля "Входы" ССЭ, и таккак В = О, то инвертирование не вьполняется и на выход коммутатора 8 поступает единичный сигнал. Так как на управляющий20 вход коммутатора 9 поступает единичныйсигнал, то на его выход передается информация из поля В команды. Единичный сигнал поступает на первый вход блока 7, изкоторого считывается следующая команда25 микропрограммы функции 4. Команда содержите=1, й =7, 0 =0, В =1. В графической форме на фиг,5,б это означает переходпо графу микропрограммы из вершины 5 ввершину 6. По 2 = 1 и В = 1 коммутатор 830 передает на выход значение первого разряда поля "Входы" ССЭ из регистра.6 с инверсией, Тем самым на выходе коммутатора 8возникает нулевой сигнал, коммутатора 9передает на выход значение поля О = О, В35 графической форме это означает выход извершины 5 графа вниз с присвоением логической функции Р 4 значения О. Сумматор 10по модулю два выполняет операцию сложения, Единичный результат сложения означа 40 ет, что 7-й элемент изменил состояние,Далее производится операции, аналогичные тем, которые были описаны для 3-гоэлемента, в результате которых в стеке 11 поадресу ) = 21 будут записаны ССЭ 7-го эле 45 мента с измененным выходом, равным в нашем случае нулю и номер= 7. В блоке 12ячейки с адресом= 7 будет содержать )т21 и К=1,Для элемента 8 аналогичным образом в50 стек 11 по адресу) = 22 запишется ССЭ 8-гоэлемента с измененным выходом, в нашемслучае с выходом, равным единице. а в блоке 12 по адресу= 8 запишется )в = 22, К =. 1,По очередному импульсу генератора 13 из55 блока 5 считывается ССЭ, соответствующее3-му элементу,= 3 и К = 2, Из блока 12 поадресу= 3 считывается содержимое ячейки, состоящее из )з = 20 и К = 1. Так как 13отлично от нуля, то на выходе схемы 17 появляется единица, Это означает, что для

СмотретьЗаявка

4878492, 26.10.1990

МИНСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ

НОВИКОВ ВЛАДИМИР ИВАНОВИЧ, МЕЛЬНИКОВ ВЯЧЕСЛАВ КОНДРАТЬЕВИЧ, ЗАРЕМБОВСКАЯ ИРИНА АРТУРОВНА, ФАДЕЕВА ЕЛЕНА ПАВЛОВНА

МПК / Метки

МПК: G06F 15/419

Метки: блок, вычисления, логических, функций

Опубликовано: 07.03.1993

Код ссылки

<a href="https://patents.su/17-1800465-blok-vychisleniya-logicheskikh-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Блок вычисления логических функций</a>

Предыдущий патент: Устройство для обучения операторов

Следующий патент: Устройство для определения площади контурных изображений

Случайный патент: Устройство для закрепления приспособлений-спутников