Формирователь импульсов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1226527

Авторы: Косоусов, Максимов, Петричкович, Филатов

Текст

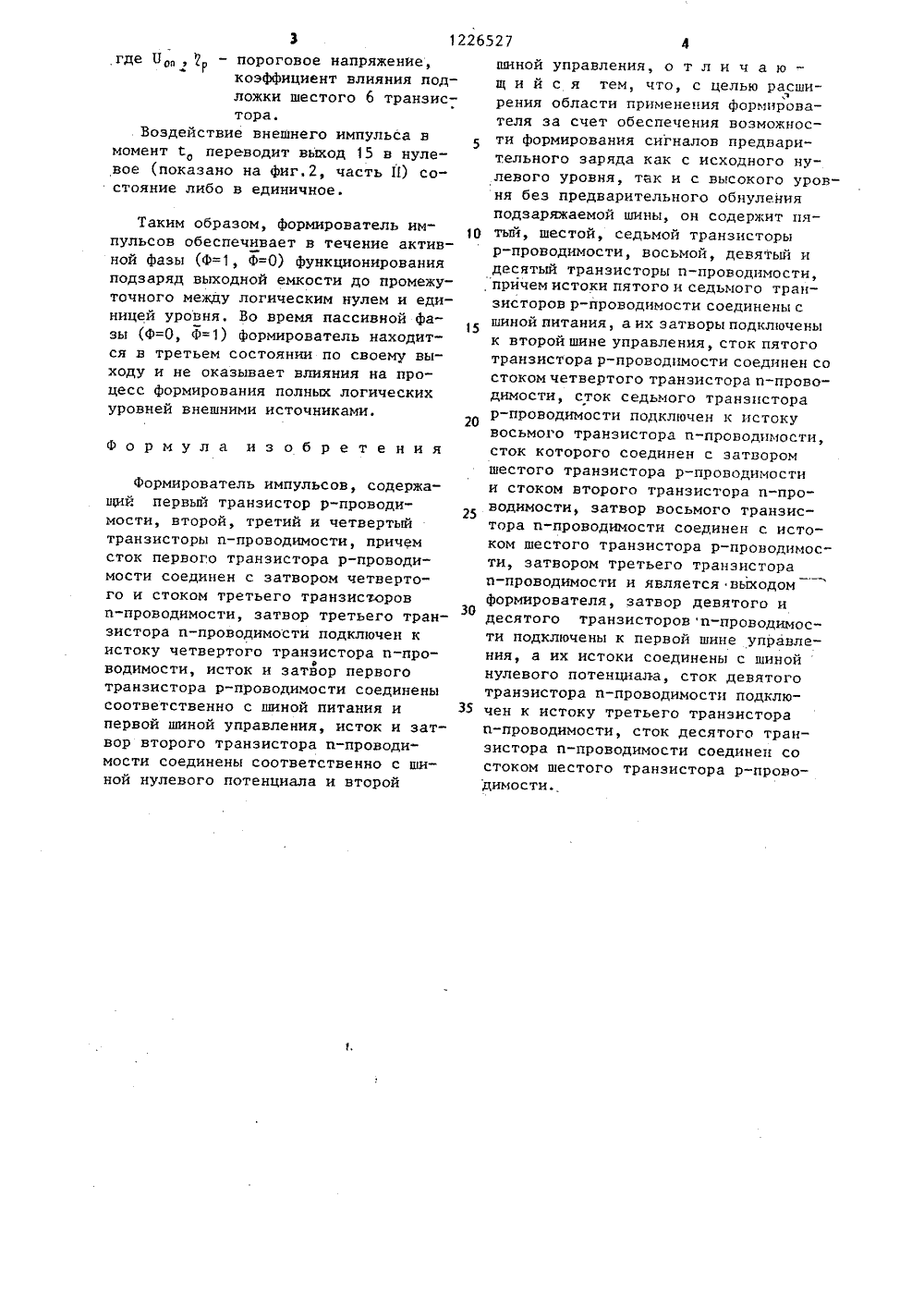

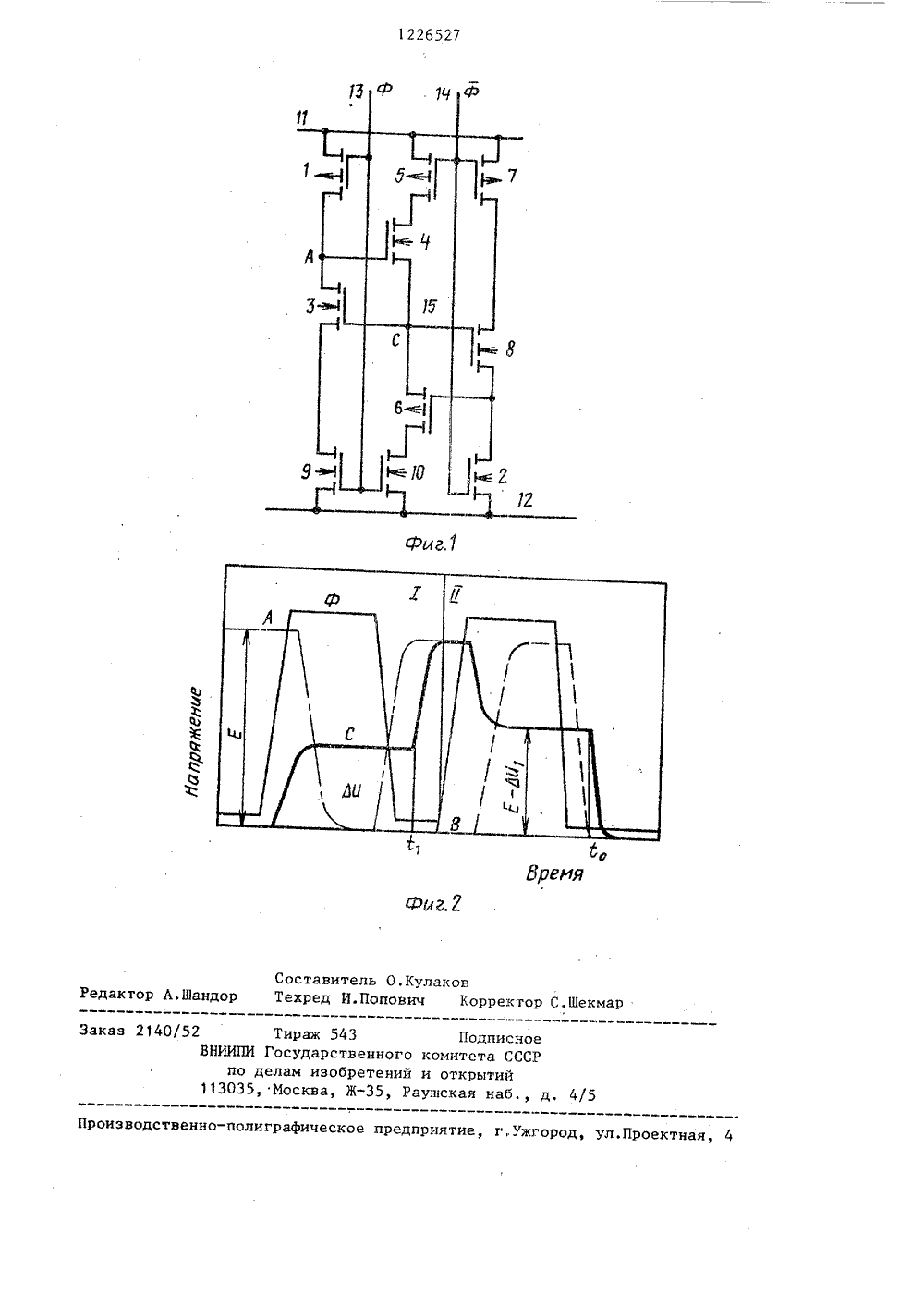

. ГОСУДАРСТВЕННЫЙ НОМИТЕТ ССС ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫ ПИСАНИЕ ИЗ ОРСНОМУ СВИДЕТЕЛЬСТВ(57) Изобретение относится к областивычислительной техники и электроникии может быть использовано при построении устройств для считывания инфоркапителей запоминающих у р тв в качестве элемента, осуществляющего предварительный подзаряд шин данных, Целью изобретенияявляется расширение области применения устройства за счет обеспечениявозможности формирования сигналовпредварительного заряда как с исходного нулевого, уровня, так и с высокого уровня без предварительногообнуления подзаряжаемой шины. ормирователь работает в двух режимах:режим восстановления (подготовки) ирежим формирования уровня подзаряда,2 ил.Изобретение относится к вычислительной технике и электронике и может быть использовано при построенииустройств для считывания информациииз накопителей запоминающих устройствв качестве элемента, осуществляющегопредварительный подзаряд шин данных.Целью изобретения является расширение области применения за счет обеспечения возможности Формирования сигналов предварительного заряда как сисходного нулевого уровня, так и свысокого уровня без предварительногообнуления подзаряжаемой шины.На фиг. 1 приведена схема Формирова теля импульсов; на фиг.2 - кривые переходных процессов,Формирователь импульсов содержитпервый 1 транзистор р-проводимости,второй 2, третий 3, четвертый 4 транзисторы п-проводимости, пятый 5, шестой 6, седьмой 7 транзисторы р-проводимости, восьмой 8, девятый 9, десятый 10 транзисторы п-проводимости,шину 11 питания, шину 12 нулевого потенциала, первую 13 и вторую 14 шиныуправления, выход 15.Формирователь импульсов работает вдвух режимах: режим восстановления(подготовки) и режим Формированияуровня подзаряда.В режиме восстановления (подготовки) на прямом и инверсном управляющих входах 14 установлен код, соответственно, Ф=О, Ф=1. При этом открытые первый 1 и второй 2 транзисто- Зры обеспечивают Формирование в узлахЙ и Ь уровней, соответственно, Е и О,Закрытые пятый 5 и десятый 10 транзисторы отключают выход 15 от шины,11 питания и общей шины 12, обеспечивая тем самым пассивное (третье) состояние выхода 15.Смена управляющего кода 01 на противоположный 10 на входах 13 и 14переводит схему в режим формированияподэаряда. В зависимости от состояниявыхода 15 возможны два варианта переходного процесса: формирование подзаряда из нулевого состояния на выходе15 - область 1 на фиг.2 и формирование подэаряда из единичного состоя.ния на выходе 15 - область й на Фиг.2. В первом варианте переходного процесса открывающийся седьмой и откры тый восьмой 8 транзисторы обеспечивают формирование в узле 8 логической единицы, закрывающей шестой транзистор 6. Открывающийся пятый 5 и открытый четвертый 4 транзисторы инициируют процесс повышения напряжения на выходе 15 схемы до уровня, определяемого соотношением60 =Е1 ор )(1 п) фгде Е - напряжение на шине 11 питания относительно общей шины12;Б, , - пороговое напряжение, коэффициент влияния подложкичетвертого транзистора.В случае если ЛБЦ, открываюО )щийся третий 3 и открытый девятый 9 транзисторы обеспечивают формирование логического нуля в узле А, закрывающего четвертый транзистор 4. В случае, если ЬБУ , что имеет место при выполнении условияЕ 1 п 2 ф оо четвертый транзистор 4 закрываетсяпо подложке и потенциал узла Й неизменяется.Таким образом, в результате воздействия управляющих сигналов Ф=1, Ф=О на выходе 15 сформирован импульсо подзаряда, амплитуда которого Ь Ц находится в пределах 0 с ьПЕ, причем в схеме отсутствуют сквозные токи, а выход 15 отключен от шин 11 питания и общей шины 12 закрытыми четвертым 4 и шестым 6 транзисторами. Последуюшее изменение состояния управляющих .входов 13 и 14 на противоположное, соответственно Ф=О и Ф=1 обеспечивает сохранение уровня напряожения йБ на выходе 15 эа счет сохранения его отключенного состояния посредством запирания десятого 10 и пятого 5 транзисторов. Воздействие в момент й, внешнего импульса переводит выход 15 в состояние логической единицы (на Фиг.2, часть 1) либо в состояние логического нуля.Исходя из симметричности схемы,характер переходного процесса приФормировании уровня подзаряда иэединичного состояния (фиг.2, часть П)аналогичен рассмотренному, при этомуровень на выходе 15 определяетсявыражениемгде ц ,- пороговое напряжение,коэффициент влияния подложки шестого 6 транзистора.Воздействие внешнего импульса в момент С переводит выход 15 в нулевое (показано на фиг,2, часть П) состояние либо в единичное.Таким образом, формирователь импульсов обеспечивает в течение активной фазы (Ф=1, Ф=О) функционирования подзаряд выходной емкости до промежуточного между логическим нулем и единицей уровня, Во время пассивной фазы (Ф=О, Ф=1) формирователь находится в третьем состоянии по своему выходу и не оказывает влияния на процесс формирования полных логических уровней внешними источниками.Формула изобретенияФормирователь импульсов, содержащий первый транзистор р-проводимости, второй, третий и четвертый транзисторы п-проводимости, причем сток первого транзистора р-проводимости соединен с затвором четвертого и стоком третьего транзисторов п-проводимости, затвор третьего транзистора и-проводимости подключен к истоку четвертого транзистора п-проФводимости, исток и затвор первого транзистора р-проводимости соединены соответственно с шиной питания и первой шиной управления, исток и затвор второго транзистора и-проводимости соединены соответственно с шиной нулевого потенциала и второй шиной управления, о т л и ч а ю -щ и й с я тем, что, с целью расширения области применения формирователя за счет обеспечения воэможности формирования сигналов предварительного заряда как с исходного нулевого уровня, так и с высокого уровня без предварительного обнуленияподзаряжаемой шины, он содержит пя О тьпу, шестой, седьмой транзисторыр-проводимости, восьмой, девятый идесятый транзисторы п-проводимости,причем истоки пятого и седьмого транзисторов р-проводимости соединены сшиной питания, а их затворы подключенык второй шине управления, сток пятоготранзистора р-проводимости соединен состоком четвертого транзистора п-проводимости, сток седьмого транзисторар-проводимости подключен к истокувосьмого транзистора п-проводимости,сток которого соединен с затворомшестого транзистора р-проводимостии стоком второго транзистора и-проводимости, затвор восьмого транзистора и"проводимости соединен с истоком шестого транзистора р-проводимости, затвором третьего транзисторап-проводимости и является выходомформирователя, затвор девятого и ЗОдесятого транзисторов и-проводимости подключены к первой шине управления, а их истоки соединены с шинойнулевого потенциала, сток девятоготранзистора и-проводимости подклюЗ 5 чен к истоку третьего транзисторап-проводимости, сток десятого транзистора и-проводимости соединен состоком шестого транзистора р-проводимости.

СмотретьЗаявка

3794655, 28.09.1984

ОРГАНИЗАЦИЯ ПЯ В-8466

КОСОУСОВ СЕРГЕЙ НИКОЛАЕВИЧ, МАКСИМОВ ВЛАДИМИР АЛЕКСЕЕВИЧ, ПЕТРИЧКОВИЧ ЯРОСЛАВ ЯРОСЛАВОВИЧ, ФИЛАТОВ ВАЛЕРИЙ НИКОЛАЕВИЧ

МПК / Метки

Метки: импульсов, формирователь

Опубликовано: 23.04.1986

Код ссылки

<a href="https://patents.su/4-1226527-formirovatel-impulsov.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь импульсов</a>

Предыдущий патент: Формирователь сигналов

Следующий патент: Буферное запоминающее устройство

Случайный патент: 402762