Устройство для коррекции ошибок в информации, представленной в системе остаточных классов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1206962

Авторы: Брезгунов, Долгов, Краснобаев

Текст

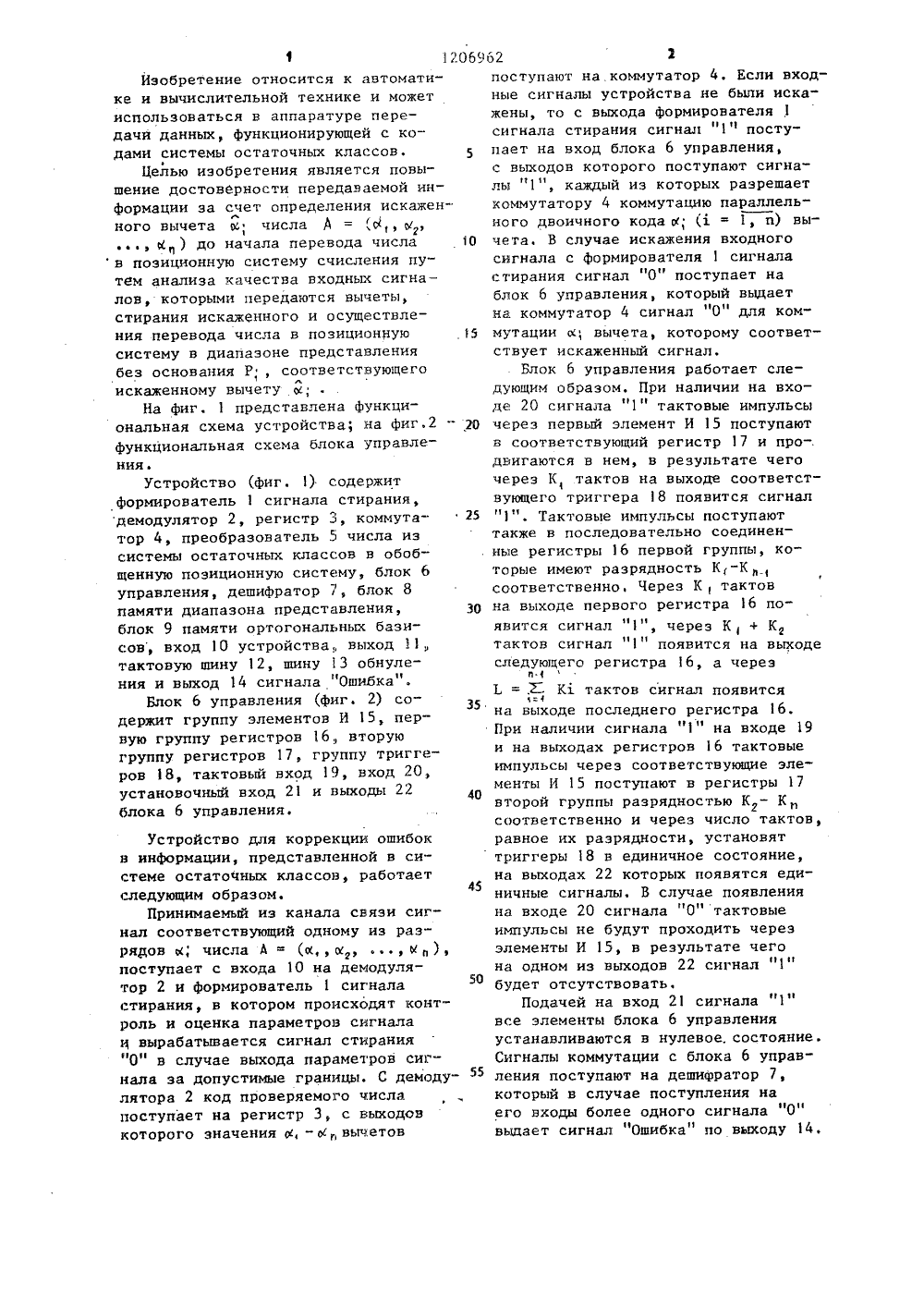

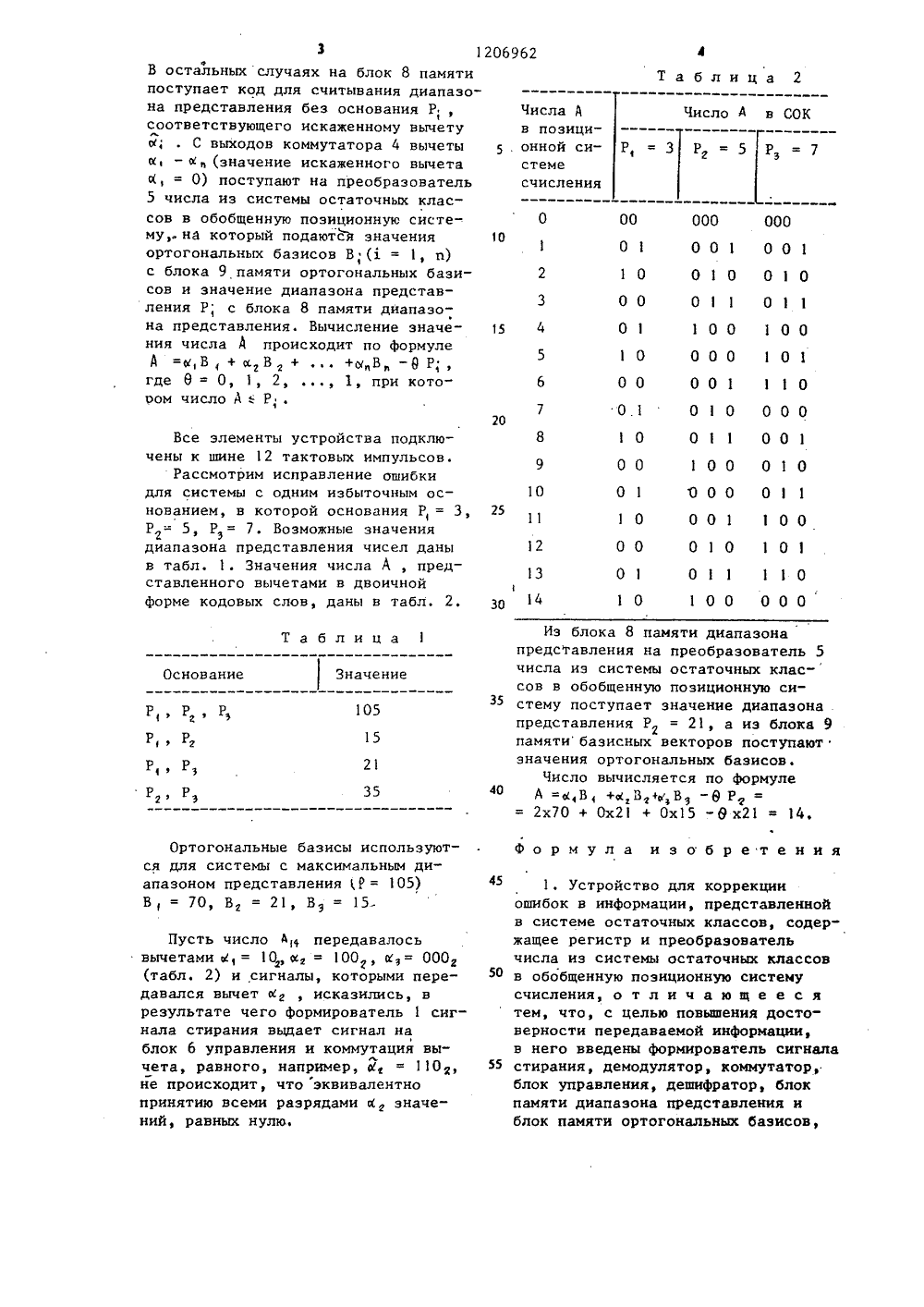

.01.79. ОШИ- ОЙ втое и уре иг ГОСУДАРСТВЕННЫЙ КОМИТЕТ ССПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТН 3783290/24-2405.06.8423.01.86, Бюл, )Р 3В.И. Долгов, А.В. БреэгунКраснобаев81.326.77(088.8)(56) Акушский И.Я., Юдицкий Д. Машинная арифметика в остаточн классах. М.: Советское радио, с. 351-356.Авторское свидетельство ССС У 798846, кл. С 06 Р 11/08, 04 (54) УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ БОК В ИНФОРМАЦИИ, ПРЕДСТАВЛЕНН В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ (57) Изобретение относится к а матике и вычислительной техник может использоваться в аппарат передачи данных, функционирующейс кодами системы остаточных классов .Цель изобретения - повышение достоверности передаваемой информации.Устройство содержит формирователь 1сигнала стирания, демодулятор 2,регистр 3, коммутатор 4, преобразователь 5 числа из системы остаточных классов в обобщенную позиционную систему, блок 6 управления, состоящий из группы элементов 15 И,двух групп регистров 16 и 17 и группы триггеров 18, а также дешифратор 7, блок 8 памяти диапазона представления, блок 9 памятиортогональ-ных базисов, вход 1 О, выход 11, тактовую шину 12, шину 13 обнуленияи выход 14 сигнала "Ошибка". 1 з.п.ф-лы, 2 ил.Изобретение относится к автоматике и вычислительной технике и может использоваться в аппаратуре передачй данных, функционирующей с кодами системы остаточных классов.ФЦелью изобретения является повышение достовЕрности передаваемой информации эа счет определения искаженлного вычета м числа 4 = ,М м1, К ) до начала перевода числа в позиционную систему счисления путем анализа качества входных сигналов, которыми передаются вычеты,стирания искажЕнного и осуществления перевода числа в позиционнуюсистему в диапазоне представлениябез основания Р , соответствующеголискаженному вычету м,На фиг. 1 представлена функциональная схема устройства; на фиг,2функциональная схема блока управления.Устройство (фиг. 1) содержитформирователь 1 сигнала стирания,демодулятор 2, регистр 3, коммутатор 4, преобразователь 5 числа изсистемы остаточных классов в обобщенную позиционную систему, блок 6управления, дешифратор 7, блок 8памяти диапазона представления,блок 9 памяти ортогональных базисов, вход 10 устройства выход 11тактовую шину 12, шину 13 обнуления и выход 14 сигнала "Ошибка".Блок 6 управления (фиг. 2) содержит группу элементов И 15, пер.вую группу регистров 16 вторуюгруппу регистров 17, группу триггеров 18, тактовый вход 19, вход 20,установочный вход 21 и выходы 22блока 6 управления. Устройство для коррекции ошибок н информации, представленной в системе остаточных классов, работает следующим образом.Принимаемый иэ канала связи сигнал соответствующий одному из разрядов м, числа А = (к ми)поступает с входа 10 на демодулятор 2 и формирователь 1 сигнала стирания, в котором происходят контроль и оценка параметров синала ц вырабатывается сигнал стирания "0" в случае выхода параметров сигнала за допустимые границы. С демодулятора 2 код проверяемого числа поступает на регистр 3, с выходов которого значения , - м вычетов 5 1 О 15 20 25 ЗО 35 40 45 поступают на коммутатор 4. Если входные сигналы устройства не были искажены, то с выхода формирователя 1 сигнала стирания сигнал "1 ч поступает на вход блока 6 управления, с выходов которого поступают сигналы "1", каждый из которых разрешает коммутатору 4 коммутацию параллельного двоичного кода Ф; (д = 1, и) вычета. В случае искажения входного сигнала с формирователя 1 сигнала стирания сигнал "0" поступает на блок 6 управления, который выдает на коммутатор 4 сигнал "0" для коммутации к; вычета, которому соответствует искаженный сигнал.Блок 6 управления работает следующим образом. При наличии на входе 20 сигнала "1" тактовые импульсы через первый элемент И 15 поступают в соответствующий регистр 17 и продвигаются в нем, в результате чего через К, тактов на выходе соответствующего триггера 18 появится сигналТактовые импульсы поступают также в последовательно соединенные регистры 16 первой группы, которые имеют разрядность К,-К ,1 соответственно, Через Ктактов на. выходе первого регистра 16 появится сигнал "1", через К+ К тактов сигнал "1" появится на выходе следующего регистра 16, а через Е = .Х- К тактов сигнал появится на выходе последнего регистра 16. При наличии сигнала "1" на входе 19 и на выходах регистров 16 тактовые импульсы через соответствующие элементы И 15 поступают в регистры 17 второй группы разрядностью К- К соответственно и через число тактов, равное их разрядности, установят триггеры 18 в единичное состояние, на выходах 22 которых появятся единичные сигналы, В случае появления на входе 20 сигнала "0" тактовые импульсы не будут проходить через элементы И 15, в результате чего на одном из выходов 22 сигнал "1" будет отсутствовать, Подачей на вход 21 сигнала "1" все элементы блока 6 управления устанавливаются в нулевое. состояние.Сигналы коммутации с блока 6 управления поступают на дешиФраторкоторый в случае поступления на его входы более одного сигнала "0"выдает сигнал "Ошибка" по выходу 14,1206962 Таблица 2 Числа А Число А в СОК в позици 5 . Оннои си стеме Р, = 3 Р = 5 э счисления 01 О 00 000 000 0 1 001 001 010 010 011 011 100 100 000 101 001 110 1 0 0 0 15 4 0 1 1 0 0 0 7208 1 0 011 001 100 010 000 011 001 100 010 10 011 110 0 О 1025 0 1 1 0 12 0 0 13 1 зо 40Таблица 1 Основание 105 Р Р, Р Р Р Р, Р Ргф Рэ 15 21 3В остальных случаях на блок 8 памяти поступает код для считывания диапазона представления без основания Р соответствующего искаженному вычету Ф, . С выходов коммутатора 4 вычеты ф " к (значение искаженного вычета К, = 0) поступают на преобразователь 5 числа из системы остаточных классов в обобщенную позиционную систему,.на который подаютсю значения ортогональных базисов В;(. = 1, п) с блока 9 памяти ортогональных базисов и значение диапазона представления Р; с блока 8 памяти диапазона представления. Вычисление значения числа Д происходит по формуле Д =М,В, + сгВг++ОВл -9 Р; ь где 6 = О, 1, 2, , 1, при кото" ром число Д: Р Все элементы устройства подключены к шине 12 тактовых импульсов.Рассмотрим исправление ошибки для системы с одним избыточным основанием, в которой основания Р, = 3, Рг, Рэ = 7. Возможные значения диапазона представления чисел даны в табл. 1. Значения числа А , представленного вычетами в двоичной форме кодовых слов, даны в табл. 2. Ортогональные базисы используются для системы с максимальным диапазоном представления (Г = 105) В, = 70, В = 21, Вэ = 15 Пусть число Д 1 передавалось вычетами Ы, = 10, к, = 100 , кэ= 000 г (табл. 2) и сигналы, которыми передавался вычет Кг , исказились, в результате чего формирователь 1 сигнала стирания выдает сигнал на блок 6 управления и коммутация выфЪчета, равного, например, Ф = 110, не происходит, что эквивалентно принятию всеми разрядами Кг значений, равных нулю. 01О 0 000 10 100 000 Из блока 8 памяти диапазона представления на преобразователь 5 числа из системы остаточных классов в обобщенную позиционную систему поступает значение диапазона представления Р = 21, а иэ блока 9 памяти базисных векторов поступают значения ортогональных базисов.Число вычисляется по формулеА =ы,В, +к,В ь,В -6 Р2 х 70 + Ох 21 + Ох 15 - 9 х 21 = 14,Формула изобретения 1. Устройство для коррекцииошибок в информации, представленной в системе остаточных классов, содержащее регистр и преобразователь числа из системы остаточных классов в обобщенную позиционную систему счисления, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности передаваемой информации, в него введены формирователь сигнала 55 стирания, демодулятор, коммутатор,блок управления, дешифратор, блок памяти диапазона представления и блок памяти ортогональных базисов,5 Составитель Л. ЗахТехред АБабинец . едактор Л. Гратилл ректор Г, Решетник аз 8734/59ВНИИПИ ПодписСССР Тираж Государственн лам изобретен осква, Ж"35,го комитетаий и открытийаушская наб 113035Д е Патент", г. Ужгород, ул. Проектная 3 12069 вход демодулятора объединен с входом формирователя сигнала стирания и является входом устройства, а выход демодулятора подключен к входу регистра, выходы которого подключены к информационным входам коммутатора управляющие входы которого объединены с соответствующими входами дешифратора и подключены к соответствующим выходам блока управления, вход 1 О которого соединен с выхоцом формирователя сигнала стирания, первый выход дешифратора является выходом сигнала Ошибка", а остальные через блок памяти диапазона представления соединены с первым входом преобразователя числа из системы остаточных классов в обобщенную позиционную систему счисления, вторые и третьи входы которого соединены соответственно с выходами коммутатора и блока памяти ортогональных базисов, а выходявляется выходом устройства, тактовые входы всех блоков устройства дсоединены с тактовой шиной, а установочные входы блока управления и 62 Ьрегистра подключены к шиве обнуления.2. Устройство по и. 1, о т л ич а ю щ е е с я тем, что блок управления содержит первую и вторую группы регистров, группу элементов И и группу триггеров, первый вход первого элемента И и вход первого/регистра первой группы объединены и соединены с тактовым входом блока управления, выход каждого регистра первой группы соединен с входом последующего регистра этой группы, кроме последнего, и с первым входом соответствующего элемента И, вторые входы элементов И объединены и подключены к входу блока управления, а выходы - соединены с входами соответствующих регистров второй группы, выходы которых подключены к входам соответствующих триггеров, выходы которых соединены с соответствующими выходами блока управления, установочные входы триггеров и регистров первой и второй групп объединены и подключены к установочному входу блока управления.

СмотретьЗаявка

3783290, 05.06.1984

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ РАКЕТНЫХ ВОЙСК ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ДОЛГОВ ВИКТОР ИВАНОВИЧ, БРЕЗГУНОВ АЛЕКСАНДР ВЛАДИМИРОВИЧ, КРАСНОБАЕВ ВИКТОР АНАТОЛЬЕВИЧ

МПК / Метки

МПК: H03M 7/18

Метки: информации, классов, коррекции, остаточных, ошибок, представленной, системе

Опубликовано: 23.01.1986

Код ссылки

<a href="https://patents.su/4-1206962-ustrojjstvo-dlya-korrekcii-oshibok-v-informacii-predstavlennojj-v-sisteme-ostatochnykh-klassov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для коррекции ошибок в информации, представленной в системе остаточных классов</a>

Предыдущий патент: Преобразователь кода числа из системы остаточных классов в позиционный код

Следующий патент: Устройство цифрового преобразования сигналов импульсно кодовой модуляцией в сигналы с дельта-сигма модуляцией

Случайный патент: Способ контроля процесса возведения вертикальных монолитных железобетонных конструкций в скользящей опалубке