Устройство для вычисления разности двух чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1141401

Авторы: Бочкарева, Крочакевич, Саухатас

Текст

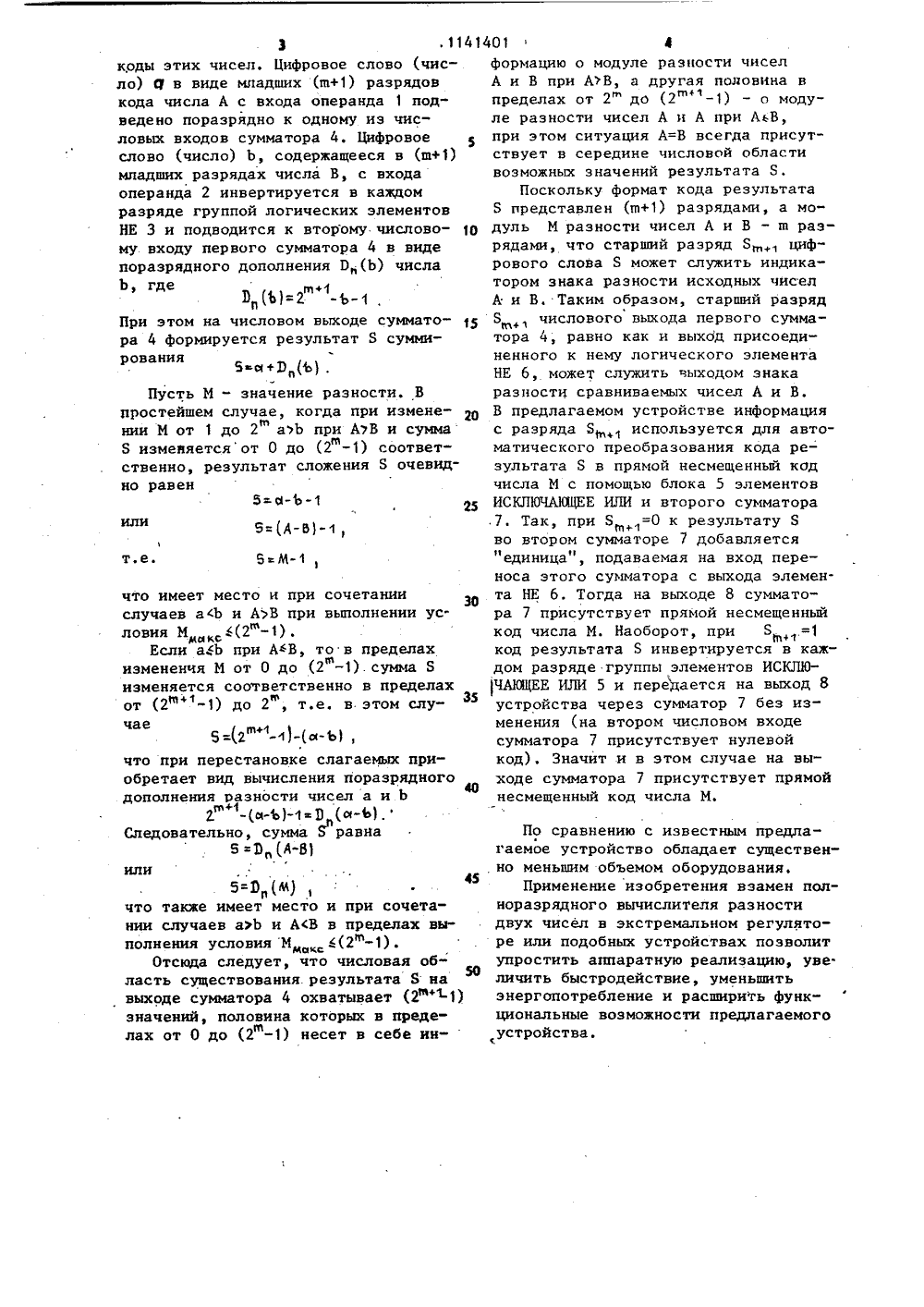

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН 4(511 С 06 Р 7/5 ОПИСАНИЕ ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ хатас ас- тиГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(71) Рижский ордена Трудовогоного Знамени политехнический и тут53) 681.325,5(088.8)56) 1. Симофанов К.Г., Корнейчук В.И арасенко В.П. Цифровые электронные вычислительные машины, Киев. "Высшая школа", 1976, с. 290, рис. 267.2. Титце У Шенк К. Полупроводниковая схемотехника. И., "Иир", 983, с. 335-336 (прототип).(54)(57) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ РАЗНОСТИ ДВУХ ЧИСЕЛ, содержащее первый и второй сумматоры, группу элементов НЕ, группу элемент ов ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент НЕ,причем первая группа входов первого сумматора соединена с входами разрядов первого операнда устройства, вторая группа входов первого сумматора соединена с выходами соответствующих элементов НЕ группы, входы которых подключены к соответствующим входам разрядов второго операнда устройства, выходы разрядов первого сумматора, кроме старшего разряда, соединены с первыми входами соответствующих элементов ИСКЛЮЧАКЦЕЕ ИЛИ группы, выходы которых соединены с первой группой входов второго сумматора, вторая группа входов которого соединена с нулевой шиной устройства, а вход переноса - с выходом элемента НЕ и с выходом знака разности устройства, выходы разрядов второго сумматора соединены с выходами разрядов разности устройства, о т л и - ч а ю щ е е с я тем, что, с целью упрощения конструкциипри определении малых разностей чисел, первый сумматор выполнен (в+1)-разрядным, где в - разрядность максимального ожидаемого значения разности, в в, где и - разрядность вычитаемых чисел, а второй сумматор - 1 п -разряд ным, причем выход суммы старшего разряда первого сумматора подключен к входу элемента НЕ и к вторым входам элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы.Изобретение относится к вычислительной технике и может быть использовано при построении специализированных вычислительных устройств, например, для численного дифференциро вания.Известно устройство для вычисления разности двух чисел, содержащее регистры первого и второго операндов,сумматор, регистр результата и блок 10управления, выход переноса старшегоразряда сумматора соединен с ВхОдомпереноса младшего разряда сумматора 11.Недостатком устройства является 15сложность конструкции, обусловленнаятем, что при вычислении малой разности больших чисел используемые сумматоры и другие цепи должны быть полноразрядными, т,е. их разрядность 20.должна быть равной разрядности большего из сравниваемых чисел.Наиболее близким техническим решением к изобретению является устройство для вычисления разности двух чисел, содержащее первый и второй сумматоры, группу элементов НЕ, группуэлементов ИСКЛЮЧАКЩЕЕ ИЛИ и элементНЕ, причем первые входы первого сумматора соединены с входами разрядов 30первого операнда устройства, вторыевходы первого сумматора - с выходамисоответствующих элементов НЕ группы,входы которых подключены к соответстВующим Входам РазрядОВ Второго 35операнда устройства, выходы разрядовпервого сумматора, кроме старшегоразряда, соединены с первыми входами соответствующих элементов ИСКЛЮЧАКЩЕЕ ИЛЧ группы, выходами соединенных с первыми входами второго сумматора, вторые входы которого соединены с нулевой шиной устройства, а входпереноса - с выходом элемента НЕ ис выходом знака разности устройства, 45выходы разрядов второго сумматорасоединены с выходами разрядов разности устройства, выход суммы старшегоразряда первого сумматора - с первымвходом соответствующего элементаИСКЛЮЧАЮЩЕЕ ИЛИ группы, вторые входыэлементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы -с выходом элемента НЕ, вход которогоподключен к выходу переноса старшегоразряда сумматора 2.Недостатком известного устройства,является сложность конструкции,обусловленная тем, что при определении малых разностей чисел разрядность сумматоров и других цепей долж 1на быть равной разрядности входныхоперандов.Целью изобретения является упрощение конструкции устройства для вычисления разности двух чисел приопределении малых разностей чисел.Поставленная цель достигается тем,что устройство для вычисления разности двух чисел, содержащее первый ивторой сумматоры, группу элементовНЕ, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИи элемент НЕ, причем первая группавходов первого сумматора соединена3с входами разрядов первого операндаустройства, вторая группа входов пер.вого сумматора - с выходами соответствующих элементов НЕ группы, входыкоторых подключены к соответствующимвходам разрядов второго операнда устройства, выходы разрядов первогосумматора, кроме старшего разряда,соединены с первыми входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИгруппы, выходами соединенных с первой группой входов второго сумматора, вторая группа входов которогосоединена с нулевой шиной устройства,а вход переноса - с выходом элементаНЕ и с выходом знака разности устройства, выходы разрядов второго сумматора соединены с выходами разрядовразности устройства, первый сумматорвыполнен (ш+1)-разрядным, где шразрядность максимального ожидаемогозначения разности (шп, где и - разрядность Вычитаемых чисел), а второйсумматор - ш-разрядным, причем выходсуммы старшего разряда первого сумматора подключен к входу элемента НЕи к вторым входам элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы.На чертеже представлена структурная схема устройства для вычисленияразности двух чисел.Устройство содержит входы первогооперанда 1, входы второго операнда 2,группу элементов НЕ 3, первый сумматор 4, группу элементов ИСКЛЮЧАК 1 ЦЕЕИЛИ 5, элемент НЕ 6, второй сумматор 7,выходы 8 разности и выход 9 знака разности,Устройство работает следующим образом,На входах операндов 1 и 2 сравниваемых чисел А и В соответственноприсутствуют двоичные и-разрядныеЗ=б-Ь 5=(А-Ь)-1 у5 М25 т.е. что имеет место и при сочетании случаев а(Ь и А)В при выполнении ус. ловия М6(2-1) .Если аЬ при А 4 В, то в пределах измененчя М от 0 до (2 -1). сумма Б изменяется соответственно в пределах от (2+ -1) до 2 , т.е. в этом слу- чае что при перестановке слагаемых приобретает вид вычисления поразрядного40 дополнения разности чисел а и Ь2.-(а-Ь)-12 (а-Й.Следовательно, сумма Я равнаБ =Э(Д-В или5=)(М)что также имеет место и при сочетании случаев аЬ и А(В в пределах выполнения условия Мй(21-1).Отсюда следует что числовая обЭ50 ласть существования результата Б на выходе сумматора 4 охватывает (2 ф+1) значений, половина которых в пределах от О до (2 -1) несет в себе ин-3 , 1141 коды этих чисел. Цифровое слово (число) Ю в виде младших (ш+1) разрядов кода числа А с входа операнда 1 подведено поразрядно к одному иэ числовых входов сумматора 4. Цифровое слово (число) Ъ, содержащееся в (ш+1) младших разрядах числа В, с входа операнда 2 инвертируется в каждом разряде группой логических элементов НЕ 3 и подводится к второму числово му входу первого сумматора 4 в виде поразрядного дополнения В(Ь) числаВ(Ь = 2 - Ь,При этом на числовом выходе сумматора 4 формируется результат Б сумми 5 а+Э(Ь) .Пусть М - значение разности. В простейшем случае, когда при изменении М от 1 до 2 аЬ при АВ и сумма Б изменяетсяот 0 до (2-1) соответственно, результат сложения Б очевидно равен 401 4формацию о модуле ра з нос ти чисел А и В при АВ, а другая половина в пределах от 2 до (2 "-1) - о модуле разности чисел А и А при АаВ, при этом ситуация А=В всегда присутствует в середине числовой области возможных значений результата Б.Поскольку формат кода результата Б представлен (ш+1) разрядами, а модуль М разности чисел А и В - ш разрядами, что старший разряд Б,+ циф" рового слова Б может служить индикатором знака разности исходных чисел А и В. Таким образом, старший разряд Бчислового выхода первого сумматора 4, равно как и выхдд присоединенного к нему логического элемента НЕ 6, может служить выходом знака разности сравниваемых чисел А и В. В предлагаемом устройстве информация с разряда Б используется для автоматического преобразования кода результата Б в прямой несмещенный код числа М с помощью блока 5 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и второго сумматора 7. Так, при Б =0 к результату Б во втором сумматоре 7 добавляется "единица", подаваемая на вход переноса этого сумматора с выхода элемента НЕ 6. Тогда на выходе 8 сумматора 7 присутствует прямой несмещенный код числа М. Наоборот, при Б , =1 код результата Б инвертируется в каждом разряде группы элементов ИСКЛЮ 1 ЧАЮЩЕЕ ИЛИ 5 и передается на выход 8 устроиства через сумматор 7 без изменения (на втором числовом входе сумматора 7 присутствует нулевой код). Значит и в этом случае на выходе сумматора 7 присутствует прямой несмещенный код числа М. По сравнению с известным предлагаемое устройство обладает существенно меньшим объемом оборудования.Применение изобретения взамен полноразрядного вычислителя разности двух чисел в экстремальном регуляторе или подобных устройствах позволит упростить аппаратную реализацию, уве личить быстродействие, уменьшить энергопотребление и расширить функ" циональные возможности предлагаемого ,устройства.1141401 Составитель А. Степанедактор В.Данко Техред М.Кузьма Зака дписноеР д. 4/ ППП "Патент", г,ужгород, ул.Проектная,96/36 Тираж 71 ВНИИПИ Государстве по делам изобрет 113035, Москва, Ж ного комитета С ний и открытий 5, Раушская наб Корректор Л. Пилипенк

СмотретьЗаявка

3614903, 05.07.1983

РИЖСКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

КРОЧАКЕВИЧ ВАЛЕРИЙ ВАДИМОВИЧ, САУХАТАС АНТАНАС-САУЛЮС САМУЭЛИО, БОЧКАРЕВА ГАЛИНА ИВАНОВНА

МПК / Метки

МПК: G06F 7/50

Метки: вычисления, двух, разности, чисел

Опубликовано: 23.02.1985

Код ссылки

<a href="https://patents.su/4-1141401-ustrojjstvo-dlya-vychisleniya-raznosti-dvukh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления разности двух чисел</a>

Предыдущий патент: Устройство для деления в системе остаточных классов

Следующий патент: Матричное устройство для деления

Случайный патент: Штамп для гибки скоб из штучных заготовок