Устройство для сложения чисел в из-быточной системе счисления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

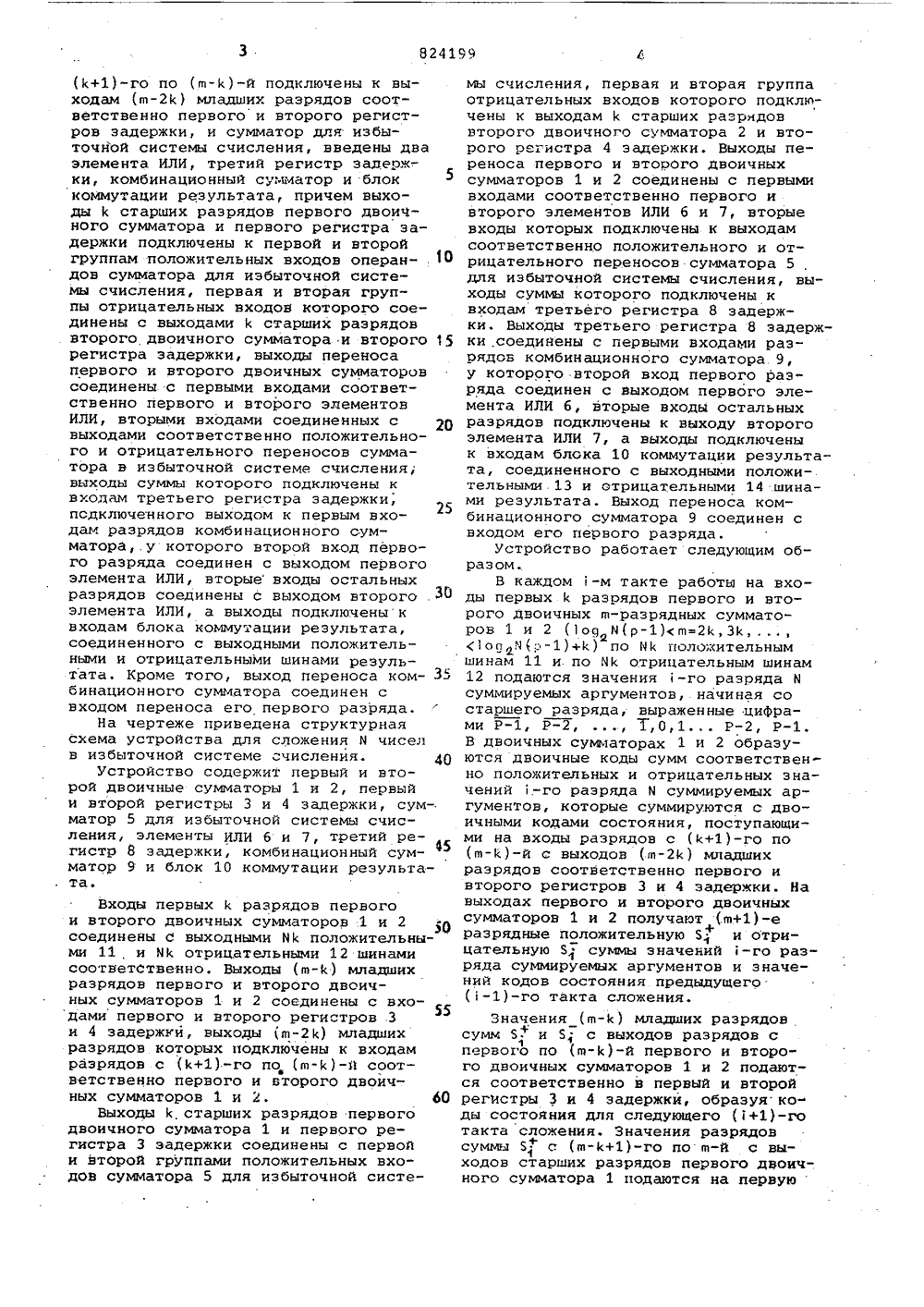

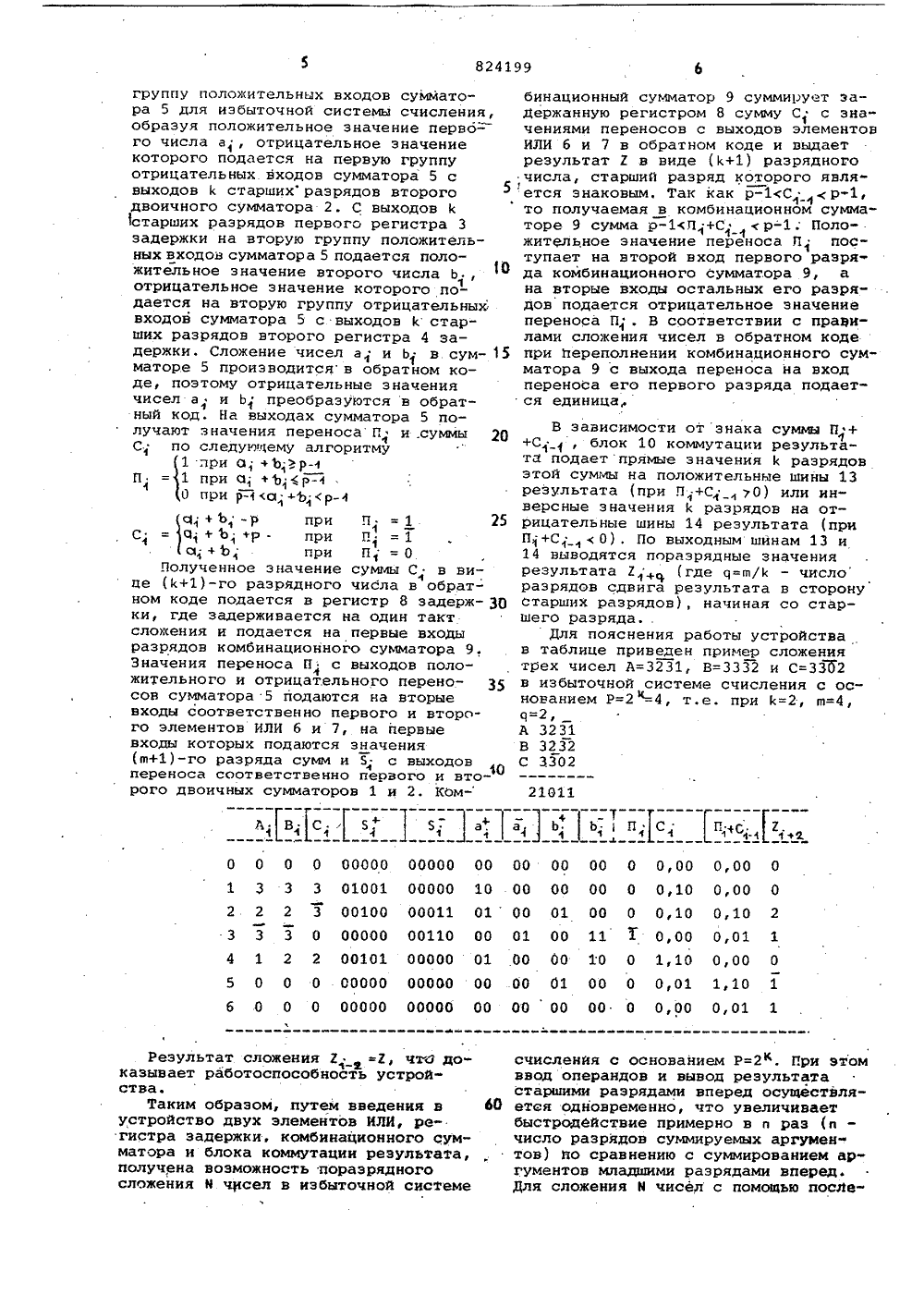

(22) Заявлено 04.07,79 (21) 2792339/18-24с присоединением заявки йо(23) Приоритет Государствеииый комитет СССР ио делам изобретеиий и открытийганрогский радиотехнический институ им. В.Д. Калмыкова 71) Заявитель 4) УСТРОЙСТВО ДЛЯ СЛОВЕНИЯ М ЧИСЕЛ В ИЗБЫТОЧНОСИСТЕМЕ СЧИСЛЕНИЯ Изобретение относится к цифровой вычислительной технике и может быть использовано в вычислительных системах, .работающих в избыточной системе счисления.Известно устройство для сложения чисел, содержащее два функциональных регистра, два шифратора, сумматор и вдй рр, в котором произво дится одновременное сложение нескольких чисел в избыточной системе счис" ления с последовательным поразрядным. вводом операндов 11.Однако устройство осуществляет сложение М чисел только в двоичной избы точной системе счисления.Наиболее близким к предлагаемому является устройство для сложения М чисел в избытоЧной двоичной системе счисления, содержащее первый и вто рой а-разрядные двоичные сумматоры, соединенные с входными шинами соответственно отрицательных и положительных значений слагаеватх, два регистра задержки, входы которых подключены к выходам с первого по (а)-й разряды двоичных сумматоров, и последовательный сумматор в избыточной двоичной системе счисления, первый и второй выходы которого подключены к вы ЗО ходам старших а-х разрядов двоичных сумматоров, а третий и четвертый его входы соединены с выходами старших (а)-х разрядов регистров задержки, в которых производится последовательный поразрядный ввод одновременно М чисел 2 .Недостатком известного устройства является то, что оно работает только в двоичной избыточной системе счисления, т.е. при Р=2.Цель изобретения - расширение функ циональных возможностей, заключающееся в возможности последовательного поразрядного сложения М чисел в избыточной системе счисления с основанием Р=2".Для достижения поставленной цели в устройство, содержащее. первый и второй а-разрядные двоичные сумматоры Г(од М.(р)саод М(р)+1 с, где аф 21, ЗМ входы первых разрядов которых подключены соответственно к М 1 положительным и ММ отрицательиых входным шинамт операндов устройства, первый и второй регистры задержки, подключенные к выходам (а-к) младших разрядов соответственно первого и второго двоичных сумматоров, входы разрядов которых с(1+1)-го по (а)-й подключены к выходам (а) младших разрядов соответственно первого и второго регистров задержки, и сумматор для избыточной системы счисления, введены дваэлемента ИЛИ, третий регистр задержки, комбинационный сумматор и блоккоммутации результата, причем выходы 1 старших разрядов первого двоичного сумматора и первого регистра задержки подключены к первой и второйгруппам положительных входов операн-, 10дов сумматора для избыточной системы счисления, первая и вторая группы отрицательных входов которого соединены с выходами К старших разрядов. второго двоичного сумматора и второго 15регистра задержки, выходы переносапервого и второго двоичных сумматоровсоединены с первыми входами соответственно первого и второго элементовИЛИ, вторыми входами соединенных свыходами соответственно положительного и отрицательного переносов сумматора в избыточной системе счисления,выходы суммы которого подключены квходам третьего регистра задержки,псдключенного выходом к первым входам разрядов комбинационного сумматора,.у которого второй вход первого разряда соединен с выходом первогоэлемента ИЛИ, вторые входы остальныхразрядов соединены с выходом второгоэлемента ИЛИ, а выходы подключены квходам блока коммутации результата,соединенного с выходными положительными и отрицательными шинами результата. Кроме того, выход переноса комбинационного сумматора соединен свходом переноса его первого разряда,На чертеже приведена структурнаясхема устройства для сложения й чиселв избыточной системе счисления. 4 ОУстройство содержит первый и второй двоичные сумматоры 1 и 2, первыйи второй регистры 3 и 4 задержки, сумматор 5 для избыточной системы счисления, элементы ИЛИ б и 7, третий Регистр 8 задержки, комбинационный сумматор 9 и блок 10 коммутации результата,Входы первыхразрядов первого и второго двоичных сумматоров 1 и 2 соединены с выходными 81 положительными 11 и Нас отрицательными 12 шинами соответственно, Выходы (ас) младших разрядов первого и второго двоичных сумматоров 1 и 2 соединены с входами первого и второго регистров 3 и 4 задержки, выходы (а) младших разрядов которых подключены к входам разрядов с (Е+1)-го по (а-)-й соответственно первого и второго двоичных сумматоров 1 и 2. 60Выходы М. старших разрядов первого двоичного сумматора 1 и первого регистра 3 задержки соединены с первой и второй группами положительных входов сумматора 5 для избыточной системы счисления, первая и вторая группа отрицательных входов которого подключены к выходам М старших разрядов второго двоичного сумматора 2 и второго регистра 4 задержки. Выходы переноса первого и второго двоичных сумматоров 1 и 2 соединены с первыми входами соответственно первого и второго элементов ИЛИ б и 7, вторые входы которых подключены к выходам соответственно положительного и отрицательного переносов сумматора 5, для избыточной системы счисления, выходы суммы которого подключены к входам третьего регистра 8 задержки. Выходы третьего регистра 8 задержки .соединены с первыми входами разрядов комбинационного сумматора 9, у которого второй вход первого разряда соединен с выходом первого элемента ИЛИ б, вторые входы остальных разрядов подключены к выходу второго элемента ИЛИ 7, а выходы подключены к входам блока 10 коммутации результата, соединенного с выходными положительными.13 и отрицательными 14 шинами результата. Выход переноса комбинационного сумматора 9 соединен с входом его первого разряда.Устройство работает следующим образом.В каждом 1-м такте работы на входы первыхразрядов первого и второго двоичных а-разрядных сумматоров 1 и 2 (1 ой й(р)а=21,31 с (1 оай(р)+1) по й положительным шинам 11 и.по й 1 отрицательным шинам 12 подаются значения 1-го разряда й суммируемых аргументов,. начиная со старшего разряда, выраженные цифрами Р, Р, , Т,0,1 Р, Р. В двоичных сумматорах 1 и 2 образуются двоичные коды сумм соответственно положительных и отрицательных значений 1-го разряда й суммируемых аргументов, которые суммируются с двоичными кодами состояния, поступающими на входы разрядов с (+1)-го по (а-)-й с выходов (аМ) младших разрядов соответственно первого и второго регистров 3 и 4 задержки. На выходах первого и второго двоичных сумматоров 1 и 2 получают (а+1)-е разрядные положительную 5 и отрицательную 5 суммы значений 1-го разряда суммируемых аргументов и значений кодов состояния предыдущего (1-1)-го такта сложения.Значения (а-М) младших разрядов сумм 5 и 5; с выходов разрядов с первого по (а-М)-й первого и второго двоичных сумматоров 1 и 2 подаются соответственно в первый и второй регистры 3 и 4 задержки, образуя коды состояния для следующего (1+1)-го такта сложения. Значения разрядов суммы 5 с (а+1)-го поа-й с выходов старших разрядов первого двоичного сумматора 1 подаются на первуюдовательных сумматоров для сложения двух чисел в избыточной системе счисления потребовалось бы не менее Мтакихсумматоров, что сложнее предлагаемого устройства примерно в М/2 раза.Формула изобретенияУстройство для сложения М чисел в избыточной системе счисления, содержащее первый и второй а-разрядные двоичные сумматоры Го 9 М(р)с Сев 2 К,З, ,) о 9 М(р)+1, входы первых 1 разрядов которых подключены соответственно к ММ положи тельным и ММ отрицательным входным шинам операндов устройства, первый и второй регистры задержки подключены к выходам (в-М) - младших разрядов соответственно первого и 2 О второго двоичных сумматоров, входы разрядов которых с(1 с+1)-го йо (вс)-й подключены к выходам (аК) младших разрядов соответственно первого и.второго регистров задержки, и сумматор в избыточной системесчисления, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей, заключающегося в возможности последовательного поразрядного сложения М чисел в избыточной системе счисления с основанием Р=2 в него введены два элемента ИЛИ, третий регистр задержки, комбинационный сумматор и блок коммутации результата, причем выходыстарших разря дов первого двоичного сумматора ипервого регистра задержки подключены к первой и второй группам положительных входов операндов сумматооа для избыточной системы счисления,первая и вторая группы отрицательныхвходов операндов которого соединеныс выходами М старших разрядов второгодвоичного сумматора и второго регистра задержки, выходы переноса первогои второго двоичных сумматоров соединены с первыми входами соответственнопервого и второго элементов ИЛИ, вторыми входами соединенных с выходамисоответственно положительного и отрицательного переносов сумматора в избыточной системе счисления, выходы суммы которого подключены к входам третьего регистра задержки, подключенноговыходом к первым входам разрядов комбинационного сумматора, второй вход.первого разряда которого соединен свыходом первого элемента ИЛИ, вторыевходы остальных разрядов соединеныс выходом второго элемента ИЛИ, авыходы подключены ко входам блокакоммутации результата, соединенногос выходными положительными и отрицательными шинами результата устройства. Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРР 634274, кл. С 06 Г 7/385, 1976.2. Авторское свидетельство СССРпо заявке 2665233/18-24,кл. 0 06 Г 7/385, 1978 (прототип).824199 Составитель Н. Слюсарев,Редактор А. Шишкина ТехредА.Бабинец Корректор Г. Наэаро Закаэ 2112/71 Тир ВНИИПИ Государ по делам из 113035, Москва, аж 745ственного комитеобретений и открЖ, Раушская:н Подписное таыти 4/5 илиал ППП фПатент", г. Ужгород, ул, Проектная,

СмотретьЗаявка

2792339, 04.07.1979

ТАГАНРОГСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТИМЕНИ B. Д. КАЛМЫКОВА

ТЕЛЕКОВЕЦ ВАЛЕРИЙ АЛЕКСЕЕВИЧ, ШИРВАНЯН ИЗАБЕЛЛА АНУШЕВАНОВНА, БЕЛАЯ НАДЕЖДА ДМИТРИЕВНА

МПК / Метки

МПК: G06F 7/49

Метки: из-быточной, системе, сложения, счисления, чисел

Опубликовано: 23.04.1981

Код ссылки

<a href="https://patents.su/5-824199-ustrojjstvo-dlya-slozheniya-chisel-v-iz-bytochnojj-sisteme-schisleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для сложения чисел в из-быточной системе счисления</a>

Предыдущий патент: Устройство для сложения в избыточнойсистеме счисления

Следующий патент: Суммирующее устройство

Случайный патент: Гидрораспределитель