Устройство для вычисления логических выражений переменных

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1119004

Авторы: Бобков, Козюминский, Мищенко

Текст

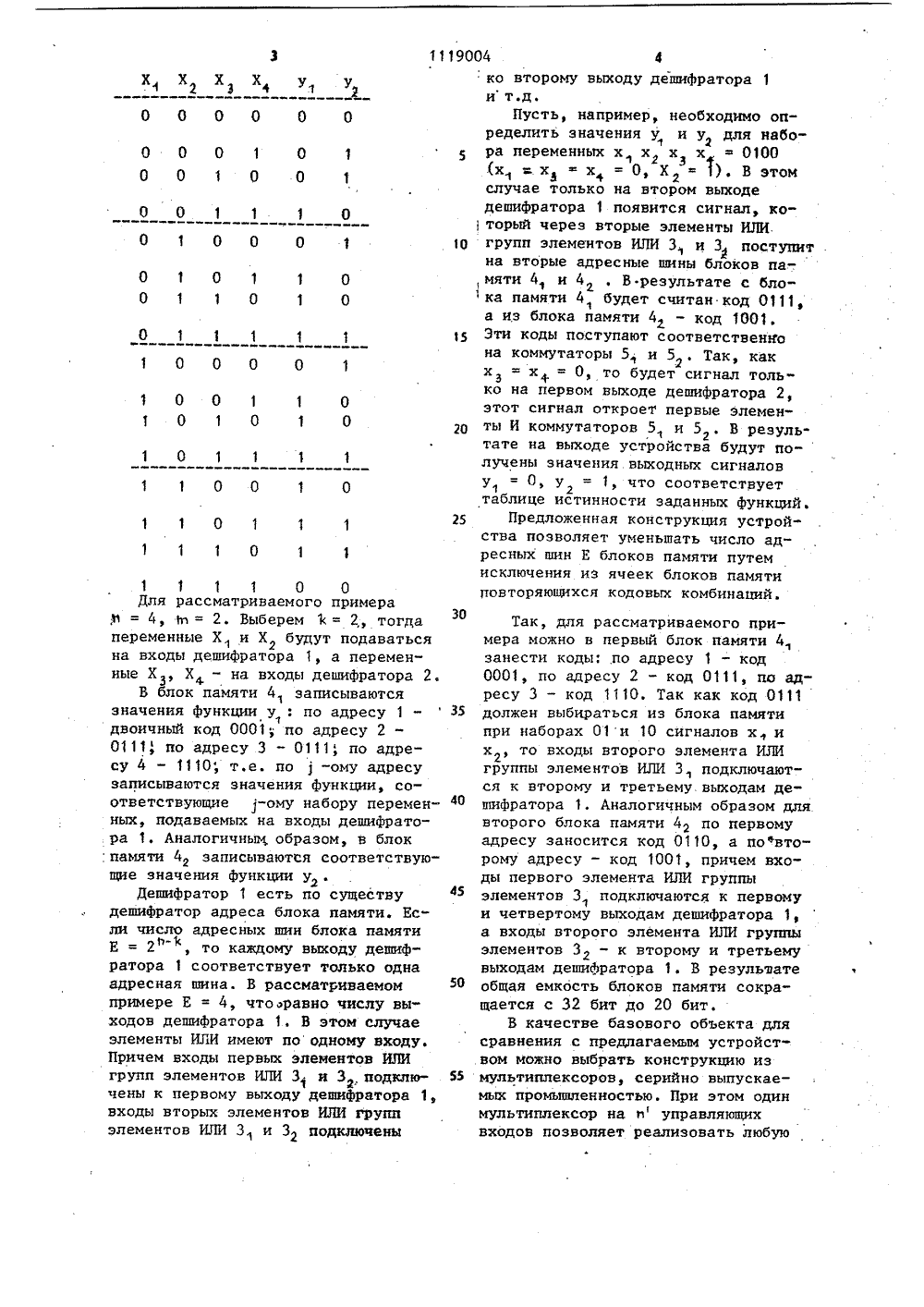

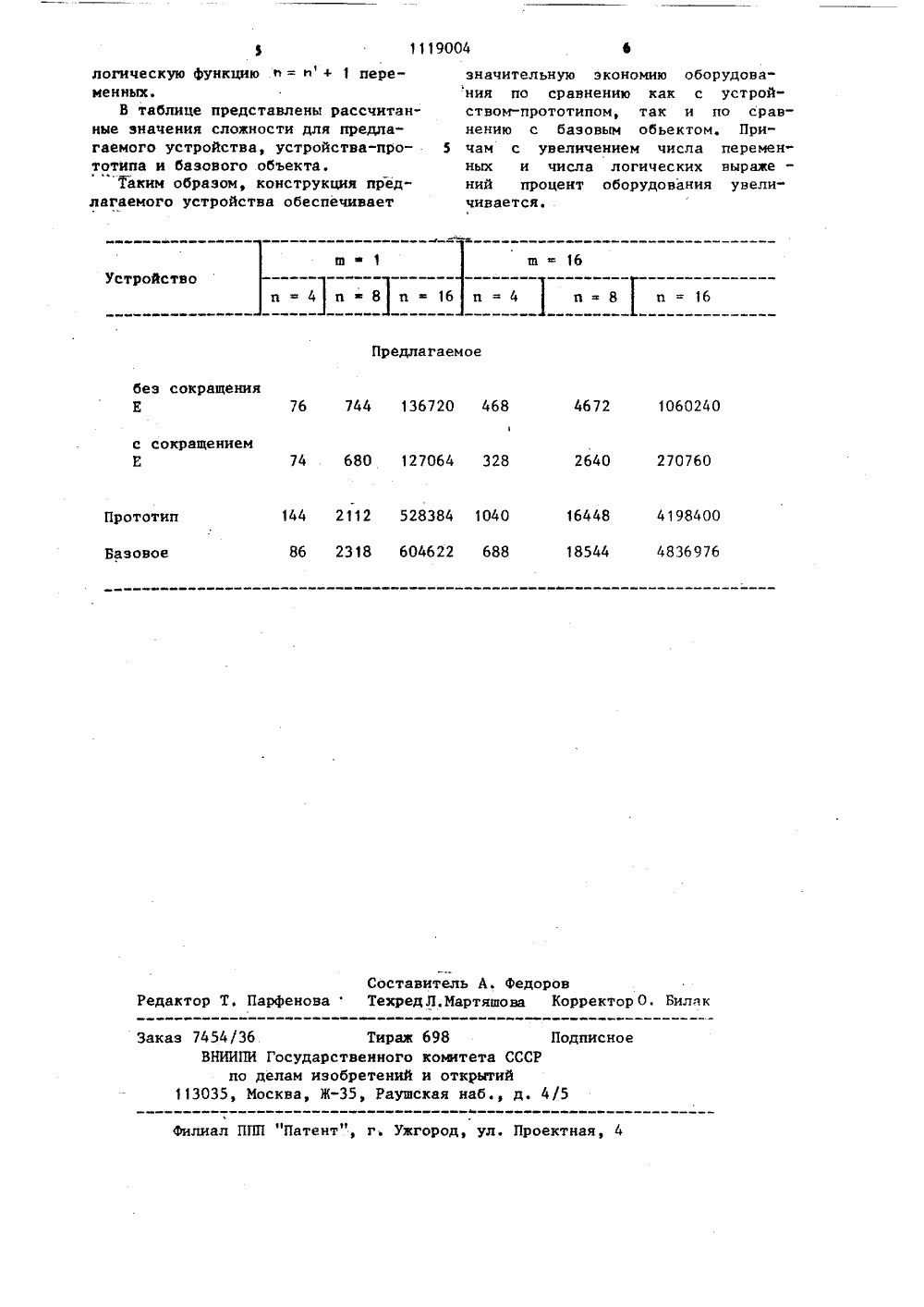

(1% (10 00 ОПИСАНИЕ ИЗОБРЕТЕНИЯ/"К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ к, к лГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ(56) 1. Авторское свидетельство СССР У 962918, кл. С 06 Р 7/00, 1982.2. Авторское свидетельство СССР В 911507, кл. С 06 Г 7/00, 1982.3. Березенко А.И. и др. Микропро.цессорные комплекты повышенного быстродействия", М., "Радио и связь", 1981, с. 157, рис. 73 (прототип).(54)(57) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯЛОГИЧЕСКИХ ВЫРАЖЕНИЙ Ь ПЕРЕМЕННЫХ,содержащее е блоков памяти (- количество реализуемых устройствомвыражений), первый и второй дешифраторы, входы которых соединены соответственно с первой и второй группами входов устройства, о т л ич а ю щ е е с я тем, что, с цельюсокращения аппаратурных затрат, внего введены п групп элементов ИЛИи щ коммутаторов, причем адресныевходы 1-го блока памяти ( 1 = 1,, п) соединены с выходами соответствующих элементов ИЛИ 1-й группы, входы которых соединены с выходами первого дешифратора, значения которых соответствуют одинаковым значениям данного выражения от(и -к) переменных ( 1 - количествовходов первой группы устройства),выходы .1-го блока памяти соединеныс информационными входами 1-го коммутатора, управляющие входы коммутаторов соединены с выходами второго дешифратора, выходы коммутаторовявляются выходами устройства.19004 2 О 30 11Изобретение относится к вычисли" тельной технике и предназначено для реализации систем логических функций, описывающих работу комбинационных узлов различных цифровых устройств.Известно устройство для вычисления логических выражений, содержащее универсальный логический модуль, блок памяти и коммутатор 2М% каналов, которые подключены к 2 выходам блока памяти, вход записи которого подключен к выходу универсального логического модуля, Это устройство позволяет реализовать ,любые логические функции и переменных за 2 " тактов работы 1 .Недостаток устройства - низкое быстродействие.Известно также устройство, содержащее первый дешифратор на и -к входов, второй дешифратор на 1 входов и коммутатор 2" каналов, информационные входы которого подклю" чены к выходам дешифраторов, а управляющие входы - к управляющим входам устройства, Данное устройство реализует любые логические функции и переменных, Для реализации систем из т логических выражений требуется п таких устройств 2 1которых соединены с выходами первого дешифратора, значения которыхсоответствуют одинаковым значениямданного выражения от (и- ) переменных ( Ъ - количество входов первойгруппы устройства), выходы 1-гоблока памяти соединены с информационными входами 1 - го коммутатора, управляющие входы коммутаторов соединены с выходами вто"рого дешифратора, выходы коммутаторов являются выходами устройства,Такое построение устройства позволяет реализовать в нем любуюсистему ш логических функций ппеременных, при этом обеспечивается уменьшение сложности схемы устройства по сравнению сизвестными аналогичными устройствамии,На чертеже изображена структурная схема устройства для вычислениялогических выражений,п переменных. Структурная схема устройства содержит первый дешифратор 1, второй дешифратор 2,п групп элементов ИЛИ 3 - 3 , в блоков памяти 4 - 4коммутаторов 5- 5.Однако данное устройство сложно.Наиболее близким по техническойсущности к изобретению являетсяустройство, содержащее адресный формирователь, входные дешифраторы,блок памяти, выходные дешифраторыи усилители считывания . Устройствопозволяет реализовать систему логических функций 3 .Недостаток устройства - аппаратная избыточность.Цель изобретения - сокращениеаппаратурных затрат,Для достижения поставленной целив устройство для вычисления логи"ческих выражений и переменных, со".держащее в блоков памяти (п - количество реализуемых устройствомвыражений), первый и второй дешифраторы, входы которых соединенысоответственно с первой и второйгруппами входов устройства, введеныФ групп элементов ИЛИ и п коммутаторов, причем адресные входы -го Ыблока памяти ( 1 = 1, , м ) соединены с выходами соответствующихэлементов ИЛИ 1-й группы, входы В схеме устройства входы дешифратора 1 подключены к информационным входам логических переменных Х1 Хустройства, а входы дешифратора 2 - к информационным входам ло" гических переменных Х - Х уст.п.ф%ройства. 2 выходов дешифратора 1 подключены ко входам элементов ИЛИ групп элементов ИЛИ 3, - 3пф выходы которых подключены к соответствующим адресных шинам блоков памяти 4 - 4соответственно, 2" информационных выходов каждого блока памяти 4 - 4, подключены к 21 информационным входам коммутаторов 5 - 5, соответственно. Одноименные управляющие входы коммутаторов 5 - 5 объединены и подключены к соответствующим 2 выходам дешифратора 2. Выходы коммутаторов 5 - 5 являются выходами сигналов у " у устройства,Работу устройства рассмотрим на примере реализации системы двух логических функций четырех переменных, заданных таблицей истинности0 0 0 0 О 0 0 0 0 1 0 1 0 0 1 О 0 1 0 0 1 1 1 0 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 0 1 0 0 1 1 1 1 1 1 0 0 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 1 1 1 1 1 0 0 1 0 1 1 0 1 1 11 1 0 1 1 1 1 1 1 0 0Для рассматриваемого примера Ю = 4, ь = 2. Выберем % = 2 тогда переменные Х и Х 2 будут подаваться на входы дешифратора 1, а переменные ХЗ, Х 4 - на входы дешифратора 2,В блок памяти 4 записываются значения функции у : по адресу двоичный код 0001; по адресу 2 - 0111, по адресу 3 - 0111, по адресу 4 - 1110; т.е. по 1 -ому адресу записываются значения функции, соответствующие 1-ому набору переменных, подаваемых на входы дешифратора 1. Аналогичным образом, в блок памяти 4 записываются соответствую"щне значения функции у .Дешифратор 1 есть по существу дешифратор адреса блока памяти. Ес" ли число адресных шин блока памяти Е = 2 , то каждому выходу дешифьсратора 1 соответствует только одна адресная шина. В рассматриваемом примере Е = 4, чторавно числу выходов дешифратора 1, В этом случае элементы ИЛИ имеют по одному входу. Причем входы первых элементов ИЛИ групп элементов ИЛИ 3 я 3, подключены к первому выходу дешифратора 1, входы вторых элементов ИЛИ групп элементов ИЛИ 3 и 32 подключены 5 1 О 5 20 25 30 35 40 45 50 55 ко второму выходу дешифратора 1 И ТедаПусть, например, необходимо определить значения у и у для набо 2 ра переменных х 1 х х х01003(х х 5х - 0 Х - 1), В этом случае только на втором выходе дешифратора 1 появится сигнал, ко торый через вторые элементы ИЛИ. групп элементов ИЛИ 3 и 3 поступитф на вторые адресные шины блоков па,мяти 41 и 4 . В результате с бло ка памяти 4, будет считан код 01 11, а из блока йамяти 4 - код 1601. Эти коды поступают соответствен 1 го на коммутаторы 5 и 5 , Так какф х = х+ = О, то будет сигнал толь" ко на первом выходе дешифратора 2, этот сигнал откроет первые элементы И коммутаторов 5 н 5 . В реэуль 1 2 тате на выходе устройства будут по" лучены значения выходных сигналов у 1 = О, у 2 = 1, что соответствует таблице истинности заданных функций.Предложенная конструкция устройства позволяет уменьшать число адресных шин Е блоков памяти путем исключения из ячеек блоков памяти повторяющихся кодовых комбинаций.Так, для рассматриваемого примера можно в первый блок памяти 41 занести коды: по адресу 1 - код 0001, по адресу 2 - код 0111, по ад" ресу 3 - код 1110. Так как код 0111 должен выбираться из блока памяти при наборах 01 и 10 сигналов х и х , то входы второго элемента ИЛИ группы элементов ИЛИ 3, подключаются к второму и третьему выходам дешифратора 1. Аналогичным образом для второго блока памяти 4 Ъ по первому адресу заносится код 0110, а пофвторому адресу - код 1001, причем входы первого элемента ИЛИ группы элементов 3 подключаются к первому и четвертому выходам дешифратора 1, а входы второго элемента ИЛИ группы элементов 32 - к второму и третьему выходам дешифратора 1. В резульшате общая емкость блоков памяти сокращается с 32 бит до 20 бит.В качестве базового объекта для сравнения с предлагаемым устройством можно выбрать конструкцию из мультиплексоров, серийно выпускаемых промышленностью. При этом один мультиплексор науправляющих входов позволяет реализовать любую1119004 Устройство ш 1 ш =16и4 и 8 и16 и = 4 и8 и = 16 Предлагаемое без сокращенияЕ 4672 1060240 76 744 136720 468 с сокращениемЕ 2640 270760 74 680 127064 328 144 2112 528384 1040 86 2318 604622 688 ПрототипБазовое 16448 4198400 18544 4836976 Составитель А. ФедоровРедактор Т. ПарфеноваТехредЛ,Мартяшова Корректор О. Биляк Заказ 7454/36 Тираж 698 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д. 4/5Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 логическую функцию ь = и + 1 переменных.В таблице представлены рассчитанные значения сложности для предлагаемого устройства, устройства-прототипа и базового объекта.Таким образом, конструкция предлагаемого устройства обеспечивает значительную экономию оборудова"ния по сравнению как с устройством-прототипом, так и по сравнению с базовым обьектом. При чам с увеличением числа переменных и числа логических выражений процент оборудования увеличивается.

СмотретьЗаявка

3599589, 03.06.1983

МИНСКОЕ ВЫСШЕЕ ИНЖЕНЕРНОЕ ЗЕНИТНОЕ РАКЕТНОЕ УЧИЛИЩЕ ПВО

БОБКОВ ВЛАДИМИР АКИМОВИЧ, МИЩЕНКО ВАЛЕНТИН АЛЕКСАНДРОВИЧ, КОЗЮМИНСКИЙ ВАЛЕРИЙ ДМИТРИЕВИЧ

МПК / Метки

МПК: G06F 7/00

Метки: выражений, вычисления, логических, переменных

Опубликовано: 15.10.1984

Код ссылки

<a href="https://patents.su/4-1119004-ustrojjstvo-dlya-vychisleniya-logicheskikh-vyrazhenijj-peremennykh.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления логических выражений переменных</a>

Предыдущий патент: Универсальный логический модуль

Следующий патент: Устройство для сравнения чисел с допусками

Случайный патент: Светоэлектрическое устройство для автоматического торможения повозок рельсового и безрельсового транспорта