Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

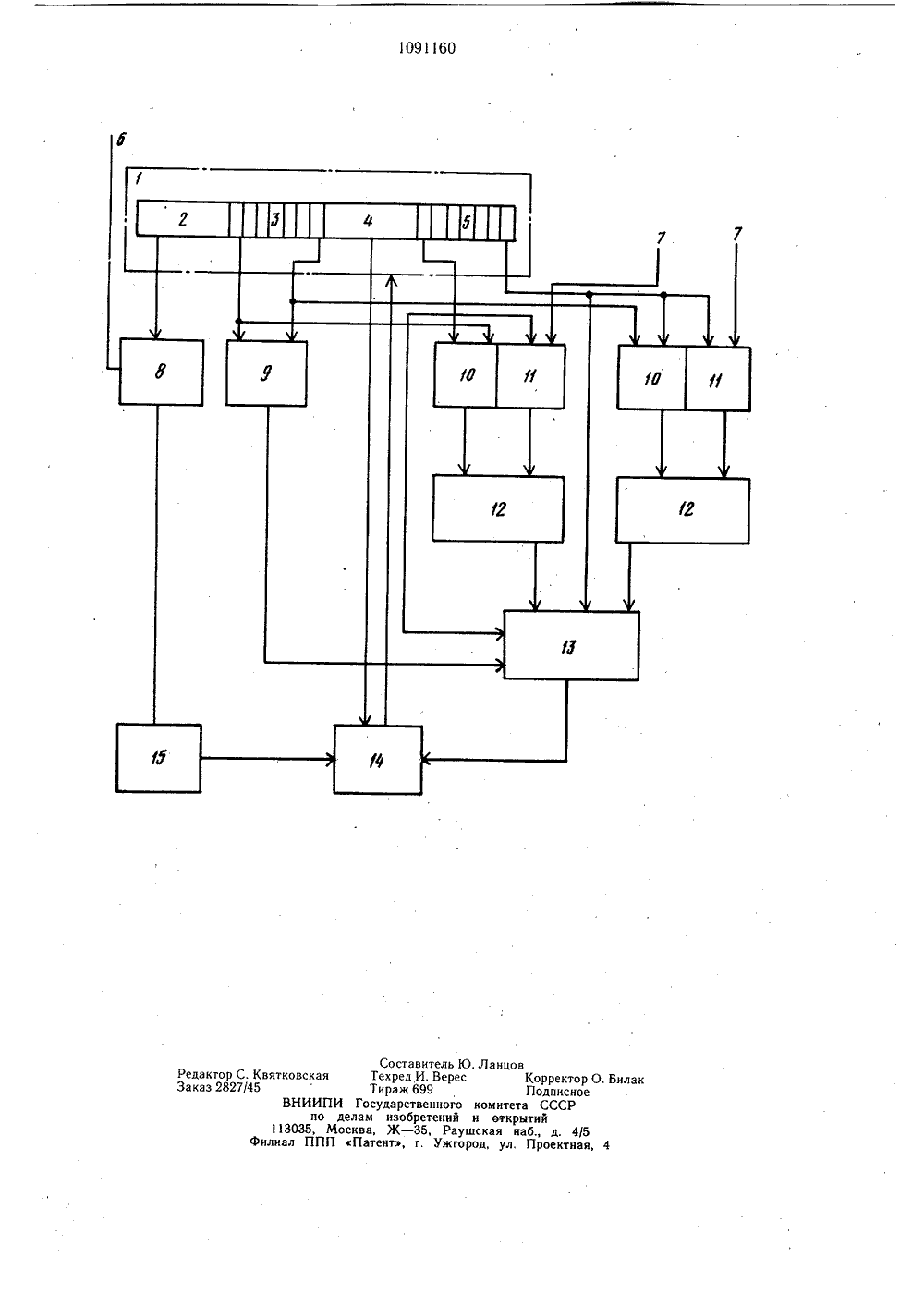

(19) (111 З 15 ц б 06 Р 9/2 ИСАНИЕ ИЗОБРЕТЕНИ ернетик тоти п ОСУДАРСТВЕННЫЙ КОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(71) Ордена Ленина институт кибим. В. М. Глушкова(54) (57) МИКРОПРОГРАММНОЕ УСТРОГ 1 СТВО УПРАВЛЕНИЯ, содержащее блок памяти микрокоманд, регистр микро- команд, генератор тактовых импульсов, регистр адреса и коммутатор, первая группа информационных входов которого соединена с первой группойи выходов кода поля (и= =1, 2, ) блока памяти микрокоманд, вторая группа выходов кода адресного поля которого соединена с первой группой информационных входов регистра адреса, вторая группа информационных входов которого соединена с группой выходов коммутатора вход синхронизации регистра адреса соединен с первым выходом генератора тактовых импульсов, второи выход которого соединен с входом синхронизациирегистра микро- команд, информационный вход которого соединен с выходом кода поля операций блока памяти микрокоманд, группа адресных входов которого соединена с группой выходов регистра адреса, выход регистра микро- команд соединен с выходом микроопераций устройства, отличающееся тем, что, с целью увеличения быстродействия, оно дополнительно содержит схему сравнения,и элементов запрета, и элементов И и и элементов ИЛИ, выходы которых соединены с информационными входами второй группы коммутатора, первый и второй входы 1-го (1=1, 2, ,и ) элемента ИЛИ соединены соответственно с выходом 1-го элемента запрета и с выходом 1-го элемента И, первые входы которых соединены с 1 -м выходом кода адресного поля группы блока памяти микро- команд, второй вход 1 -го элемента запрета соединенс 1-м выходом кода поля ветвления группы блока памяти микрокоманд и с 1-м информационным входом схемы сравнения, выход которой соединен с управляющим входом коммутатора, второй вход 1-го элемента И соединен с 1-м входом логических условий устройства.45 50 55 Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах с микропрограммным управлением.Известно микропрограммное устройство управления для цифровой вычислительной машины, содержашее накопитель запоминающего устройства, регистры - адресный и микрокоманд, дешифратор, генератор тактовых импульсов, логические элементы И и ИЛИ 1.В состав регистра микрокоманды в этом устройстве входят оперативная часть, представляющая собой информацию об импульсах управления; адресная часть, представляющая собой информацию адреса следующей микрокоманды.Формирование адреса следующей микро- команды осушествляется путем коррекции текушего адреса в некоторых разрядах по счетному входу триггеров.Условные переходы осушествляются также путем коррекции кода адреса. При этом выполняю гся специальные микрокоманды, содержашие элементарные операции, которые опрашивают какой-либо выработанный признак, и по этому признаку производится коррекция некоторого определенного разряда адреса. Таким образом осуществляется ветвление по выделенному признаку. При ветвлении по ряду признаков необходимо выполнение ряда микрокоманд, что замедляет процесс анализа логических условий и удлиняет общее время выполнения команд в цифровой вычислительной машине.Наиболее близким к предлагаемому является микропрограммное устройство управления, содержашее блок памяти микрокоманд, генератор тактовых импульсов, регистр адреса и коммутатор, первая группа информационных входов которого соединена с первой группой п выходов (и = 1, 2, ) кода адресного поля блока памяти микро- команд, вторая группа выходов кода адресного поля блока памяти микрокоманд, вторая группа информационных входов которого соединена с группой выходов комутатора, вход синхронизации регистра адреса соединен с первым выходом генератора тактовых импульсов, второй выход которого соединен с входом синхронизации регистра микрокоманд, информационный вход которого соединен с выходом кода поля операций блока памяти микрокоманд, группа адресных входов которого соединена с группой выходов регистра адреса, выход регистра микрокоманд соединен с выходом микроопераций устройства 12 .Работа устройства осуществляется путем выборки из блока памяти микрокоманд в регистр микрокоманд и исполнения последовательности микрокоманд. По окончании выборки очередной команды из оперативной памяти ее код операции передается в регистр 5 1 О 15 20 25 Зо 35 40 операции и хранится там до конца выполнения команды.При выполнении команды с ветвлением происходит срабатывание дешифратора, выходы которого подключают соответствующее логическое условие, по которому происходит переход по признаку, т. е, формирование необходимого адреса перехода.В случае необходимости ветвления по другому признаку микрокоманда, настроенная на этот признак, выполняет следующий условный переход. Таким образом, для осуществления логических переходов по ряду признаков необходимо выполнение ряда микрокоманд, что значительно замедляет работу устройства, особенно при анализе совокупности признаков, возникающих одновременно, например, при обработке многих потоков данных и требующих немедленной реакции устройства управления.Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в микропрограммное устройство управления, содержашее блок памяти микрокоманд, регистр микрокоманд, генератор тактовых импульсов, регистр адреса и коммутатор, первая группа информационных входов которого соединена с первой группойп выходов кода поля (п=1, 2, ) блока памяти микро- команд, вторая, группа выходов кода адресного поля которого соединена, с первой группой информационных входов регистра адреса, вторая группа информационных входов которого соединена с группой выходов коммутатора, вход синхронизации регистра адреса соединен с первым входом генератора тактовых импульсов, второй выход которого соединен с входом синхронизации регистра микрокоманд, информационный вход которого соединен с выходом кода поля операций блока памяти микрокоманд, группа адресных входов которого соединена с группой выходов регистра адреса, выход регистра микро- команд соединен с выходом микроопераций устройства, введены схема сравнения, элементов запрета,л элементов И им элементов ИЛИ, выходы которых соединены с информационными входами второй группы коммутатора, первый и второй входы 3-го ( =1, 2, ,и) элемента ИЛИ соединены соответственно с выходом 1 -го элемента запрета и с выходом 1-го элемента И, первые входы которых соединены с 1-м выходом кода адресного поля группы блока памяти микрокоманд, второй вход 1-го элемента запрета соединен с 1 -м выходом кода поля ветвления группы блока памяти микрокоманд и с 1 -м информационным входом схемы сравнения, выход которой соединен с управляющим входом схемы сравнения, выход которой соединен с управляющим входом коммутатора, второй вход 1-го элемента И соединен с 1-м входом логических условий устройства,На чертеже представлена функциональная схема предлагаемого устройства.Устройство содержит блок 1 памяти микрокоманд с полями 2 кодов микроопераций, 3 ветвления,4 старших разрядов кода адре,са и 5 младших разрядов кода адреса, выход 6 микроопераций, входы 7 логических условий, регистр 8 микрокоманд, схему 9 сравнения, элементы 10 запрета, элементы И 11, элементы ИЛИ 12, коммутатор 13, .регистр 14 адреса, генератор 15 тактовых 10 импульсов.Устройство работает следующим образом.В исходном режиме блок 1 памяти микро- команд находится в режиме чтения и на его выходах формируется информация, соответствующая содержимому регистра 14 адреса. (цепи занесения начального адреса выполнения команды в адресный регистр не показаны). В поле 2 кодов микроопераций выбирается код очередной микрокоманды для управления внешним устройством. В поле 4 20 старших разрядов кода адреса формируется старшая часть адреса перехода следующей микрокоманды, поступающая на вторую группу входов регистра 14 адреса.Если в поле 3 ветвления нули, то в поле 5 кода младших разрядов адреса указывается младшая часть адреса перехода следующей микрокоманды. Нули с выхода поля 3 ветвления поступают на схему 9 сравнения, которая формирует управляющий потенциал, подключающий поле 5 кода младших разрядов адреса перехода через коммутатор 13 к первой группе входов регистра 14 адреса. При поступлении импульса с выхода генератора тактовых импульсов происходит занесение информации в регистр 14, а также в регистр 8 микрокоманд. После чего в блоке З 1 памяти микрокоманд за счет изменения информации в регистре 14 выбираются данные для нового поля 2 кода микроопераций, 3 ветвления, 4 старших и 5 младших разрядов адреса очередной микрокоманды, а с выхода регистра 8 микрокоманд поступают 4 О на выход 6 для исполнения микрокоманды внешним устройством. В результате выполнения микрооперации внешним устройством формируются признаки логических условий, которые поступают на входы 7 устройства, 4 Выборку логических условий осуществляют позиционным кодом поля 5 кода младших разрядов адреса. Единица определенного разряда этого кода указывает на подключение соответствующего разряда логического условия, нуль - на его запрет. Коды выбранных разрядов логических условий через элементы И 11 и ИЛИ 12 поступают на коммутатор 13. Нули поля 5 младших разрядов адреса поступают на входы элементов 10 запрета, подключая фиксированные кодовые комбинации из поля 3 ветвления. Эти комбинации дополняют выбранное подмножество разрядов логических условий до полно- разрядного адреса, который через коммутатор 13 поступает в младшую часть адресного регистра 14.При выбранном подмножестве из н ло-. гических условий количество возмож ных переходов из определенного адреса будет равно 2". В блоке 1 памяти микрокоманд этому соответствует 2" различных адресов. Дополняющие коды, указанные в поле 3 ветвления, являются привязкой этой группы адресов в блоке 1 памяти.Выбор дополняющих кодов может осуществляться произвольным образом. Это дает возможность перемещения групп адресов условных переходов в блоке 1 памяти для плотного их размещения. Состояния разрядов поля 3 ветвления, не входящие в дополняющие коды, на адрес перехода не влияют. Поэтому эти разряды могут быть использова ны для указания наличия разветвлений в микропрограммах в случае нулей в дополняющем поле.Ненулевой код поля 3 ветвления вызывает срабатывание схемы 9 сравнения, выходной сигнал которой поступает на коммутатор 13, подключая сформированную младшую часть адреса к первой группе входов регистра 14 адреса, которая с приходом очередного импульса с выхода генератора 15 тактовых импульсов вызывает новую выборку микрокоманд с блока 1 памяти.Таким образом, за один такт работы предлагаемое устройство позволяет осуществлять логический анализ любого подмножества внешних логических условий, что в конечном итоге повышает быстродействие этого устройства по сравнению с прототипом, в котором отсутствует возможность анализа любого подмножества логических условий за один такт работы.новКорректор О, БилПодписноетета СССРоткрытийнаб., д. 4/5ул. Проектная, 4 Составитель Ю. ЛаТехред И. ВересТираж 699 Государственного ком елам изобретений и сква, Ж - 35, Раушска Патент, г. Ужгород,

СмотретьЗаявка

3543251, 21.01.1983

ОРДЕНА ЛЕНИНА ИНСТИТУТ КИБЕРНЕТИКИ ИМ. В. М. ГЛУШКОВА

БЕЛЯЕВ АНАТОЛИЙ КОНСТАНТИНОВИЧ, КОРНИЕНКО ГРИГОРИЙ ИВАНОВИЧ, ЯРОВАЯ НАТАЛЬЯ ВИКТОРОВНА, МУДЛА БОРИС ГОРДЕЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 07.05.1984

Код ссылки

<a href="https://patents.su/4-1091160-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство управления

Следующий патент: Устройство для управления обслуживанием заявок в порядке поступления

Случайный патент: Газодинамический подшипник скольжения