Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

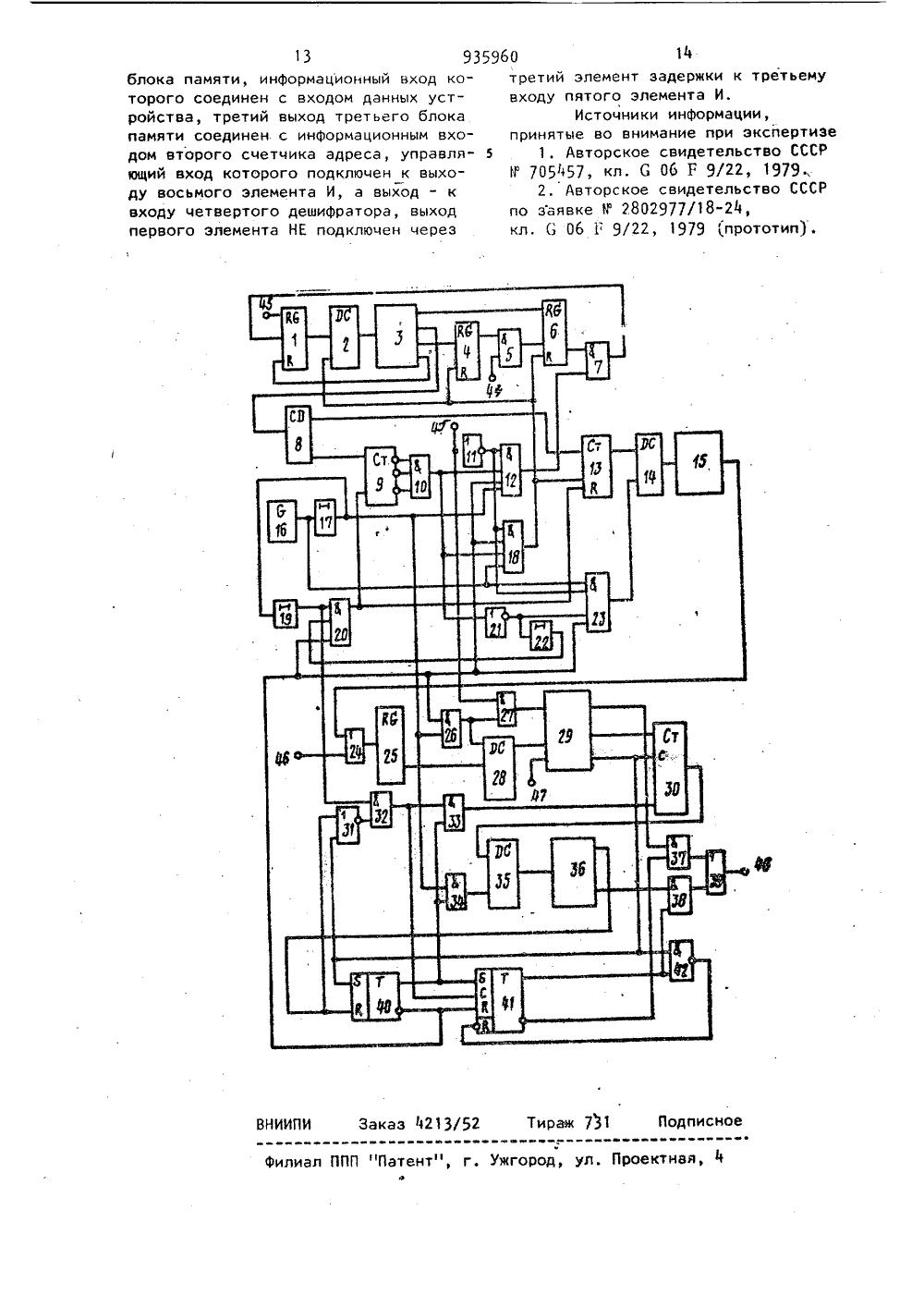

ОП ИСАНИЕИЗОБРЕТЕН ИЯХ АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскикСфцмалмстыческыиРвслублмк и 935960(22) Заявлено 13.10. 80 (21) 3211181/18-2 чс присоединением заявки Ж -(51)М. Кд, С 06 Р 9/22 Ркударотаэииый комитат СССР ию дамам изобретеиий и открытий(71) Заявитель 51) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ Изобретение относится к вычислительной технике и может быть использовано в качестве устройства Чправления высоконадежных микропрограммных процессоров.Известно микропрограммное устройство управления с контролем и восстановлением 11.Недостатком этого устройства является низкая функциональная надеж 1 о ность, вызванная потерей работоспособности процессором, если выполнение любой из микрокоманд сопровождается Чстойчивым отказом. При обнаружении сбоев в таких устройствах осчщест 15 вляется повторение соответствующих микрокоманд и, если после определенного числа повторений сбой не чстраняется, производится блокировка работы и переход в режим диагностирования.Наиболее близким к изобретению по технической сущности и достигаемому положительному эфФекту из микропрограглмных устройств управления явля-, ется устройство, содержащее два регистра адреса, три дешифратора, три блока памяти, регистр логических чсловий, буферный регистр, шифратор, счетчик числа микрокоманд, счетчик адреса, два триггера, генератор тактовых импульсов, три элемента задержки, два элемента НЕ, пять элементов И, три блока элементов И 12 3.Однако Ч этого устройства низкая ФЧнкциональная надежность, вследствие которой процессор теряет работоспособность в случае отказа при выполнении любой из микрокоманд.Цель изобретения - повышение функциональной надежности устройства,Поставленная цель достигается тем, что микропрограммное Чстройство Чправления, содержащее два регистра адреса, три дешифратора, три блока памяти, регистр логических условий, буферный регистр, шифратор, счетчик числа микрокоманд, счетчик адреса, 935960два триггера, генератор тактовых импульсов, три элемента задержки, дваэлемента НЕ, пять элементов И, триблока элементов И, причем первый,второй, третий и четвертый выходыпервого блока памяти соединены соответственно с установочным входомадресного регистра, информационнымвходом регистра логических условий,входом шифратора, первым входом буферного регистра, установочный входкоторого соединен с установочным входом первого дешифратора, установок ними входами регистра логических условии, счетчика адреса и с выходомпервого элемента И, первый вход которого подключен к выходу генератораимпульсов, а входу первого элементазадержки и к первому входу второгоэлемента И, второй вход которогочерез первый элемент НЕ соединен свыходом третьего элемента И, вторымвходом первого элемента И и первымвходом четвертого элемента И, выходкоторого подключен к первому входупервого блока элементов И, второйвход которого соединен с выходом бу" 20 ферного регистра, второй вход которого подключен к выходу второго блокаэлементов И, первый вход которогоявляется входом логических условийустройства, а второй вход соединен свыходом регистра логических условий,выход первого блока элементов И соединен с первым входом первого регистра адреса, второй вход которогоподключен к входу кода операций устройства, а выход - к входу первогодешифратора, выход которого соединенс входом первого блока памяти, второй вход третьего элемента И соеди 35 фъ ки и входом второго элемента задержки, выход которого соединен с первым входом пятого элемента И, входы третьего элемента И подключены к выходам счетчика числа микрокоманд, вход которого соединен с первым выходомшифратора, второй выход которого подключен к входу счетчика адреса, выход которого соединен с.входом второго дешифратора, установочный вход которого соединен с выходом второго элемента И, а выход - с входом второго блока памяти, выход второго регистра адреса подключен к входу третьего дешифратора. выход которого соединен с входом третьего блока памяти,нен с выходом первого элемента задержпервый выход которого соединен с первым входом третьего блока элементов И, дополнительно содержит четвертый запоминающий блок, четвертый дешифратор, второй счетчик адреса, шестой, седьмой, восьмой, девятый и десятыйэлементы И, четвертый блок элементовИ, первый и второй блоки элементов ИЛИ, элемент ИЛИ-НЕ, причем выход второго блока памяти соединен с первым входом первого блока элементов ИЛИ, второй вход которого подключен к входу адреса устройства, а выход - к входу второго регистра адреса, входуправления перезаписью устройства соединен с первым входом шестого элемента И, а через второй элемент НЕ- с третьими входами первого, второго и четвертого элементов И, четвертые входы которых подключены к второму входу пятого элемента И, к первому входу седьмого элемента И, к нулевому входу первого триггера и к нулевому выходу второго триггера, единичный выход которого соединен с единичным входом первого триггера, спервыми входами восьмого и девятогоэлементов И, тактирующий вход первоготриггера подключен к второму входувосьмого элемента И и к выходу девятого элемента И, первый вход которогосоединен с выходом второго элементазадержки, второй вход - с выходомэлемента ИЛИ-НЕ, первый вход которого соединен с единичным входом второго триггера, с первым входом десятого элемента И, со вторым выходомтретьего блока памяти и с тактирующим входом второго счетчика адреса,второй вход элемента ИЛИ-НЕ подклю"чен к нулевому входу второго триггера и первому выходу четвертого бло.ка памяти, второй выход которогоподключен к первому входу четвертогоблока элементов И, второй вход которого соединен с единичным выходомпервого триггера и с вторым входомдесятого элемента И, выход которогоподключен к асинхронному инверсномувходу первого триггера, нулевой выход которого соединен с вторым входом третьего блока элементов И, выход которого соединен с первым входомвторого блока элементов ИЛИ, второйвход которого подключен .к выходу четвертого блока элементов И, а выходк выходу микрооперации устройства,вход четвертого блока памяти соеди935960 нен с выходом четвертого дешифратора , установочный вход которого соединен с выходом девятогоэлемента И, второй вход которого подключен к выходу первого элемента за- Юдержхи и к второму входу седьмогоэлемента И, выход которого соединенс установочным входом третьего дешифратора .и с вторым входом шестогоэлемента И, выход которого подключен 1 Ок управляющему входу третьего блокапамяти, информационный вход которого соединен с входом данных устройства, третий выход- третьего блока памяти соединен с информационным вхо-дом второго счетцика адреса, управляющий вход которого подключен к выходу восьмого элемента И, а выходк входу четвертого дешифратора, выход первого элемента НЕ подключен 20через третий элемент задержки с третьим входом пятого элемента И.Сущность изобретения состоит вповышении функциональной надежностипутем, замены микрокоманд, при выполнении которых фиксируется устой 1цивый отказ, эквивалентными последо" . вательностями других микрокоманд,На чертеже представлена функциональная схема предлагаемого микропро- зограммного устройства управления.Устройство содержит регистр 1 адреса, дешифратор. 2, блок 3 памяти, регистр 4 логических условий, блок 5элементов И, буферный регистр 6, блок7 элементов И, шифратор 8, счетчик 9микрокоманд, элемент И 10, элементНЕ 11, элемент И 12, счетчик 13 адреса, дешифратор 14,.блок 15 памяти,40генератор 16 тактовых импульсов, элемент 17 задержки, элемент И 18, элемент 19 задержки, элемент И 20, элемент НЕ 21, элемент 22 задержки, элемент И 23, блок 24 элементов ИЛИ, регистр 25 адреса операционных микро 45команд, элементы И .26 и 27, дешифратор 28, блок 29 памяти, счетчик 30адреса, элемент ИЛИ-НЕ 31, элементы.И 32-34, дешифратор 35, блок 36 памяти, блоки. 37 и 38 элементов И, блок о39 элементов ИЛИ, триггеры 40 и 41,элемент И 42, вход кода операции,вход проверки логических условий,вход 43 управления перезаписью, вход44 адреса, вход 45 данных, выход 46 ф устройства.Рассмотрим работу предлагаемого устройства. 6В исходном состоянии все регистры и элементы памяти находятся в нулевом состоянии.Устройство имеет следующие режимы работы: перезаписи информации в запоминающий блок 29; выполнениехранимых в запоминающих блоках 3, 15 и 29 мик ропрограмм; автоматической коррекции микропрограмм. Первый режим используется при на" чальной записи информации в блок 29 и коррекции его содержимого. В этом режиме на вход 43 поступает единич-. ный сигнал управления перезаписью,который разрешает прохождение импульсов записи через элемент И 27. Одновременно через элемент НЕ 11 закрываются элементы И 12, 18 и 23Со входа 44 через блок 24 на регистр 25 поступает последовательность адресов, а на вход 45 - последовательность кодов данных. Тактовые импульсы от ге" нератора 16 через элемент 17 задержки и открытый элемент И 26 запускают дешифратор 28. Через элемент И 27 навход блока 29 поступают единичныеимпульсы записи и данные со входа 45 записываются по адресу, определяемому содержимым регистра 25. На выходе блоков 29 и 36 при этом нулевые сигналы.При подаче нулевого сигнала на вход 43 закрывается элемент И 27:и запрещается поступление единичных им-пульсов записи, блок 29 переходит в режим считывания информации, Одновременно единичным выходным сигналом элемента НЕ 11 открываются элементы И 12, 18 и 23. Перед выполнением очередной линейной последовательности счетчик 9 микрокоманд находится в нулевом состоянии, и на выходе элемента И 10 устанавливается единичный сигнал. Этим сигналом открываются элементы И 12 и 18 и через элемент НЕ 21 закрывается элемент И 23. Еди-, ничный сигнал на нулевом выходе триг" гера 40 также открывает элементы И 12, 18, 20, 23 и 26 по соответствующим входам. Тактовый импульс с выхода генератора 16 через элемент И 18 устанавливает в "0" счетчик 13 адреса, буферный регистр 6 и запускает, дешифратор 2 адреса. На регистр 1 ад.реса в начале микропрограмм поступа- ет код операции и по соответствующе" му ему адресу производится считывание из блока 3. С выхода блока 3 кодследующего адреса записывается в буферный регистр 6, код проверяемых логических условий поступает на регистр 4, откуда через блок элементов И 5, на второй вход которого поступает код логических условий, подается на буферный регистр б, где таким образом формируется следующий адрес. Импульсом с выхода блока 3 регистр 1 адреса устанавливается в нулевое со 1 О стояние и подготавливается к приему информации. Номер текущей последовательности поступает на вход шифраторов 8, где он преобразуется в код начального адреса текущей линейной последовательности, записываемый в счетчик 13, и код числа микрокоманд в линейной последовательности, записываемый в счетчик 9 микрокоманд, Задержанный тактовый импульс с выхо да элемента 17 задержки через элемент И 12 открывает блок 7 элементов И, икод следующего адреса перезаписывается из буферного регистра 6 в регистр 1 адреса. Как только счетчик 9 устаа навливается в отличное от нуля состояние, на выходе элемента И 1 О появляется нулевой сигнал, закрывающий элементы И 12 и 18. Элемент И 23 при этом .открывается. Задержанный элементом 22 низкий уровень сигнала на входе элемента И 20 не позволяет импульсу с выхода элемента 19 изменить состояние счетчиков 9 и 13. Следующий тактовый импульс от генера- З тора 16 через элемент И 23 запускает дешифратор 14, и из блока 15 осуществляется считывание по адресу, опрецеляемому счетчиком 13. Адрес операционной микрокоманды с выхода блока 40 15 через блок 24 элементов ИЛИ записывается в регистр 25 адреса операционных микрокоманд. После установления кода адреса в регистре 25 на элемент И 26 поступает задержанный тактовый импульс 5 с выхода элемента 17. Так как элемент И 26 открыт, этот импульс запускает, дешифратор 28, и из блока 29 считывается код операционной микрокоманды, который через блоки 37 и 39 элементов о И и элементов ИЛИ поступает на выход 46, После окончания считывания микро- команды из блока 29 появляется задержанный тактовый импульс на выходе элемента 19, который проходит через открытый элемент И 20, уменьшая на единицу содержимое счетчика 9 и увеличивая на единицу содержимое счетчи 60 8ка 13 адреса, Таким образом, по адресам, считываемым из блока 15, считываются остальные операционные микрокоманды линейной последовательности,После считывания последней микрокоманды текущей линейной последовательности счетчик 9 микрокоманд устанавливается в нулевое состояние, Далееосуществляется считывание из блока 3и считвание микрокоманд следующейлинейной последовательности описаннымобразом.8 процессе функционирования процессора в его операционной части возникают отказы, в результате чего некоторые микрокоманды не могут быть выполнены, Однако, благодаря естественнойфункциональной избыточности системымикрокоманд, возможна замена однихмикрокоманд эквивалентными им послЕдовательностями других микрокоманд исоответствующая коррекция микропрограмм. В этом режиме в блоке 29 поадресам, соответствующим операционныммикрокомандам, при выполнении которыхфиксируется отказ, записаны коды, содержащие поле операционной микрокаманды, поле адреса и поле метки. В поле операционной микрокоманды записыва-,ется первая операционная микрокоманда эквивалентной последовательностимикрокоманд, В поле адреса записывается адрес второй микрокоманды эквивалентной последовательности, хранимойв блоке 36. В поле метки записывается единица, определяющая переход к выполнению эквивалентной последовательности микрокоманд, Коррекция содержимого запоминающего блока 29 осуществляется в первом режиме по результатам диагностики,1Если при считывании операционноймикрокоманды из блока 29 поступаетединичный сигнал, то переход к выполнению эквивалентной последовательности микрокоманд осуществляется следующим образом.Первая операционная микрокомандвс выхода блока 29 через блоки 37 и39 элементов И и ИЛИ поступает на выход устройства 46. По единичному сигналу в счетчик 30 записывается адресмикрокоманды эквивалентной последовательности. Одновременно триггер 40устанавливается в единичное состоя ние. При этом закрываются элементыИ 12, 18, 20, 23 и 26 и открываютсяэлементы И 34 и 35. После считыванияК 5Пос ьку В.о К 71,ормула изобретени Микропрограммное устройство управления,.содержащее два регистра адреса, три дешифратора, три блока па" мяти, регистр логических условий, бу" Ферный регистр, шифратор, счетчик чи. сла микрокоманд, счетчик адреса, два триггера, генератор тактовых импульсов, три элемента задержки, два элемента НЕ, пять элементов И, три блока элементов И, причем первый, второй, третий и четвертый выходы первого блока памяти соединены соответственно с установочным входом регистра адреса, информационным входом регист - ра логических условий, входом шифра" тора, первым входом буферного регистра, установочный вход котррого соеди" нен с установочным входом первого де" 9 93596 информации из блока 29 на вход элемента И 32 поступает задержанный тактовый импульс с выхода элемента 19, Но элемент ИЛИ-НЕ 31 и элемент И 32 закрыты, и перезаписи состояния 5 . триггера 40 в триггер 41 не происходит. Не изменяется также содержимое счетчика 31 и при поступлении следующего тактового импульса, задержанного элементом 17., элемент И 26 за крыт, и дешифратор 28 не запускается. Но импульс с выхода элемента 17 через открытый элемент И 34 запускает дешифратор 35, и по адресу, определяемому содержимым счетчика 30, произво дится считывание операционной микро- команды эквивалентной последовательности из блока 36. Задержанный тактовый импульс с выхода элемента 19 через элемент И 32 синхронизирует пере запись состояния триггера 40 в триггер 41, а через последовательно соединенные элементы И 32 и 33 осуществляется приращение на единицу содержимого счетчика 30. Триггер 41 устанавливается в единичное состояние в момент,. когда на выходе запоминающего блока 36 считана операционная микракоманда эквивалентной последовательности, Тогда происходит переклю- Зо чение, и через открытый блок 38 элементов И и блок 39 элементов ИЛИ на выход 46 поступает операционная микрокоманда эквивалентной последовательности, записанная в блоке 36. 3 Далее, аналогичным образом считываются последующие микрокоманды зкви" валентной последовательности из бло" ка 36. Состояние счетчиков 9 и 13 не изменяется, так как элемент И 20 4 в закрыт и импульсы с выхода элемента 19 через него не проходят, При считывании последней микрокоманды эквивалентной последовательности единичный сигнал устанавливает триггер 42 в нулевое состояние. При этом элементы И 33 и 34 закрываются, а элементы И 12, 18, 20, 23 и 26 открываются, Таким образом, осуществляется пере" ход к считыванию из блока 28. Задер в жанный импульс с выхода элемента 19 через элемент И 20 уменьшает на еди" ницу содержимое счетчика 9 и увеличивает на единицу содержимое счетчика 13. Таким образом, вся эквивалентная последовательность микрокоманд фиксируется как одна микрокоманда. В следующем такте производится считывание 0 10 микрокоманды из блока 28 описанным образом. Так как на вход элемента ИЛИНЕ 31 поступают нулевые сигналы, то единичным выходным сигналом он открывает элемент И 32, и задержанный тактовый импульс с выхода элемента 19 поступает на вход синхронизации триггера 41. Триггер 41 устанавливается в нулевое состояние и к выходу 45 через блоки 37 и 39 элементов И и ИЛИ подключается выход блока 28, на выходе которого уже считана очередная операционная микрокоманда. Далее устройство функционирует описанным образом, последовательно считывая операционные микрокоманды.Среднее время между отказами процессора с предлагаемым микропрограммным устройством управления, когда восстановление его работы возможИэ только заменой функциональных блоков, можно оценить с помощью следующей формулы Т=где / ф Б Х сум"2 "щ" марная интенсивйость отказов при вы" полнении микрокоманд подмножества Г.Выигрыш по среднему времени между отказами процессора известного устройства и предлагаемого устройства управления определяется следующей ормулойТ9359 25 30 шифратора, установоцными входами регистра логических условий, счетчика адреса и с выходом первого элемента И, первый вход которого подключен к выходу генератора импульсов, к входу первого элемента задержки и к первому входу второго элемента И, второй вход которого через первый элемент НЕ соединен с выходом третьего элемен. та И, вторым входом первого элемента1 О И и первым входом четвертого элемента И, выход которого подключен к первому входу первого блока элементов И, второй вход которого соединен с выходом буферного регистра, второй вход которого подключен к выходу второго блока элементов И, первый вход которого является входом логических условий устройства, а второй вход соединен с выходом регистра логических условий, выход первого блока элементов И соединен с первым входом первого регистра адреса, второй вход которого подключен к входу кода операций устройства, а выход - к входупервого дешифратора, выход которого соединен с входом первого блока памяти, второй вход третьего элемента Исоединен с выходом первого элементазадержки и входом второго элементазадержки, выход которого соединен с первым входом пятого элемента И, входы третьего элемента И подключены к выходам счетчика числа микрокоманд, вход которого соединен с первым выходом шифратора, второй выход которого подключен к входу счетчика адреса, выход которого соединен с входом второго дешифратора, установоц 40 ный вход которого соединен с выходом второго элемента И, а выход - с входом второго блока памяти, выход второго регистра адреса подключен квходу третьего дешифратора, выход45 которого соединен с входом третьего блока памяти, первый выход которого соединен. с первым входом третьего блока элементов И, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности за счет коррекции мик 50 ропрограмм, оно содержит четвертый блок памяти, четвертый дешифратор, второй счетчик адреса, шестой, седьмой, восьмой, девятый и десятый элементы И, четвертый блок элементов И, первый и второй блоки элементов ИЛИ, элемент ИЛИ-НЕ, причем выход второго блока памяти соединен с первым 60 12входом первого блока элементов ИЛИ, второй вход которого подключен к входу адреса устройства, а выход - к входу второго регистра адреса, вход управления перезаписью устройства соединен с первым входом шестого элемента И, а через второй элемент НЕ - с третьими входами первого, второго и четвертого элементов И, цетвертые входы которых подключены к второму входу пятого элемента И, к первому входу седьмого элемента И, к нулевому, входу первого триггера и к нулевому выходу второго триггера, единичный выход которого соединен с единичным входом первого триггера, с первыми входами восьмого и девятого элементов И, тактирующий вход первого триггера подключен к второму входу восьмого элемента И и к выходу девятого элемента И, первый вход которого соединен с выходом второго элемента задержки, второй вход - с выходом элемента ИЛИ-НЕ, первый вход которого соединен с единичным входом второго триггера, с первым входом десятого 1элемента И, с вторым выходом третьего блока памяти и с тактирующим входом второго счетчика адреса, второй вход элемента ИЛИ-НЕ подключен.к нулевому входу второго триггера и первому выходу четвертого блока памяти, второй выход которого подключен к первому входу цетвертого блока элементов И, второй вход которого соединен с единичным выходом первого триггера и со вторым входом десятого элемента И, выход которого подключен касинхронному инверсному входу первого триггера, нулевой выход которого соединен с вторым входом третьего блока элементов И, выход которого соединен с первым входом второго блока элементов ИЛИ, второй вход которого подключен к выходу четвертого блока элементов И, а выход - к выходу микрооперации устройства, вход четвертого блока памяти соединен с выходом четвертого дешифратора, установочный вход которого соединен с выходом девятого элемента И, второй вход которого подключен к выходу первого эле-; мента задержки и к второму входу седьмого элемента И, выход которого соединен с установочным входом третьего дешифратора, и с вторым входом шестого элемента И, выход которого подключен к управляющему входу третьегоЗаказ 4213/52 Тираж 731 Подписн НИИП милиал ППП "Патент", г. Ужгород, ул. Проектная, 4 13 935960 14блока памяти, информационный вход ко- третий элемент задержки к третьемуторого соединен с входом данных уст- входу пятого элемента И.ройства, третий выход третьего блока Источники информациипамяти соединен с информационным вхо- принятые во внимание при экспертизедом второго счетчика адреса, управля 1. Авторское свидетельство СССРющий вход которого подключен к выхо- У 705457, кл, С 06 Р 9/22, 1979,ду восьмого элемента И, а выход - к 2. Авторское свидетельство СССРвходу четвертого дешифратора, выход по заявке Ю 2802977/18-24,первого элемента НЕ подключен через кл. 6 06 Г 9/22, 1979 прототип).

СмотретьЗаявка

3211181, 13.10.1980

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ПЛАХТЕЕВ АНАТОЛИЙ ПАВЛОВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 15.06.1982

Код ссылки

<a href="https://patents.su/7-935960-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Устройство для управления доступом к магистрали

Случайный патент: Механизм для смены шпуль к пестроткацкому станку