Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

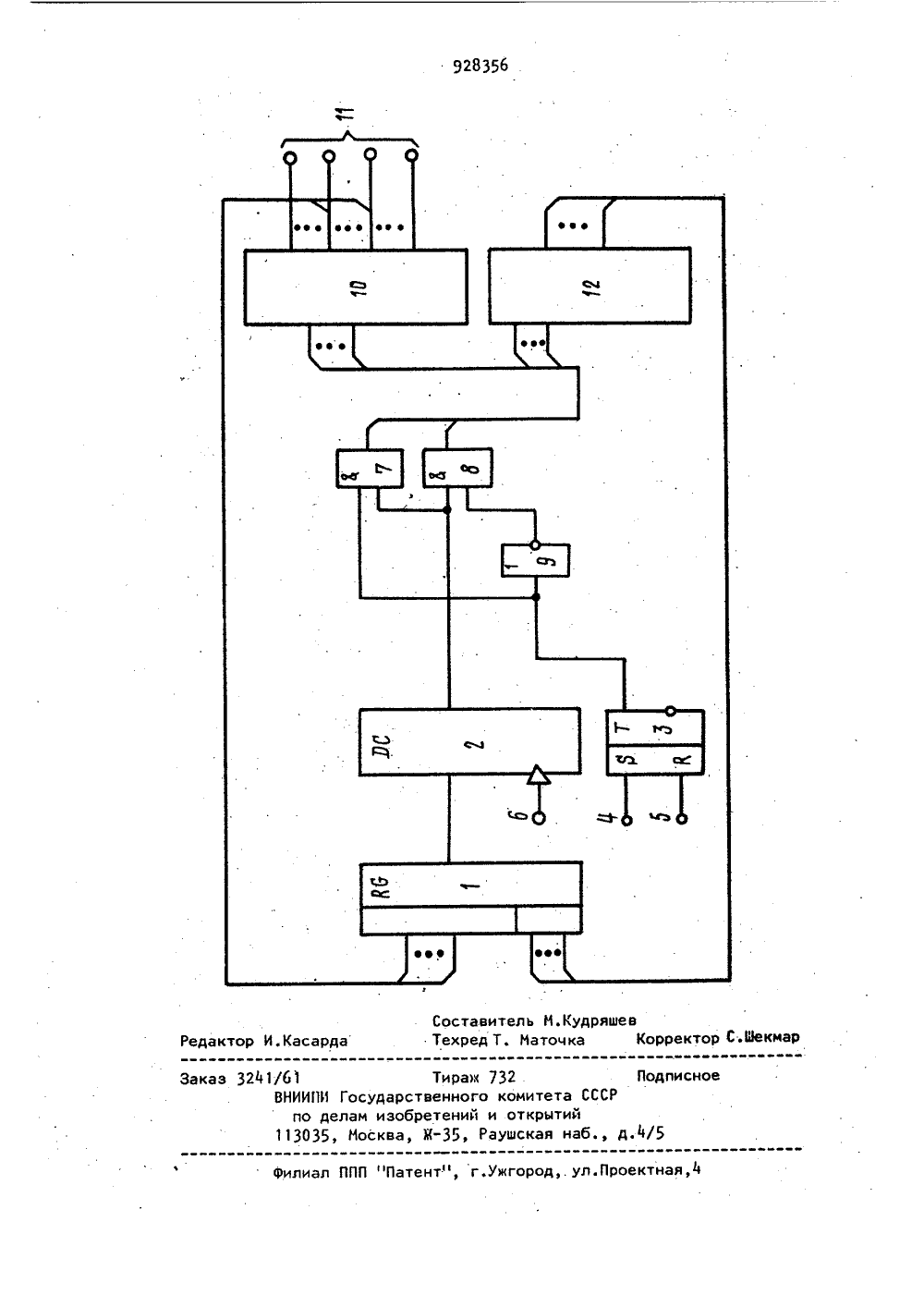

ОП ИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскикСоциалистическихРеспублик 1 928356(6 ) Дополнительное к авт, свид-ву(22) Заявлено 04.07,80 (21) 2950662/18-24с присоединением заявки РЙ. (51)М. Кл. С 06 Р 9/22 Ркударетваааый камктет СССР ае делам лзобретенкй н аткрытайДата опубликования описания 15.05.82(71) Заявитель щи фф й 1 и з 1Щ 4 ПжшмИзобретение относится к вычислительной технике и может быть исполь" зовано при разработке микропрограммных устройств управления ЭВИ.Известно микропрограммное устройство управления, содержащее регистр адреса, блок памяти и дешифратор 11,Недостатком этого устройства является низкая экономичность, обусловленная избыточностью формата микро команд.Наиболее близким к предлагаемому является устройство, содержащее последовательно соединенные узел ветвления, блок памяти, регистр адреса и дешифратор, триггер ЮНедостатком этого устройства является низкая экономичность, которая обусловлена избыточностью, хранимой в блоках памяти адресной информации.Цель изобретения - сокращение объема оборудования.Поставленная цель достигается тем, что в микропрограммном устрой 2стве управления, содержащем два бло" ка памяти, дешифратор, регистр адреса, триггер, элемент НЕ и два блока элементов И, причем выход регистра адреса соединен с первым входом дешифратора, второй вход которого соединен с тактовым входом устройства, единичный вход триггера соединен с входом логического условия устройства, выход триггера соединен с пер" вым входом первого блока элементов И и яерез элемент НЕ - с первым входом второго блока элементов И, группы адресных входов первого и вто. рого блоков памяти соединены с груп" пами выходов первого и второго блоков элементов И, нулевой вход триг" гера соединен с входом сброса устройства, вторые входы первого и второго блока элементов И соединены с выходом дешифратора, первая и вторая группы выходов первого блока памяти являются группой информационных выходов устройства, первая группа выхо928356 3дов первого блока памяти соединена с первой группой информационных входов регистра адреса, вторая груп" пэ входов которого соединена с группой выходов второго блока памяти юНа чертеже приведена структурная схема устройства.Устройство содержит регистр 1 ад" реса, дешифратор 2, триггер 3, вход 4 логических условий устройства, 1 з вход 5 сброса устройства, тактовый вход 6 устройства, блоки элементов И 7 и 8, элемент ЙЕ 9, блок 10 памя" ти, группу 1 1 информационных выходов устройства, блок 12 памяти. зБлок 10 предназначен для хранейия операционных частей микрокоманд.Блок 12 предназначен для хране" ния дополнительных кодов, используемых для идентификации адреса очеред ной микрокоманды.Устройство работает следующим образом.По адресу, записанному в регистре 1, и синхроимпульсам, поступающим На 25 вход 5, дешифратор 2 возбуждает, один из своих выходов. Блоки 7 и 8 в зависимости от значения логического условия с входа 4 формируют сигнал на.одном из своих выходов. По этому зо сигналу из блока 10 памяти считывается код микроопераций, который поступает на выход в группу 11. Адресная часть, кода из блока 10 совместно с дополнительным кодом,считываемым из блока 12 памяти по тому же адресу, образ,уют код адреса следующей микро" команды. Этот адрес заносится в ре-: гистр 1.Применение предлагаемого устройст о ва позволяет сократить объем блоков памяти за счеФ сокращения объема ад" ресной информации. формула изобретенияМикропрограммное устройство управления, содержащее два блока памяти, дешифратор, регистр адреса, триггер, элемент НЕ и два блока элемен" тов И, причем выход регистра адреса соединен с первым входом дешифратора, второй вход которого соединен с тактовым входом устройства, единичный вход триггера соединен с входом логического условия устройства, выход триггера соединен с первым входом первого блока элементов И и через элемент НЕ " с первым входом второго блока элементов И, группы адрес" ных входов первого и второго блоков . памяти соединены с группами выходов первого и второго блоков элементов И, о т л и ч а 0 щ е е с я тем, что, ,с целью сокращения объема оборудова" ния, нулевой вход триггера соединен с входом сброса устройства, вторые входы первого и второго блока элемен" тов И соединены с выходом дешифратора, первая и вторая группы выходов первого блока памяти являются группой информационных выходов устройства, первая группа выходов первого блока памяти соединена с первой группой информационных входов регистра адреса, вторая группа входов которого соединена с группой выходов второго блока памяти. Источники информации,принятые во внимание при экспертизе 1. Авторское свидетельство ССССР У 156271, кл. С 06 Г 9/22 1975928356 оставитель И.Кудряехред Т. Иаточка Шекм актор И.Ка оррек а аказ 3241/61 Тираж 732ИПИ Государственного комитета ССо делам изобретений и открытий035, Иосква, И, Раушская наб. Подпис

СмотретьЗаявка

2950662, 04.07.1980

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 15.05.1982

Код ссылки

<a href="https://patents.su/3-928356-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Устройство микропрограммного управления

Случайный патент: Аэрожелоб для выгрузки зерна