Устройство микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

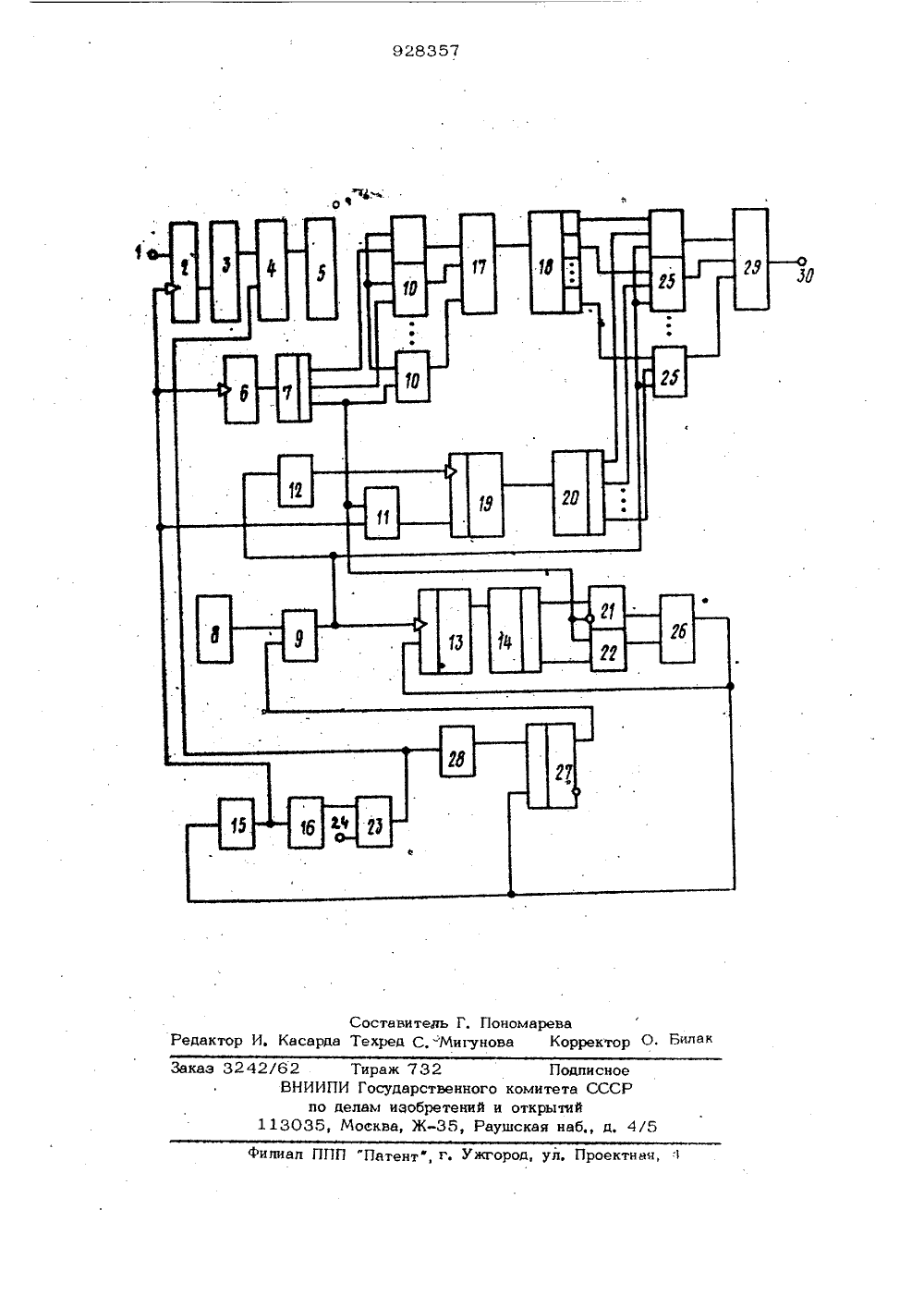

Союз СоветскикСоцианистическмаРеспубики ТЕЛЬСТ 8 К АВТОРСКОМ(23) Приоритет оеударствееыЯ квинт юллетень М етеквЯ делан ОпубликованДата опубл(54) УСТРОЙС ике ыть ств го счетчика череинеи с первым пока, выходысоединены с пер-,вующих блоков н ходами второго дешорого подкпючен к вь фратора, вход кооду второго счет- соединен с перемента И 23.устройства явля- ость запоминаюшечика, выход генератора вым входом первого эпНедостатком данног тся низкая экономич я тем, что в ячейго блока, обусповпенна ке запоминаюшего бпо ся только целое чиспо Цепь изобретения -номичности устройства Поставленная цель что устройство микрон равнения допопнитепьнани а можетмикрокома овышение стигается тем рограммного упо содержит вторую Изобретение относится к автомат и вычиспитепьной технике и может б применено при проектировании устрой управления микропрограммных ЭВМ,Известно устройство микропрограммого управления, содержащее запоминающий блок, регистр, дешифратор, погические элементы 13.Недостатком этого устройства является низкая экономичность, обусповпеннаят тем, что дпя хранения микрокоманд используется только часть разрядов каждой ячейки запоминающего бпока.Наиболее близким по технической сущности и достигаемому эффекту к предпагаемому является устройство микропрограммного управления, содержащее запоми. нающий бпок (ЗБ), два счетчика, два дешифратора, регистр микрокоманд, генератор импульсов, группу из (К+1) (где К - число микрокоманд, помешавшихся в формате ЗБ цепиком) блоков эпементов И, бпок элементов ИЛИ, первый эпемент И, причем установочный вход первоРОПРОГРАММНОГО УПРАВЛЕ го счетчика является первым входом устройства, а выход перво первый дешифратор соед входом запоминающего регистра микрокоманд выми входами соответс лементов И первой группы, выходы котоых через первый блок элементов ИЛИодкпючены к выходу устройства, а втоые входы соединены соответственно с3 92835 группу из т (рч- чисно ячеек ЗБ) блоков элементов И, второй бпок эпементов ИЛИ, третий и четвертый счетчики, третий и четвертый дешифраторы, три эпемента задержки, второй - четвертый эпе 5 менты И, два элемента ИЛИтриггер, дифференцируюшую цепочку, буферный регистр, причем выход буферного регистра соединен с первыми входами блоков эпементов И второй группы, вторые. входы которых соединены с соответствующими выходами третьего дешифратора, а выходы соединены со входами второго бпока элементов ИЛИ, выход которого подкшочен ко входу регистра микрокоманд, т-ый выход третьего дешифратора подключен к первым входам второго, третьего и инверсному входу четвертого элемента И, выходы третьего и четвертого эпементов И через первый элемент ИЛИ и дифферен20 цируюшую цепочку подкпючены ко второму входу второго эпемента И, к входу первого элемента задержки, к счетным входам первого и третьего счетчиков, выход третьего счетчика подкцюченко входу тре 25 тьего дешифратора, выход второго эпемента И соединен с установочным вхо- дом второго счетчика, счетный вход кото- . рого через второй эпемент задержки соединен с выходами первого эпемента И,третьими входами блоков эпементов И36 первой группы, счетным входом четвертого счетчика, выход которого соединен с входом четвертого дешифратора, К-ый вы-, ход которого соединен с прямым входом четвертого элемента И, а (К+1)-й выход З четвертого дешифратора соединен с вторым входом третьего элемента И, выход первого элемента ИЛИ соединен с нупевым входом триггера и установочным входом четвертого счетчика, выход первоО го эпемента задержки соединен с первым входом второго элемента ИЛИ, выход которого соединен с вторым входом запоминающего блока и через третий элемент задержки - с единичным входом триггера,43 единичный выход которого соединен с вторым входом первого элемента И, а второй вход устройства подключен ко второму входу второго эпемента ИЛИ,вход буферного регистра соединен с вы- Яходом запоминающего бпока. Сущность изобретения состоит в повы-. шении экономичности устройства за счет использования ячеек запоминающего блока,с макснмапьной эффективностью дпя полезной информации путем организации считывания дробного числа микрокоманд,7 фсодержащихся в ячейках запоминающегоблока.На чертеже приведена функционапьнаясхема устройства дпя случая, когда оставшаяся незаполненной часть форматаячейки запоминающего блока дщ позво 1пяет разместить в ней не бопьше поповииы микрокоманды.Устройство содержит первый вход 1устройства, первый счетчик 2, первый дешифратор Э,запоминающий блок 4, буферферный регистр 5, третий счетчик б,третий дешифратор 7, генератор 8 первыйэлемент И 9, вторую группу блоков эпементов И ( - 1,п) 10, второй элементИ 11, элемент 12 задержки, четвертыйсчетчик 13, четвертый дешифратор 14,дифференцирующую цепочку 15, первыйэлемент 16 задержки,второй блок элементов ИЛИ 17 регистр 18 микрокоманд,второй счетчик 1 9, второй дешифраторО, четвертый элемент И 21, третийэпемент И 22, второй элемент ИЛИ 23,второй вход 24 устройства, первую группу блоков элементов И- 1, К+1) 25,первый элемент ИЛИ 26, К 5-триггер27, третий элемент 28 задержки, первыйблок элементов ИЛИ 29, выход 30 устройства,Устройство работает следующим образом,По команде "Пуск", поступающей на"вход 24, разрешается считывание информации иэ бпока 4 в регистр 5, котораяпоступает дапее через блок эпементовИ 10 второй группы и блок ИЛИ 17в регистр 18. Через время, равное времени считывания информации и опредепяемое элементом 28 задержки, триггер27 устанавливается в единичное состояние и импульсы от генератора 8 поступают в счетчик 13, а затем - в счетчик19, В результате поочередно возбуждаются первый К-ый выход дешифратора 20и микрокоманды А, , Ас полей регистра 18 через бпоки элементов И 25поступают на блок элементов ИЛИ 29 идалее - на выход 30 устройства,После прихода К-того импупьса появпяется сигнал на выходе элемента И 21,цо которому обнуляется счетчик 13 итриггер 27, блокируя элемент И 9, асчетчик 1 9 устанавливается в состояние,которому соответствует единичный сигнал на (К+1)-м выходе.дешифратора 20,Одновременно импульс сформированныйдкфференцируюшей цепочкой 15; увепичивает содержанке счетчиков 2 и 6 на единицу, Затем осуществпяется считывание5 9283 информации из ячейки блока 4 в регистр 5, Микрокоманда из регистра 5 через блок элементов И 10 второй группы и блок эпементов ИЛИ 17 поступает в ре- гистр 18. Причем остаток (К+1)-й микрокоманды А поступает в (К+1) - поле регистра 18, где хранится ее первая часть А 1, 1 После установки в единицу триггера 27 импульс от генератора 8 разрешает выдачу микрокоманды А 1= 1 о-А Ачерез блок элементовИ 25 открйтый единичным потенциалом с (К+1)-го выхода дешифратора 20.Затем этим импульсом, проходящим через элемент 12 задержки, счетчик 19 15 устанавливается в состояние, которомусоответствует единичный сигнаи, на перМм выходе дешифраторв 20 и с первого ыопя регистра 18 через бпок элементовИ.25 и бпок энементов ИЛИ 29 на выход 30 устройства поступает микро комвнда. Далее устройство работает аналогично и поспедоватепьно выдает микрокомвнды А , А 1 , А, После выдачи .микрокомвщы Ащ на к-том выходе дешифратора 14 вновь появляется единичный сигнви, который,. проходя через элементы И 21, ИЛИ 26, обнупяет триггер27 и счетчйк.13,"Затем иэ блока 4 считывается информация, хранимая в очередной ячейке, микрокоманды поступают нв выход устройства, начиная с К-того поля регистра 1835После считывания иэ п 1 -ой ячейки информация, которая дроходит через блокэлементов И 10 в регистре 18 записано К+1 полная микрокомандв. Организациясчитывания этих микрокомвнд из регистра 18 в данном цикле осуществпяетсяаналогично, Отличие состоит в том, чтопосле установки счетчика 13 в состояние,которому соответствует единица на К-омвыходе дешифратора 14, элемент И 21остается закрытым, поскольку на п -омвыходе дешифрвтора 7 установлен единичный сигнал, Поэтому очередным импульсом счетчик 13 переводится в (К+1)-есостояние а с 1 -го поля регистра 18Э50через бпок эпементов И 25 выдается микрокоманда. Затем элемент И 22 формирует единичный сигнал, по которому обнупяется счетчик 13, триггер 27, а черезоткрытый элемент И 11 - счетчик 19,Затем из блока 4 считывается очеред 55нвя информвцйя, которая записывается врегистр 18 через блок эпементов И 10.Дапее устройство работает анапогично. 57 6Предлагаемое устройство существеннопревосходит известное, по экономичности,Применение его поэвопяет строить бопееэкономичные микропрограммы системыза счет уменьшения ассортимента запоминающих блоков и повышения коэффициентаих использования,формула изобретенияУстройство микропрограммного управпения, содержащее запоминающий блок, два счетчика, два дещифратора, регистр микрокоманд, генератор импульсов, группу иэ (К+1) (где К - число микрокоманд, помещающихся в формате запоминающего блоке целиком) блоков эпементов И,блок элементов ИЛИ, первый элемент И, причем установочный вход первого счетчика является первым входом устройства, а выход первого счетчика через первый дешифратор соединен с первым входом запоминающего блока, выходы, регистра микрокоманд соединены с первыми входами соответствующих блоков элементов И первой группы, выходы которых через первый блок элементов ИЛИ подкпючены к выходу устройства, а вторые входы соединены соответственно с выходами второго дешифрвтора, вход которого подкпючен к выходу счетчика, выход генератора сое- динен с первым входом первого элемен та И, о т л и ч а ю ш е е с я тем, что, с целью повышения экономичности, устройство дополнительно содержит вторую группу иэ дз (гп- чиспо ячеек ЗБ) бпоков эпементов И, второй блок элементов ИЛИ, третий и четвертый счетчики, третий и четвертый дещифрвторы, три элемента задержки, второй - четвертый эпе- менты И, два элемента ИЛИ, триггер, дифференцируюшую цепочку, буферный ре- .гистр, причем выход буферного регистра соединен с первыми входами блоков элементов И второй группы, вторые входы которых соединены с соответствующими выходами третьего дещифрвтора, выходы соединены со входами второго блока элементов ИЛИ, выход которого подкпючеы ко входу регистра микрокомвнд, е -ый выход третьего дешифратора подключен к первым входам второго, третьего и инверсному входу четвертого элемента И выходы третьего и четвертого элементов И через первый элемент ИЛИ и дифференцируюшую цепочку подключены ко второму входу второго элемента И, к входу первого элемента задержки, к счет ным входам первого и третьего счетчиков, выход третьего счетчика подкшоченко входу третьего дешифратора, выходвторого элемента И соединен с установочным входом второго счетчика, счетный 5вход которого через второй элемент задержки соединен с выходом первого элемента И, третьими .входами блоков элементов И первой группы, счетным входомчетвертого счетчика, выход которого сое- одинен с входом четвертого дешифратора,К-ый выход которого соединен с прямымвходом четвертого элемента И, а (К+1 )-й .выход четвертого дешифратора соединенс вторым входом третьего элемента И, 5выход первого элемента ИЛИ соединен снулевым входом триггера и установочнымвходом четвертого счетчика, выход первого элемента задержки соединен с пер 357 8вым входом второго элемента ИЛИ, выход которого соединен с вторым входом запоминающего блока и через третий элемент задержки - с единичным входом триггера, единичный выход которого соединен с вторым входом первого элемента И, а второй вход устройства подключен ко второму входу второго элемента ИЛИ, вход буферного регистра соединен с выходом запоминаюшего блока. Источники информации,принятые во внимание при экспертизе 1. Авторское свидетельство СССР Ж 487490, кл. С 06 Р 9/16, 1975. 2. Геолецян А. Г, ЭВМ "Наири". Программирование и микропрограммирование, М., "Статистика", 1979, с. 13,рис. 15 (прототип).

СмотретьЗаявка

2961311, 23.07.1980

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, РОЗАНОВ АНДРЕЙ ДМИТРИЕВИЧ, ЧЕПЕЛЬ СЕРГЕЙ ВАЛЕНТИНОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммного

Опубликовано: 15.05.1982

Код ссылки

<a href="https://patents.su/5-928357-ustrojjstvo-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Устройство для формирования адресов памяти

Случайный патент: 190766