Преобразователь двоично-десятичных чисел в коде 4, 2, 2, 1 в двоичные

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

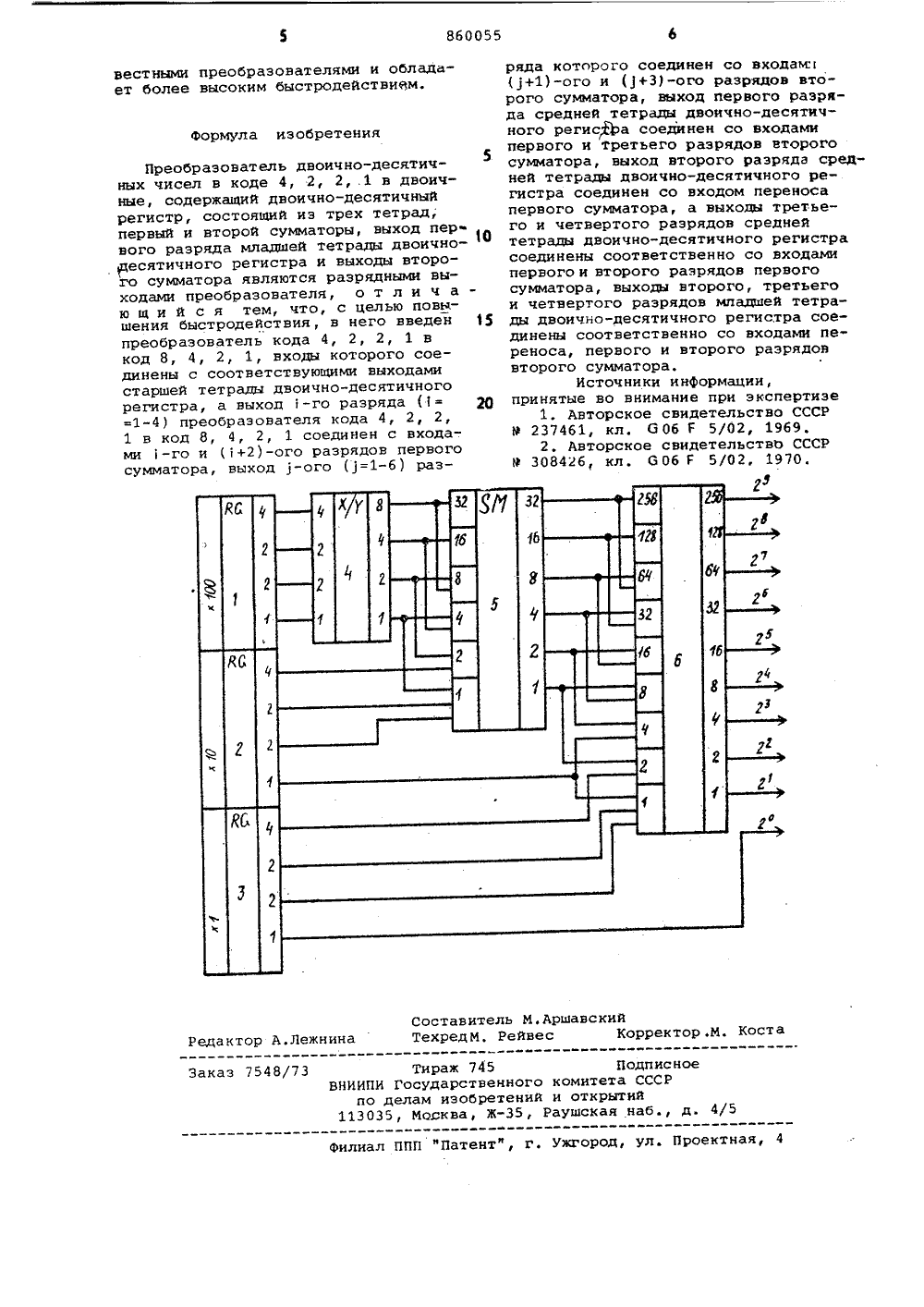

Союз Севетскик Социалистических Республик(22) Заявлено 1010.79 (21) 2828291/18-24с присоединением заявки Нов(5)М. Кл.з С 06 Г 5/02 Государственный комитет СССР оо дедам изобретений и открытий(54) 1 РЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ В КОДЕ 4,2,2,1 В ДВОИЧНЫЕ Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении двоично-десятичных преобразователей.Известен преобразователь двоичнодесятичных чисел в двоичные, содержащий двоично-десятичный регистр, элементы И и ИЛИ, сумматоры, выходы которых соединены со входами двоична-десятичного регистра И .Недостаток известного преобразователя 6 остоит в низком быстродействии. Наиболее близким к предлагаемому по технической сущности и схемному .15 решению является преобразователь двоично-десятнчных чисел в коде "4, 2, 2, 1" в двоичные, содержащий двоичнодесятичный регистр, состоящий из трех тетрад, первый и второй сумматоры, 20 выход первого разряда младшей тетрады двоично-десятичного регистра н выходы второго сумматора являются разрядными выходами преобразователя 2 .Недостаток этого преобразователя также состоит в низкой скорости преобразования, связанной с большим числом циклов сдвига, суммирования и перезаписи преобразуемого числа в двоично-десятичный регистр. 30 Цель изобретения - увеличение скорости преобразования.Поставленная цель достигается тем, что в преобразователь двоично-десятичных чисел в коде "4, 2, 2, 1" в двоичные, содержащий двоично-десятичный регистр, состоящий иэ трех тетрад, первый а второй сумматоры, выход первого разряда младшей тетрады двоично-десятичного регистра и выходы второго сумматора являются разрядными выходами 1 преобразователя, введен преобразователь кода "4, 2, 2, 1 ф в код "8, 4, 2, 1 ф, входы которого соединены с соответствующими выходами старшей тетрады двоично-десятичного регистра, а выход 1-го разряда (1 в 1-4 ) преобразователя кода и 4, 2, 2, 1 ф в код "8, 4, 2, 1" соединен с входами 1-го и (+2)-ого разрядов первого суьиатора, выход )-ого 1-б) разряда которогО соединен со входамн +1)-го и (+ +3)-ого разрядов второго сумматора, выход первого разряда средней тетрады двоично-десятичного регистра соединен со входаии первого н третьего разрядов второго сумматора, выход второго разряда средней тетрады двоично-десятичного регистра соединен со входом переноса первого сумматора, а выходытретьего и четвертого разрядов средней тетрады двоично-десятичного регистра соединены соответственно со входами первого и второго разрядов первого сумматора, выходы второго, третьего и четвертого разрядов младшей тетрады двоично-десятичного регистра соединены соответственно со входами переноса, первого и второго разрядов второго сумматора.На чертеже изображена функциональ 10ная схема предлагаемого преобразователя.Схема содержит тетрады 1-3 входного двоично-десятичного регистра, преобразователь 4 кода "4, 2, 2, 1" в 15код "8, 4, 2, 1", сумматоры 5 и 6.Разряды двоично-десятичного числапредставлены в коде "4, 2, 2, 1",Выходы разрядов тетрады 1 подключены на входы преобразователя 4 кода, 20выходы которого подключены ко входамсумматОра 5, имеющим тот же нес, атакже ко входам со сдвигом на дваразряда в сторону старших разрядов,Выходы разрядов с весами "2", "2","4" тетрады 2 подключены ко нходаммладших раэрядон сумматора 5, выходс весом "4" - ко входу с весом "2",выходы с весами "2" - ко входу с весом "1". Выходы сумматора 5 подключе -ны ко входам сумматора б, имеющимудвоенный вес, а также со сдвигом ковходам, имеющим восьмикратный вес.Выху тетрады 2 с весом "1" подключенко входам Оумматора б с весом "1", авыходы тетрады 3 с весами "2" подклю- З 5чены ко входам сумматора б с весом"1". Выход тетрады 3 с весом "4" подключен ко входу сумматора б с весом"2". Выходы сумматора б и выход с весом "1" тетрады 3 являются выходами 40устройства,Устройство работает следующим образом.На преобразователь 4 поступает цифра старшего десятичного разряда преобразуемого числа в коде "4, 2, 2, 1".На выходы преобразователя 4 цифрастаршего десятичного разряда преобразуемого числа поступает в коде "8,4, 2, 1". Этот код поступает на входыра 5 с весами 8 ц 4 д д"1" и со сдвигом на два разряда н сто.рону старших разрядов на входы с весами "32", "16", "8", "4", т.е. значение цифры старшего разряда суммируется с этим значением, умноженнымна четыре.Таким образом, значение цифрой старшего разряда преобразуемого числа умно-жается на сумматоре 5 на пять, Наразряды сумматора 5 с весом "2" и "1" Оподключены также выходы разрядов тетрады 2 с весами "4", "2", "2" так,что на сумматор 5 поступает значениецифры второго десятичного разрядаисходного числа, деленное на дна. Код на выходах сумматора 5 представляет сумму цифры старшего разряда исходного числа, умноженной на пять, с половиной цифры следующего десятичного разряда. Выходам разрядов сумматора 5 "присваивается" удвоенный вес т.е. выход с весом "321 считаешься имеющим нес "64", выход с весом "16" - имеющим вес 32 и т.д.) . В этом случае код на выходах сумматора представляет собой сумму цифры старшего разряда, умноженной на десять, со значением цифры следующего десятичного разряда исходного числа. Код с выходов сумматора 5 с учетом присвоенных весов поступает на нходы сумматора 6, имеющие те же веса ("64", "32" и т.д.), а также со сдвигом на два разряда в сторону старших разрядов на входы с весами "256", "128" и т.д., т.е. значение кода суммируется со своим значением, умноженным на четыре. Таким образом значение кода умножается на сумматоре б на пять. На разряды сумматора б с весами "2" и "1" подключены также выходы разрядон тетрады 3 с весами "4", "2", "2", т.е. на сумматор б поступает значение цифры третьего десятичного разряда исходного числа, деленное на два, Коду на выходах сумматора б также "присвоен" удвоенный нес, т.е, он представляет сумму кода, поступающего с сумматора 5, умноженного на десять, и ко - да цифры третьего разряда исходного числа. Таким образом устройство реализует алгоритм преобразования двоичко-десятичного числа в двоичное, После записи исходного числа и регистр 3 через нремя, необходимое для срабатывания преобразователя 4 и сумматоров, на выходах сумматора б фиксируется двоичный код преобразуемого числа,В случае, если исходное число представлено в коде "8, 4, 2, 1", необходимо исключить из устройства преобразователь кода "4, 2, 2, 1" н код "8, 4, 2, 1" старшего разряда и внести преобразователи кода "8, 4, 2, 1" н код "4, 2, 2, 1" н остальных разрядах, при этом выходы разрядов тетрады 1 подключаются непосредственно на входы последних, выходы которых подключаются на входы сумматоров 5 и б аналогично, Быстродействие устройства при этом не меняется.По сравнению с известными устройствами, работающими по методу сдви - га, суммирования и перезаписи кода преобразуемого числа в регистр или устройствами преобразования методом поразрядного сдвига кода каждой тетрады и суммиронания на последовательных сумматорах, предлагаемое устройство является существенно более быстродействующим.Использование предлагаемого устройства позволяет уменьшить число каскадон сумматоров по сраннению с из860055 формула изобретения Преобразователь двоично-десятич 5 ных чисел в коде 4, 2, 2, .1 в двоичные, содержащий двоично-десятичный регистр, состоящий иэ трех тетрад, первый и второй сумматоры, выход первого разряда младшей тетрады двоично- (О десятичного регистра и выходы второго сумматора являются разрядными выходами преобразователя, о т л и ч аю щ и й с я тем, что, с целью понишения быстродействия, в него введен 15 преобразователь кода 4, 2, 2, 1 в код 8, 4, 2, 1, входы которого соединены с соответствующими выходами старшей тетрады дноично-десятичного регистра, а ныход 1-го разряда (1 2 О =1-4) преобраэонателя кода 4, 2, 2, 1 н код 8, 4, 2, 1 соединен с входами )-го и (+2)-ого разрядов первого сумматора, выход -ого =1-6) разь М.Аршанскийейнес Корректор .М. Коста Составит Техред М. актор А и Заказ 7548/7 Тираж 745ПИ Государственноо делам изобретен035, Москва, ЖПодп ис ноеитета СССРткрытийская наб., д. 4 ВН и Раилиал ППП "Патент", г. Ужгород, ул. Проектная,вестными преобразователями и обладает более высоким быстродействием. ряда которого соединен со входаьс (+1)-ого и +3)-ого разрядов второго сумматора, выход первого разряда средней тетрады двоично-десятичного регистра соединен со входами перного и третьего разрядов второго сумматора, выход второго разряда средней тетрады двоично-десятичного регистра соединен со входом переноса первого сумматора, а выходы третьего и четвертого разрядов средней тетрады двоично-десятичного регистра соединены соответственно со входами первого и второго разрядов первого сумматора, выходя нторого, третьего и четвертого разрядов младшей тетрады двоично-десятичного регистра соединены соответственно со входами переноса, первого и второго разрядов второго сумматора.Источники информации, принятые но внимание при экспертизе1. Авторское свидетельство СССР Р 237461, кл. 6 06 Г 5/02, 1969.2. Авторское свидетельствЬ СССР У 308426, кл, 6 06 Г 5/02, 1970.

СмотретьЗаявка

2828291, 10.10.1979

ПРЕДПРИЯТИЕ ПЯ Х-5827

СТЕПАНОВ АНАТОЛИЙ ВАЛЕНТИНОВИЧ, СМИРНОВ НИКОЛАЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 5/02

Метки: двоично-десятичных, двоичные, коде, чисел

Опубликовано: 30.08.1981

Код ссылки

<a href="https://patents.su/3-860055-preobrazovatel-dvoichno-desyatichnykh-chisel-v-kode-4-2-2-1-v-dvoichnye.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь двоично-десятичных чисел в коде 4, 2, 2, 1 в двоичные</a>