Способ обнаружения и исправленияошибок b запоминающем устройстве спомощью корректирующих кодов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

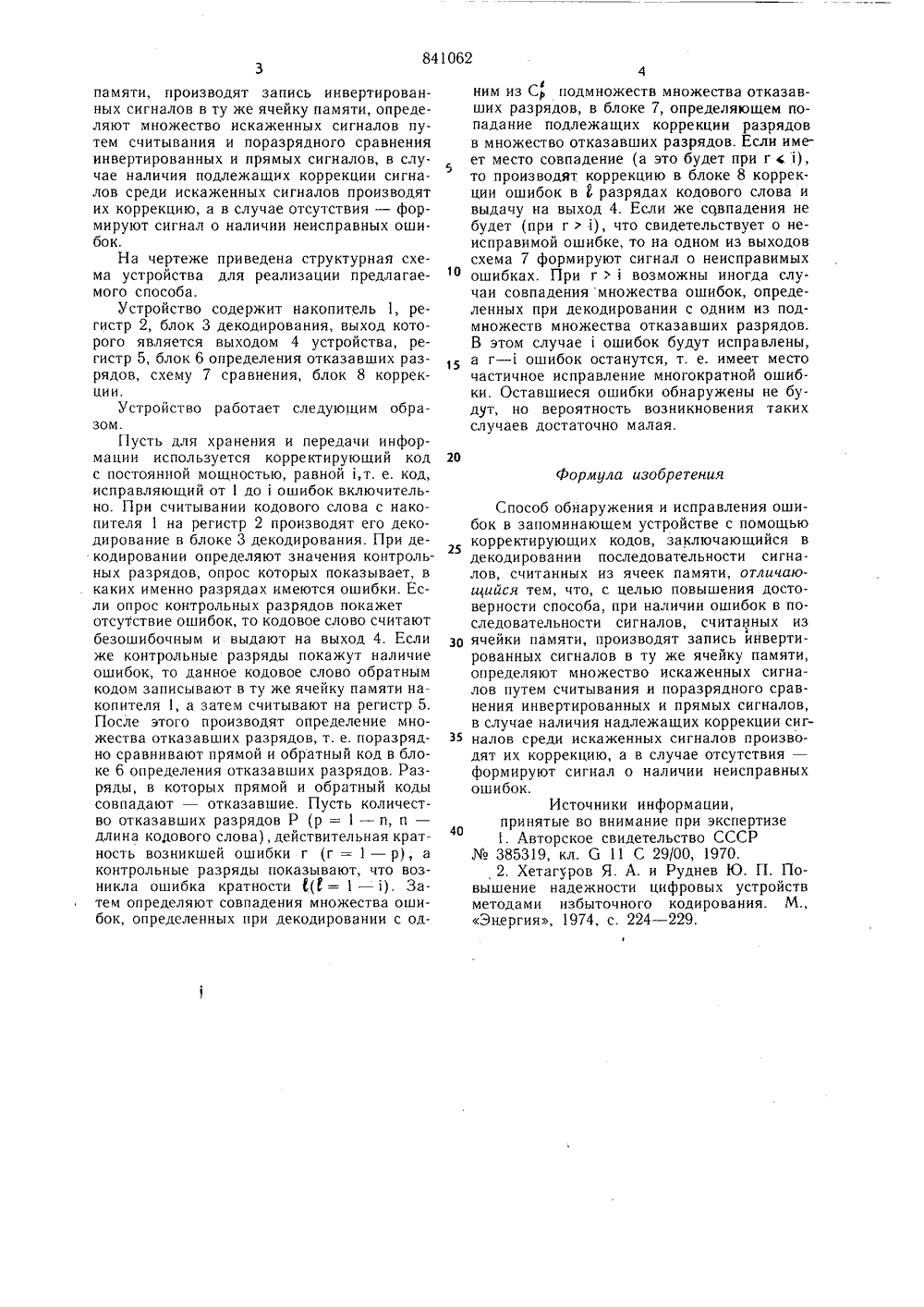

Союз Советски кСоциапистическикРеспублик ОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ.(51) М. Кл з б 11 С 29/00 Гаеударствеиамй квмитат СССР по делам изобретений и аткрытий72) Авторы изобретени И. А. Дичка, Н В. И. Корнейчу уравскии, А. Г. ЗабураН. Орлова и В. Я. Юрч Киевский ордена Ленина политехническ м. 50-летия Великой Октябрьской социареволюции институт стической(54) СПОСОБ ОБНАРУЖЕНИЯ И ИСПРАВЛЕНИЯОШИБОК В ЗАПОМИНАЮЩЕМ УСТРОЙСТВЕ С ПОМОЩЬ КОРРЕКТИРУЮЩИХ КОДОВ- повышение достоулучшения обнаружиорректирующего кода корректирующей споНаиб ем к пр ружения щи корр с которы довое сл чения к рольные ошибки,Изобретение относится к запоминающим устройствам.Известен способ обнаружения и исправления ошибок в запоминающем устройстве, согласно которому производится запись и считывание прямых и обратных кодов в запоминающее устройство с последующим поразрядным сравнением, что позволяет обнаружить, а в некоторых случаях и исправить ошибки, вызванные отказами любой кратности 1.Недостаток способа - ограниченность корректирующих возможностей, так как в случае совпадения отказа и направления записываемой информации исправление ошибки невозможно. олее близким техническим решенидлагаемому является способ обнаи исправления ошибок при помоектирующих кодов в соответствии м при считывании информации коово декодируют, т. е. определяют знантрольных разрядов, и если конт- разряды показывают отсутствие то данное слово поступает на выход,а в случае наличия ошибок в . производят их исправление и выдачу кода 2.Недостатком этого способа является то,что при возникновении ошибок большой кратности, превышающей мощность корректирующего кода, они исправляют неверно (что снижает достоверность контроля), а для их обнаружения требуется увеличить количество контрольных разрядов, что влечет увеличение аппаратурных затрат на кодирование, декодирование, коррекцию и, кроме того, усложняется алгоритм образования контрольных разрядов.Цель изобретенияверности способа завающей способности кпри его неизменной5 собности.Поставленная цель достигается тем, чтопри использовании способа обнаружения и исправления ошибок в запоминающем устройстве с помощью корректирующих кодов, заключающегося в декодировании последоЗт вательности сигналов, считанных из ячеекпамяти, при наличии ошибок в последовательности сигналов, считанных из ячейкипамяти, производят запись инвертированных сигналов в ту же ячейку памяти, определяют множество искаженных сигналов путем считывания и поразрядного сравнения инвертированных и прямых сигналов, в случае наличия подлежащих коррекции сигналов среди искаженных сигналов производят их коррекцию, а в случае отсутствия - формируют сигнал о наличии неисправных ошибок.На чертеже приведена структурная схема устройства для реализации предлагаемого способа.Устройство содержит накопитель 1, регистр 2, блок 3 декодирования, выход которого является выходом 4 устройства, регистр 5, блок 6 определения отказавших разрядов, схему 7 сравнения, блок 8 коррекции.Устройство работает следуюгцим образом.Пусть для хранения и передачи информации используется корректирующий код с постоянной мощностью, равной 1,т. е. код, исправляющий от 1 до 1 ошибок включительно. При считывании кодового слова с накопителя 1 на регистр 2 производят его декодирование в блоке 3 декодирования. При декодировании определяют значения контрольных разрядов, опрос которых показывает, в каких именно разрядах имеются ошибки. Если опрос контрольных разрядов покажет отсутствие ошибок, то кодовое слово считают безошибочным и выдают на выход 4, Если же контрольные разряды покажут наличие ошибок, то данное кодовое слово обратным кодом записывают в ту же ячейку памяти накопителя 1, а затем считывают на регистр 5. После этого производят определение множества отказавших разрядов, т. е. поразрядно сравнивают прямой и обратный код в блоке 6 определения отказавших разрядов. Разряды, в которых прямой и обратный коды совпадают - отказавшие. Пусть количество отказавших разрядов Р (р = 1 - и, и - длина кодового слова), действительная кратность возникшей ошибки г (г = 1 - р), а контрольные разряды показывают, что возникла ошибка кратности 1(1= 1 - 1). Затем определяют совпадения множества ошибок, определенных при декодировании с од 4сним из С подмножеств множества отказавших разрядов, в блоке 7, определяющем попадание подлежащих коррекции разрядов в множество отказавших разрядов. Если имеет место совпадение (а это будет при г с 1), то производят коррекцию в блоке 8 коррекции ошибок в с разрядах кодового слова и выдачу на выход 4. Если же сс 1 впадения не будет (при г ) 1), что свидетельствует о неисправимой ошибке, то на одном из выходов схема 7 формируют сигнал о неисправимых 10 ошибках. При г1 возможны иногда случаи совпадения множества ошибок, определенных при декодировании с одним из подмножеств множества отказавших разрядов.В этом случае 1 ошибок будут исправлены, а г - 1 ошибок останутся, т. е. имеет место частичное исправление многократной ошибки. Оставшиеся ошибки обнаружены не будут, но вероятность возникновения таких случаев достаточно малая.гоФормула изобретенияСпособ обнаружения и исправления ошибок в запоминающем устройстве с помощью г 5корректирующих кодов, заключающийся в декодировании последовательности сигналов, считанных из ячеек памяти, отличаюисийся тем, что, с целью повышения достоверности способа, при наличии ошибок в последовательности сигналов, считанных из ЗО ячейки памяти, производят запись инвертированных сигналов в ту же ячейку памяти, определяют множество искаженных сигналов путем считывания и поразрядного сравнения инвертированных и прямых сигналов, в случае наличия надлежащих коррекции сигЗ 5 налов среди искаженных сигналов производят их коррекцию, а в случае отсутствия - формируют сигнал о наличии неисправных ошибок.Источники информации,40принятые во внимание при экспертизе1. Авторское свидетельство СССРМо 385319, кл. Сс 11 С 29/00, 1970.2, Хетагуров Я. А. и Руднев 1 О. П. Повышение надежности цифровых устройствметодами избыточного кодирования. М.,Энергия, 1974, с. 224 - 229.1Составитель В. Рудаков Редактор В. Еремеева Техред АБойкас Корректор Ю. Макаренко Заказ 478081 Тираж 645 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж - 35, Раушская наб., д. 4/5 филиал ППП Патент, г. Ужгород, ул. Проектная, 4

СмотретьЗаявка

2828265, 08.10.1979

КИЕВСКИЙ ОРДЕНА ЛЕНИНА ПОЛИТЕХНИ-ЧЕСКИЙ ИНСТИТУТ ИМ. 50 ЛЕТИЯ ВЕЛИКОЙОКТЯБРЬСКОЙ СОЦИАЛИСТИЧЕСКОЙ PEBO-ЛЮЦИИ

ДИЧКА ИВАН АНДРЕЕВИЧ, ЖУРАВСКИЙ НИКОЛАЙ НИКОЛАЕВИЧ, ЗАБУРАННЫЙ АНАТОЛИЙ ГРИГОРЬЕВИЧ, КОРНЕЙЧУК ВИКТОР ИВАНОВИЧ, ОРЛОВА МАРИЯ НИКОЛАЕВНА, ЮРЧИШИН ВАСИЛИЙ ЯКОВЛЕВИЧ

МПК / Метки

МПК: G11C 29/00

Метки: запоминающем, исправленияошибок, кодов, корректирующих, обнаружения, спомощью, устройстве

Опубликовано: 23.06.1981

Код ссылки

<a href="https://patents.su/3-841062-sposob-obnaruzheniya-i-ispravleniyaoshibok-b-zapominayushhem-ustrojjstve-spomoshhyu-korrektiruyushhikh-kodov.html" target="_blank" rel="follow" title="База патентов СССР">Способ обнаружения и исправленияошибок b запоминающем устройстве спомощью корректирующих кодов</a>

Предыдущий патент: Устройство для контроля блоковпамяти

Следующий патент: Запоминающее устройство матрич-ного типа c самоконтролем

Случайный патент: Устройство для решения геометрических и комбинаторных задач