Параллельный накапливающий сумматор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 744568

Автор: Концевой

Текст

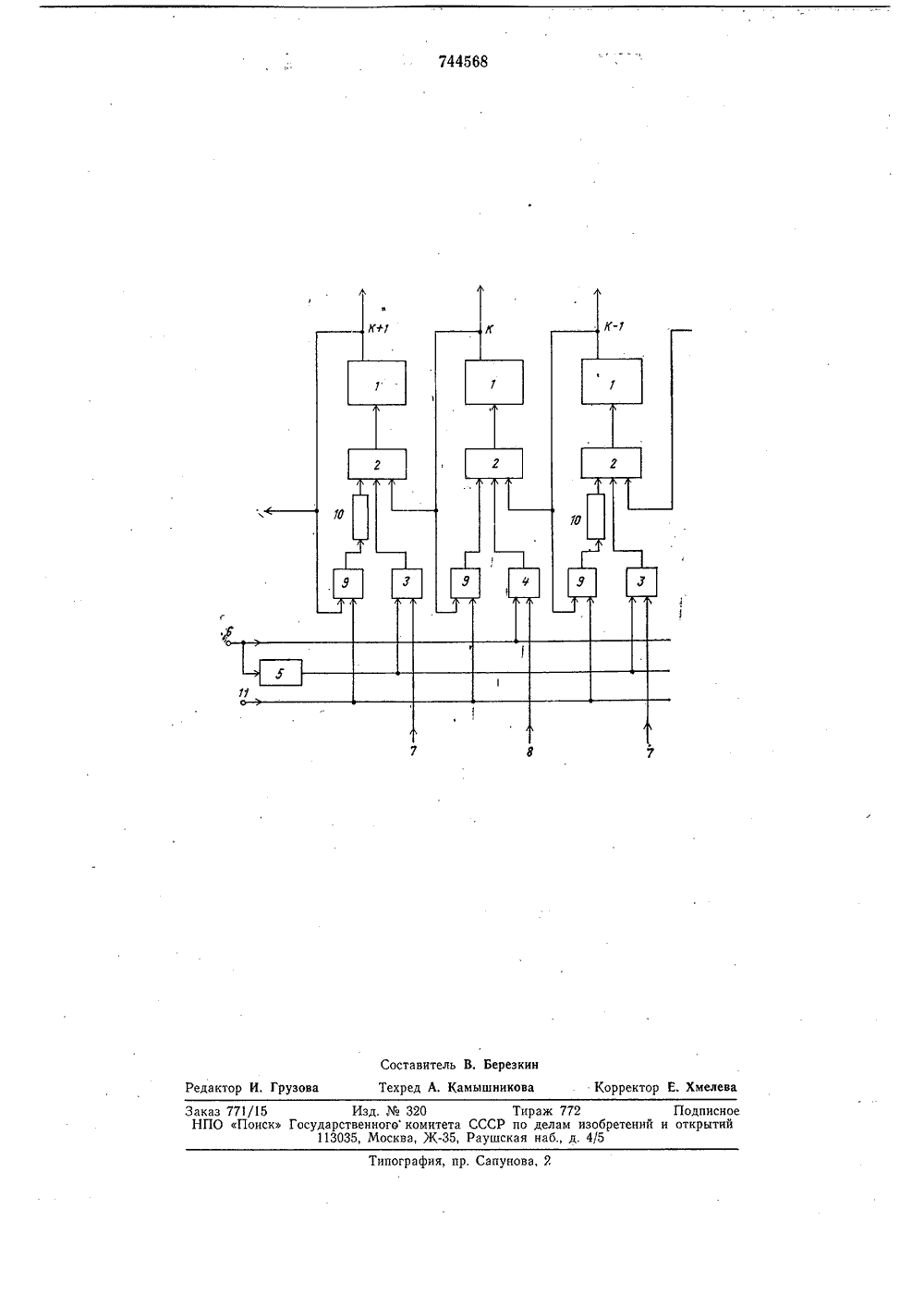

О П И С А НИ.ЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 111) У 44568 Союз Советских Социалистических Республик) Заявлено 26.05,78 (21) 2620726/18-2 с прис инением зая Государстеенный камите(088,8) по делам изобретений и открытий(45) Дата опубликовани исания 30,06,8(54) ПАРАЛЛЕЛЬНЫЙ НАКАПЛИВАЮЩИЙ СУММАТО Изобретение относится к цифровой вычислительной технике, может быть использовано для построения арифметических устройств и является усовершенствованием изобретения по авт. св.581470. 5В основном изобретении по авт. св,581470 описан параллельный накапливающий сумматор, содержащий в каждом разряде триггер, элемент И и элемент ИЛИ, причем первые входы элементов И 10 всех разрядов сумматора подключены к входам разрядов числа, выходы элементов И каждого разряда - к первому входу элементов ИЛИ соответствующего разряда сумматора, выходы которых подсоединены 15 к счетным входам триггеров того же разряда, вторые входы элементов И четных разрядов сумматора подключены к шине управления, а единичный выход триггера каждого разряда сумматора - к второму входу 20 элемента ИЛИ последующего разряда сумматора, кроме того, сумматор содержит элемент задержки, вход которого подключен к шине управления, а выход - к вторым входам элементов И нечетных разрядов сумматора 11.Недостатком такого сумматора является невозможность выполнения операции сдвига. Цель изобретения - расширение функциональных возможностей сумматора, заключающееся в возможности выполнения операции сдвига.Для достижения поставленной цели вкаждый разряд сумматора введен дополнительный элемент И, а в каждый нечетныйразряд сумматора - элемент задержки,причем входы дополнительного элемента Ив каждом разряде сумматора подключены кединичному выходу триггера соответствую- -щего разряда сумматора и к шине управления сдвигом сумматора; выход"дополнитель-"ного элемента И - к третьему входу соответствующего элемента ИЛИ непосредственно - в четных разрядах сумматора ичерез элемент задержки - в нечетных разрядах сумматора,На чертеже представлена функциональная схема трех разрядов К - 1)-го К-го,(К+1) -го) сумматора.Сумматор содержит триггеры 1, элементы ИЛИ 2, элементы И нечетных 3 и четных 4 разрядов сумматора, элемент 5 задержки, шину 6 управления (сложением),входы 7 разрядов числа, служащие для ввода нечетных разрядов слагаемого, которыеподключены к входам элементов И 3, входы8 разрядов числа, служащие для ввода чет5 10 15 20 25 31 35 40 45 50 55 ных разрядов слагаемого, которые подключены к входам элементов И 4. Сумматорсодержит также дополнительные элементыИ 9 и в каждом нечетном разряде сумматора элемент 10 задержки,Другие входы элементов И 3 соединены свыходом элемента 5 задержки, вход которого и другие входы элементов И 4 подключены к шине 6 управления (сложеннем).В каждом разряде сумматора выход элемента ИЛИ 2 подключен к счетному входутриггера 1, выходы которого соединены свходом элемента И 9, другой вход которогоподключен к шине 11 управления сдвигом,В каждом нечетном разряде сумматоравходы элемента ИЛИ 2 соединены с выходом элемента И 3, с выходом триггера 1предыдущего разряда и через элемент 10задержки - с выходом элемента И 9. Вкаждом четном разряде входы элементаИЛИ 2 соединены с выходом элемента И 4,с выходом триггера 1 предыдущего разрядаи с выходом элемента И 9.: -- .:-Рассмотрим работу сумматора, где представлены (К - 1)-й младший нечетный разряд, К-й четный разряд и (К+1)-й - старший нечетный разряд сумматора.Сумматор работает следующим образом.Допустим, что первое слагаемое а равновторому слагаемому О и равно 111. Вводслагаемых осуществляется через элементыИ 3 и 4 после подачи сигнала на шину 6.После введения первого слагаемого в сумматор триггер 1 К-го разряда, а через время, равное 1 задержки элемента 10, триггеры 1 (К - 1)-го и (К+1)-го разрядов перей" дутв единичное состояние и на первых входах элементов И 9 появится разрешающийпотенциал.Короткий сигнал, поступающий на шину11, переведет триггер 1 К-го разряда сумматора в нулевое положение, а сигнал пе" " "реноса с этого триггера через элементИЛИ 2 (К+1)-го разряда переведет триггер 1 этого разряда в состояние нуль ивыдаст сигнал переноса в (К+2)-й разряд.Через время, равное 1 задержки элемента 10(К - 1) -го разряда, сигнал сдвига установит триггер 1 этого разряда в состояниенуль, а сигнал переноса с этого разрядаустановит триггер 1 (К)-го разряда в единичное состояние. Этот же сигнал сдвигачерез время, равное 1 задержки элемента 10(К+1)-го разряда, установит триггер 1 вединичное состояние. После микрооперации сдвига в сумматоре будет записано число; в (К - 1)-м разряде - нуль, в К-м разряде - единица, в (К+ 1)-м разряде - единица и единица переноса в (К+2)-м разряде. После подачи сигнала на шину 6 для введения второго слагаемого в сумматор триггер 1 К-го разряда перейдет в нулевое состояние и сигналом переноса через элемент ИЛИ 2 переведет триггер 1 (К+ 1)-го разряда в нулевое состояние, который в свою очередь выдаст сигнал переноса в (К+2) -й разряд. Через время, равное 1 задержки элементов 10 (К - 1) -го и (К+1) -го разрядов, триггеры 1 этих разрядов перейдут в единичное состояние,Таким образом, данный сумматор кроме суммирования позволяет производить и сдвиг чисел, записанных в сумматоре.Использование изобретения в значительной степени сократит объем оборудования и упростит устройство для умножения двоичных чисел, что позволит получить экономический эффект,При выполнении операции умножение сдвиг частных произведений влево (в сторону старших разрядов) будет производиться непосредственно в накапливающем сумматоре без пересылки частных произведений в сдвиговый регистр. Формула изобретения Параллельный накапливающий сумматор по авт. св.581470, отличающийся тем, что, с целью расширения функциональных возможностей, заключающегося в возможности выполнения операции сдвига, в каждый разряд сумматора введен дополнительный элемент И, а в каждый нечетный разряд сумматора - элемент задержки, причем входы дополнительного элемента И в каждом разряде сумматора подключены к единичному выходу триггера соответствующего разряда сумматора и к шине управления сдвигом сумматора, выход дополнительного элемента И подключен к третьему входу соответствующего элемента ИЛИ непосредственно - в четных разрядах сумматора и через элемент задержки - в нечетных разрядах сумматора.Источники информации,принятые во внимание при экспертизе 1, Авторское свидетельство СССР581470, кл. 6 06 Р 7/50, 1975,744568 7 дактор рректор Е. Хмел узов пр. Сапунова,ипогр Составитель В. Березки Техред А, Камышникова Заказ 771/15 Изд.320 Тираж 772НПО Поиск Государственногокомитета СССР по делам изобретений113035, Москва, Ж, Раушская наб., д. 4/5 Подписи открыти

СмотретьЗаявка

2620726, 26.05.1978

ПРЕДПРИЯТИЕ ПЯ А-1845

КОНЦЕВОЙ ЛЕВ АЛЕКСЕЕВИЧ

МПК / Метки

МПК: G06F 7/50

Метки: накапливающий, параллельный, сумматор

Опубликовано: 30.06.1980

Код ссылки

<a href="https://patents.su/3-744568-parallelnyjj-nakaplivayushhijj-summator.html" target="_blank" rel="follow" title="База патентов СССР">Параллельный накапливающий сумматор</a>

Предыдущий патент: Параллельный двоичный сумматор

Следующий патент: Умножитель частоты

Случайный патент: Емкостный преобразователь