Процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

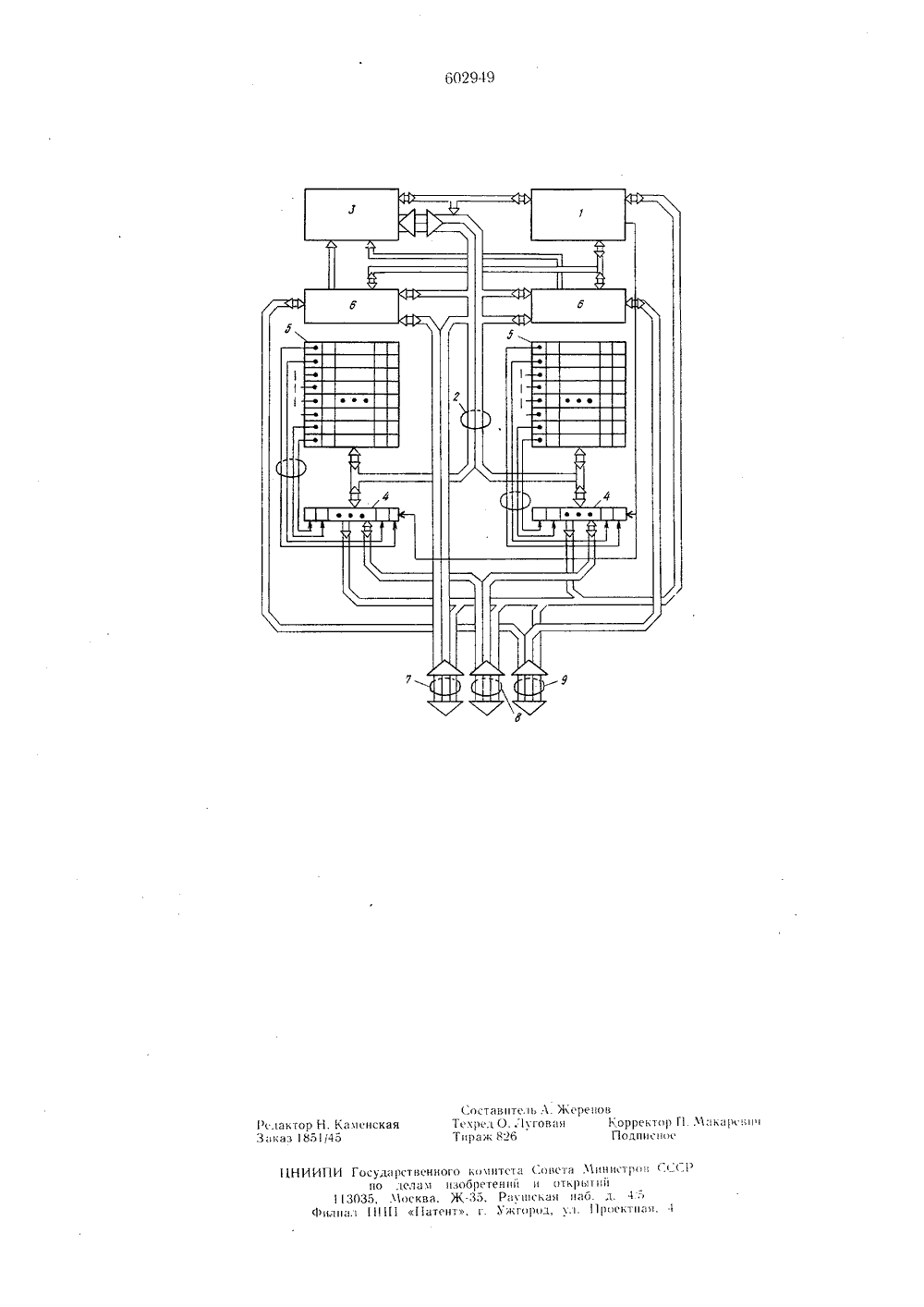

ОПИСАНИЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЙТВЛЬСТВУ Союз Соаетскиа Социалистических в еспублик(5) М, Кл,22) Заавлено 17.08.76 (21) 2 398707/18-24с присоединением заявки Ж -06 Г 15/О риоритетГесударстеенимй кометеСввете Менестрее СССРее делам нэобретвейа еткрытий 43) Опубляковано 1 5,04,77.Бюллетень % 14 46) Дата опубликования описания Рд ОЪ.М УДК 681.32(71) Заявитель 54) ПРОЦЕССОР В так водит тали - сдвиги в буферном регистре. ом устройстве наличие цепей сдвига прик усложнению схем.Наиболее близким по технической сущное. ти к данному изобретению является процес. сор, содержащий блок управления, арифметическо-логическое устройство, регистр данных оперативной памяти, блок регистров общего назначения, блок регистров специального назначения, соединенные между собой двухсто. ронними связями, адресные и информационные входы и выходы блока управления, блока регистров специального назначения, регистра даннык оперативнод памяти соединены соответственно с адресными и информационными нхо. дами и выходами процессора, выходы блока регистров специального назначения подклкле.ны к соответствующим входам арнфметическо логического устройства 2.В этом процессоре обработка н н форм а цни производится в параллельном коде, а передача данных в телеграфные каналы связи осуществляется групповым способом в последователь. ном коде. Передача битов ннфор м а цн н (дна ко. выхпосылок) в телеграфные каналы вязи в прямом и обратном направлении осушествлн. ется группами,. т.е, обслуживаемые телеграфные каналы связи объединяются в односкоростИзобретение относится к вычислительной технике.Одной из задач, возникающих при построе. нии вычислительных систем, является задача группового преобразования информации. Эта задача, в частности, возникает при проектировании многоканальных коммутационных систем.Известно устройство, представлявшее собой блок-схему памяти для приема н передачи информации через совокупность линий связи. Оно содержит ряд кольцевых блоков памя 10 ти, число которых равно числу блоков в знаке. Каждый блок представляет собой; по существу, сдвиговый регистр с разрядностью, равной числу обслуживаемых каналов, например равной (6. Каждый такой сдвиговый регистр замыкается в кольцо через соответствующий три гер буферного регистра, который, в свою очередь, также является сдвиговым регистром. Устройство управления осуществляет динамическое хранение информации, представленной параллельным кодом, а также последовательный ввод (или вывод) очередного бита в слово (иэ слова) на этапе его прохождения через буферный регистр. Таким образом, имеются два взаимно перпендикулярных и независимых направления сдвига: по вертикали - сдвиги в блоках памяти н по горнзон-д остин и Б. В. Шевкоппясные группы с одинаковыми кодовыми характеристиками. Передача ведется по всем каналам связи данной группы в одном коде илиразными кодами, у которых количество и длина стартовой, знаковых и стоповых посылокодинаковы; группа объединяет 16 каналов связи. Передача последовательных посылок знаков во все каналы связи данной группы ведется синфазно, т.е, все одноименные посылкипередаются одновременно. Формирование группы посылок осуществляется центральным процессором программным способом. Выполняетсяэто следующим образом.Из оперативного запоминающего устройства (ОЗУ) выбирается слово, состояшее из двухбайтов информации, подлежаших выдаче в дваразных канала связи. Из этих байтов выделяются соответствуюшие одноименные биты ипосредством последовательных сдвигов передаются в один из регистров процессора в разряды, соетветствуюшие номерам тех каналовсвязи, в которые требуется передать выбран 20ные из ОЗУ байты.Далее процедура повторяется для новыхдвух байтов информации и так до тех пор, пока не будет сформирована полная группа (16разрядов) одноименных битов для передачи ихв данную группу каналов связи. После выдачисформированной группы битов в каналы процедура повторяется для последующих битов техже передаваемых знаков, пока знаки не будутвыданы полностью. Таким образом, осушествляется групповое преобразование кода знаков.Недостатком такого процессора является ЭОневысокая производительность, связанная с необходимостью выполнения большого количества логических операций и обращений в ОЗУ.Целью изобретения является повышениепроизводительности процессора при работе стелеграфными каналами связи,Поставленная цель достигается тем, что впредлагаемом процессоре выходы одноименныхразрядов регистров блока регистров обшегоназначения соединены со входами соответствуюШих разрядов регистра данных оперативной 4 Опамяти, управляющий вход которого соединенс выходом блока управления.На чертеже представлена блок-схема процессора, где 1 - блок управления, 2 - двухсторонние связи с подключенными к ним арифметическо-логическим устройством 3, регистром 4 данных оперативной памяти, блоком 5регистров общего назначения, блоком 6 регистров специального назначения, 7 - цепи связидля обмена с внешними устройствами, подключенные к блоку 6 регистров специальногоназначения и к блоку 1 управления, 8 - цеписвязи данных оперативной памяти, подклюценные к регистру 4 и к блоку 1 управления,9 - цепи связи адреса оперативной памяти,подключенные к блокам 6, 1. Процессор работает следующим образом.Команда, поступающая из ОЗУ по связям 8, запоминается на регистре 4 и анализируется блоком 1 управления, который вырабатывает необходимую последовательность микрокоманд, управляющих пересылками информации по связям 2, 7, 8, 9 и работой арифметическо-логического устройства 3. В процессе выполнения команды блок 1 формирует исполнительный адрес операнда, хранящегося в ОЗУ, и пересылает этот адрес в блок 6, Блок 6 содержит регистр сигналов для связи с ОЗУ, на котором фиксируется текущее состояние процедуры обмена информацией между процессором и ОЗУ. После пересылки адреса из блока 1 в блок 6 управление связями 8 и 9 осуществляется по асинхронному принципу запрос-ответ. Операнд, выбранный из ОЗУ по исполнительному адресу, поступает по связям 8 в регистр 4 и далее в устройство 3, где осушествляется необходимая операция, соответствующая одной или нескольким микрооперациям устройства 3. Результат операции по связям 2 передается из устройства 3 в один из регистров блока 5 или 6, или, если это определено кодом операции, - в ячейку памяти ОЗУ через регистр 4 и связь 8. Обмен информацией с устройствами ввода/выво. да происходит по связям 7, по которым пере. даются данные адреса и управляющие сигналы,(и соответствующие определенному интерфеису,Формула изобретенияПроцессор, содержащий блок управления, арифматическо-логическое устройство, регистр данных оперативной памяти, блок регистров общего назначения, блок регистров специального назначения, соединенные между собой двухсторонними связями, адресные и информационные входы и выходы блока управления, блока регистров специального назначения, регистра дан. ных оперативной памяти соединены соответственно с адресными и информационными входами и выходами процессора, выходы блока регистров специального назначения подключены к соответствующим входам арифметическо.-логического устройства, отличающийся тем, что, с целью повышения производительности при работе с телеграфными каналами связи, выходы одноименных разрядов регистров блока регистров общего назначения соединены со входами соответствуюших разрядов регистра данных оперативной памяти, управляюший вход которого соединен с выходом блока управления.Источники информации, принятые во внимание при экспертизе;1. Патент США3742466, кл. 340 - 173 ЙС, 1973,2. РЯ - 6 Еес 1 гопса 1 Меззаде 5 М 1 сИпр Яуз 1 ет, 1974.(:оставитс.и, А. ЖсреновТекрсл 01 т гонии Корректор 1.,Чалак вии Тираж 826 Поди и с гик Редактор Н. КаменскаяЗаказ 1851145 ПНИИПИ Государственного комитета (.овста Министров ,.Р по аслан изобретений и открьи ий 113035, Москва, Ж о, Рдт гискал иаб. л. 4 о Филиаи 111 1 атснт, г. Ужгорода, уи. Проектная.

СмотретьЗаявка

2398707, 17.08.1976

ПРЕДПРИЯТИЕ ПЯ Р-6429

ЗВЕРЕВ ЕВГЕНИЙ МИХАЙЛОВИЧ, КОКОРИН ВЛАДИМИР СЕРГЕЕВИЧ, КОСТИН АЛЕКСАНДР ЕГОРОВИЧ, ШЕВКОПЛЯС БОРИС ВЛАДИМИРОВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: процессор

Опубликовано: 15.04.1978

Код ссылки

<a href="https://patents.su/3-602949-processor.html" target="_blank" rel="follow" title="База патентов СССР">Процессор</a>

Предыдущий патент: Устройство для формирования исполнительных адресов

Следующий патент: Вычислительная система последовательного действия

Случайный патент: Твердотельный рентген-видикон