Устройство для вычисления элементарных функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 553612

Авторы: Рейхенберг, Шевченко

Текст

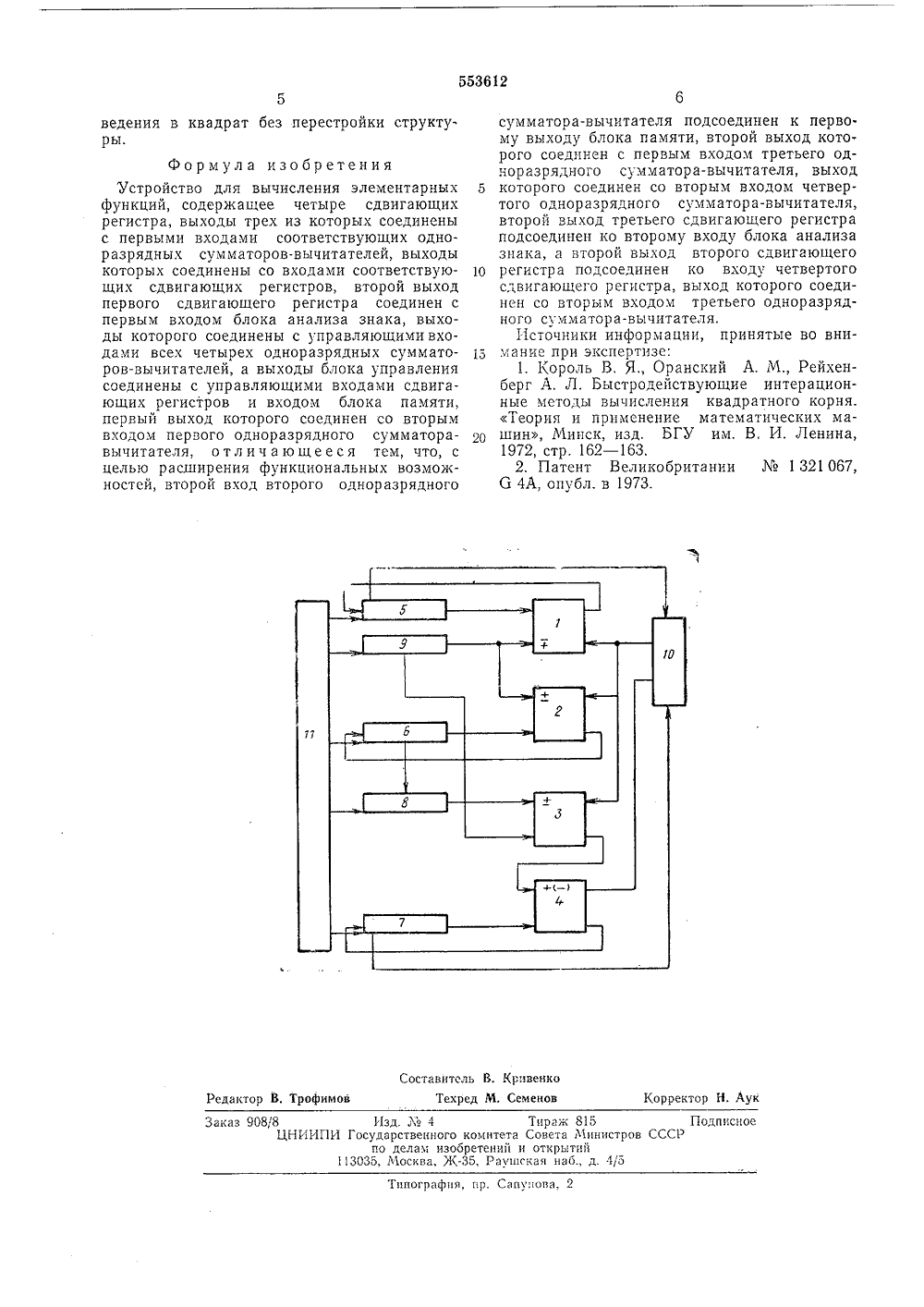

(111 553612 ОПИСАНИЕ ИЗОБРЕТЕНИЯ Союз Соеетсиив Сациаливтическии РеспубликИДЕ ТЕЛЬ СТВ АВТОРСКО(23) Приоритет Совета Министров СССРпо оелам изобретений 7, Бюллетень13(53 У 1,325(088 публиковано 05.0 и открыт та опубликования описания 25.05.77 72) Авторы изобретени Я. Шевченко А, Л. Рейхенб(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕН ЭЛЕМЕНТАРНЫХ ФУНКЦИЙ ожность и не- элементарных что вто- мматоравыод) Изобретение относится к области вычислительной техники и может быть использовано для аппаратного вычисления квадратного корня и возведения в квадрат заданного аргумента в специализированных вычислительных устройствах и машинах.Известно устройство для вычисления элементарных функций, содержащее два одноразрядных сумматора-вычитателя, три сдвигающих регистра, блок памяти, блок анализа знака и блок управления 11.Выходы двух сдвигающих регистров соединены с первыми входами двух одноразрядных сумматоров-вычитателей, выходы которых соответственно соединены со входами этих регистров, выход блока памяти соединен со вторым входом первого одноразрядного сумматора-вычитателя. Второй выход первого сдвигающего регистра соединен со входом блока анализа знака, выход которого соединен со входом управления одноразрядного сумматора-вычитателя.Недостатком его является слвысокая точность вычисленияфункций.Наиболее близким техническим решением к данному предложению является устройство для вычисления элементарных функций, содержащее четыре сдвигающих регистра, выходы трех из которых соединены с первыми входами соответствующих одноразрядныхсумматоров-вычитателей, выходы которых соединены со входами соответствующих сдвигающих регистров, второй выход первого5 сдвигающего регистра соединен с первымвходом блока анализа знака, выходы которого соединены с управляющими входами всехчетырех одноразрядных сумматоров-вычитателей, а выходы блока управления соединены10 с управляющими входами сдвиговых регистров и входом блока памяти, первый выход ко.торого соединен со вторым входом первогоодноразрядного сумматора-вычитателя.Недостатком его является то, что в этом15 устройстве операция возведения в квадратможет быть выполнена только косвенным путем при помощи перемножения, при этомтребуется произвести перестройку связей между блоками. Кроме того, в этом устройстведействия производятся над двоично-десятичными кодами, что определяет сложность устройства.Целью изобретения является расширениефункциональных возможностей устройства(вычисление квадратного корня или квадрата) без перестройки структуры, Последнеепозволяет повысить надежность,Указанная цель достигается тем,рой вход второго одноразрядного су30 вычитателя подсоединен к первомблока памяти, второй выход которого соединен с первым входом третьего одноразрядного сумматора-вычитателя, выход которого соединен со вторым входом четвертого одноразрчдного сумматора-вычитателя, второй выход третьего сдвигающего регистра подсоединен ко второму входу блока анализа знака, а второй выход второго сдвигающего регистра подсоединен ко входу четвертого сдвигающего регистра, выход которого соединен со вторым входом третьего одноразрядного сумматора-вычитатсля.Блок-схема предложенного устройства изображена на чертеже,Устройство содержит одноразрядные сумматорь 1-вычитатели 1 - 4 комбинационного типа, сдш 1 гагощие регистры 5 - 8, блок памяти 9, блок анализа знака 10 и блок управления 11. Выходы сумматоров-вычитателей 1, 2 и 4 соединены со сВОими перВыми Входами через сдвпгающие регистры 5, 6 и 7 соответственно. На вторые входы сумматоров-вычитателей 1 и 2 подсосдинен первый выход блока 9, второй выход которого подсоединен к первому входу сумматора-вычитателя 3.Блок 9 выполнен в виде одностороннего запоминающего устройства таким образом, что по одному адресу одновременно записано два слова (константы Вида 2 - 1 + и 2 - 11+1, где 1 - номер итерации), а выборка их производится поразрядно каждым тактовым (сдвигающим) импульсом. Блок анализа знака 10 выполнен, например, в виде триггера с логическими элементами, Блок управления 11 содержит генератор тактовых сдвигающих импульсов, распределитель, счетчик и логические элементы, Входом устройства в случае вычисления квадратного корня является вход сдвигаюшсго регистра 7, а ьыхо дом - выход сдвпгающего регистра 6. В случае вычисления квадрата входом устройства является вход сдвигающего регистра 5, а выходом - выход сдвигающего регистра 7.Такое выполнение схемы устройства позволяет производить вычисление квадратного корня и квадрата заданного аргумента. Устройство работает следующим образом,При вычислении квадратного корня в третий сдвигающий регистр 7 в параллельном коде вводят заданный аргумент. Первый, второй и четвертый сдвигающие регистры 5, 6, и 8 устанавливают в нулевые состояния.Цикл вычисления состоит из п-итераций, где п - число разрядов аргумента. Каждая итерация выполняется последовательно. В каждой итерации ячейки, состоящие из сумматоров-вычитателей 1 - 4 и сдвигающих регистров 5 - 8, работают параллельно. На блок 10 подается значение знакового разряда сдвигающего регистра 7. Со второго выхода блока 10 на сумматор-вычитатель 4 подается сигнал управления, определяющий режим вычитания. Режим работы остальных сумматоров-вычитателей 1, 2 и 3 определяется сигналом управления с первого выхода блока 10. 10 1 й 20 25 зо 35 Д 45 50 55 60 65 При положительном знаке содержания сдвигающего регистра 7 в сумматоре-вычитателе 1 производится вычитание, а в сумматорахвычитателях 2 и 3 производится сложение, при отрицательном - слокение и вычитание соответственно.В каждой итерации производится в сумматоре-вычитателе 2 алгебраическое сложение очередной константы вида 2 - г+ с предыдущим содержанием сдвигающего регистра 6, В сумматоре-вычитателе 3 производится алгебраическое сложение сдвинутого на 2 - г содержания сдвигаюшего регистра 6 с очередной константой вида 2 - 1+ц. В сумматоре-вычитателе 4 производится вычитание полученного в сумматоре-вычитателе 3 результата из содержания сдвигающего регистра 7. Результаты итерации с выходов сумматоров-вычитатслсй 1, 2 и 4 младшими разрядами вперед записываются в старшие освобождающиеся при сдвиге разряды сдвигающих регистров 5, 6 и 7 и продвигаются при помощи тактовых (сдвига 1 ощих) импульсов к началу сдвигающих регистров 5 - 7. Соответствующее количество тактовых импульсов для продвижения информации в сдвигающих регистрах 5 - 8 подается с выходов блока 11 управления. После выполнения и итераций в сдвигающем регистре 6 находится значение квадратного корня.При вычислении квадрата заданный аргумент подается в параллельном коде в сдвигающий регистр 5. Сдвигающие регистры 6 - 8 устанавливаются в нулевое состояние.На блок 10 подается значение знакового разряда сдвигающего регистра 5. Со второго выхода блока 10 на сумматор-вычнтатель 5 подается сигнал управления, определяющий режим сложения, Режим работы остальных сумматоров-вычитателей 1 - 3 остается прежним. В остальном процесс вычисления квадрата совершенно аналогичен вышеописанному, После выполнения п итераций в сдвигающем регистре 7 находится значение квадратного аргумента.Время вычисления квадратного корня или квадрата равно в тактах Т=п+п(т+1)+т, где т - число дополнительных разрядов для компенсации погрешности при сдвиге.Наличие связей между вторым входом второго одноразрядного сумматора-вычитателя и первого входа блока памяти, второй выход которого соединен с первым входом третьего одноразрядного сумматора-вычитателя, выход которого соединен со вторым входом четвертого одноразрядного сумматора вычитателя, и второго выхода третьего сдвигающего регистра с вторым входом блока анализа знака, а .также второго выхода второго сдвигающего регистра с входом четвертого сдвигающего регистра, выход которого соединен со вторым входом третьего одноразрядного сумматора вычитателя позволяет расширить функциональные возможности устройства, т. е. вычислять функции квадратного корня и возИзд. Ъъ 4 И Государственного комитет по делам изобретений 113035, Москва, К, РаунТираж 815 Совета Министр и открытий скал наб., д. 15 аказ 908/8ЦНИИП ПодписноеСССР ппографпя, пр. Сапунова,ведения в квадрат без перестройки структуры. Формула изобретенияУстройство для вычисления элементарных функций, содержащее четыре сдвигающих регистра, выходы трех из которых соединены с первыми входами соответствующих одноразрядных сумматоров-вычитателей, выходы которых соединены со входами соответствующих сдвигающих регистров, второй выход первого сдвигающего регистра соединен с первым входом блока анализа знака, выходы которого соединены с управляющими входами всех четырех одноразрядных сумматоров-вычитателей, а выходы блока управления соединены с управляющими входами сдвигающих регистров и входом блока памяти, первый выход которого соединен со вторым входом первого одноразрядного сумматоравычитателя, отличающееся тем, что, с целью расширения функциональных возможностей, второй вход второго одноразрядного сумматора-вычитателя подсоединен к перво.му выходу блока памяти, второй выход которого соединен с первым входом третьего одноразрядного сумматора-вычитателя, выход5 которого соединен со вторым входом четвертого одноразрядного сумматора-вычитателя,второй выход третьего сдвигающего регистраподсоединен ко второму входу блока анализазнака, а второй выход второго сдвигающего10 регистра подсоединен ко входу четвертогосдвигающего регистра, выход которого соединен со вторым входом третьего одноразрядного сумматора-вычитателя,Источники информации, принятые во вни 15 мание при экспертизе:1. Король В. Я., Оранский А. М., Рейхенберг А. Л. Быстродействующие интерационные методы вычисления квадратного корня.Теория и применение математических ма 20 шин, Минск, изд. БГУ им. В. И. Ленина,1972, стр, 162 - 163.2. Патент Великобритании1321067,6 4 А, опубл. в 1973.

СмотретьЗаявка

2155607, 08.07.1975

ПРЕДПРИЯТИЕ ПЯ А-3327

РЕЙХЕНБЕРГ АНАТОЛИЙ ЛЕОНИДОВИЧ, ШЕВЧЕНКО РАИСА ЯКОВЛЕВНА

МПК / Метки

МПК: G06F 7/38

Метки: вычисления, функций, элементарных

Опубликовано: 05.04.1977

Код ссылки

<a href="https://patents.su/3-553612-ustrojjstvo-dlya-vychisleniya-ehlementarnykh-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления элементарных функций</a>

Предыдущий патент: Устройство для отображения цифробуквенной информации на экране электронно-лучевой трубки

Следующий патент: Арифметическое устройство

Случайный патент: Механизм подачи и поворота стана холодной