Устройство для определения функции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 521570

Авторы: Рейхенберг, Шевченко

Текст

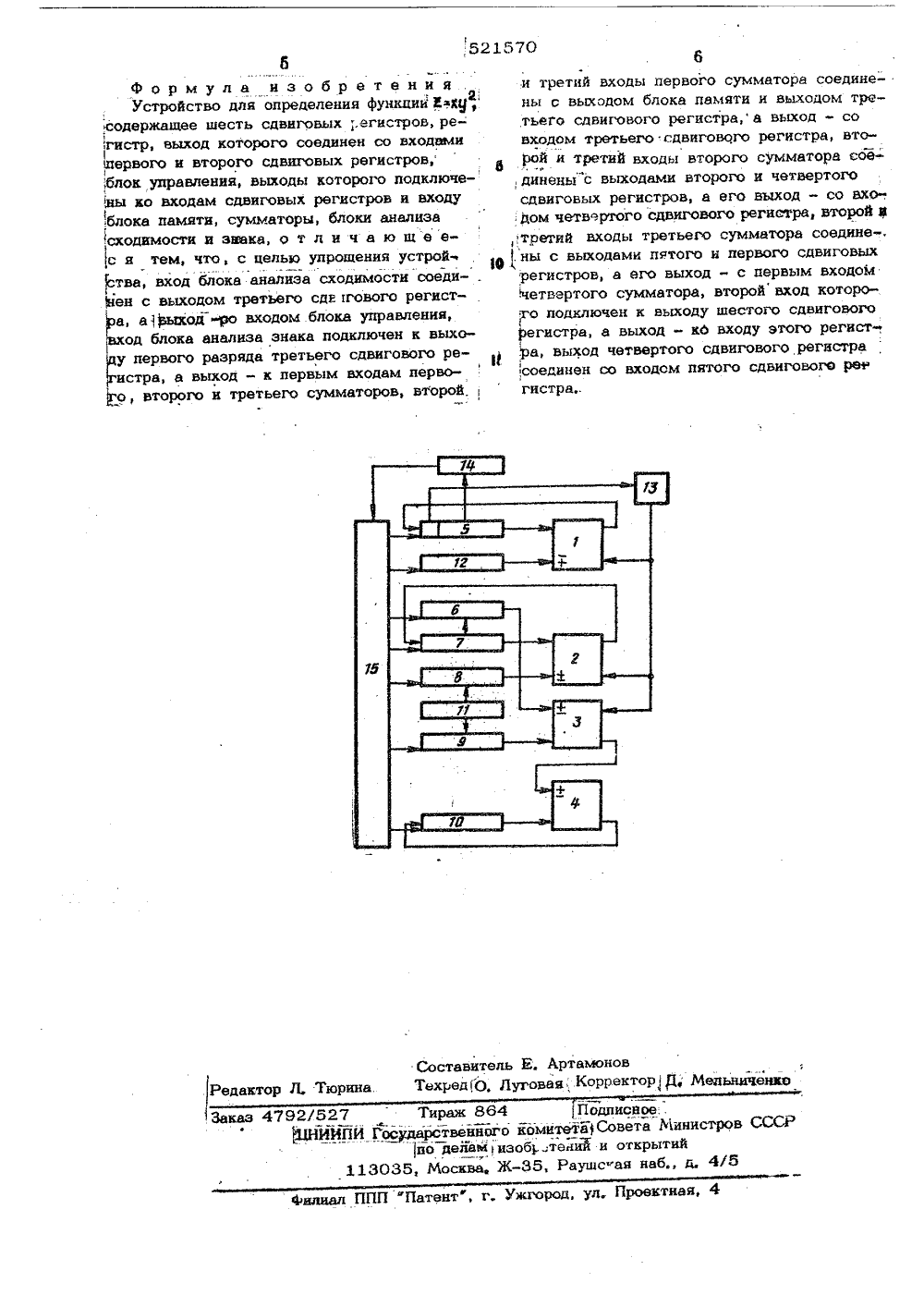

(11) Ь 2157 ОС Союз Советоах Соцмектмческих Республик(21) 1941186/24 15/34 вкиГосударствеииый иомитет Совета Миииетроа СССР ио делам изобретений и отирмтийетень26 я 16.09,76,Опубликовано 1 7.76. Бюл та опубликования описан(71) Заявнтел ЕНИЯ Ф УНКЦИИ Ж = 4) УСТРОИСТко вхо- Илока паления, вьдам сдвимя 1 и, суми знака.ство харавременем ы которого подключе овых реги маторы, б овив ки анализа сходимостиифметическое устройсложностью и большим звестное теризуетс ычислени 1Изобретение относится к цифровой вь- :числительной технике и может найти приме.нение для аппаратного вычисления функции :в специализированных цифровых вычислитель ных машинах и устройствах,.Известны арифметические устройства, вычисляющие степенные функции, содержащие счетчики, конические элементы и регистры. Наиболее близким техническим решением к 1изобретению является арифметическое устрой-) ство специализированных цифровых вычислительных машин, которое выполняет операцию 1определения функции произведения одного ар гумента на квадрат другого косвенно, путем последовательного вычисления двух элемен ,тарных функций. Известное устройство содержит шесть сдвиговых регистров, регистр, выход которого соединен со, входами первого и второго сдвиговых регистров, блок управ-,Целью изобретения является упрощение устройЧтва, а также повышение его быстродействия, В описываемом устройстве это достигается тем, что в нем вход блока ан лиза сходимости соединен с выходом третьего сдвигового регистра, а выход - со входом блока управления, вход блока анализа ,знака подключен к выходу первого разряда ,третьего сдвигового регистра, а выход- к первым входам первого, второго и третьего сумматоров, второй и третий входы .первого сумматора соединейы с выходом блока памяти и выходом третьего сдвигового регистра, а выход - со входом третьего сдвигового регистра, второй и третий входы второго ,сумматора соединены с выходами второго и ,четвертого сдвиговых регистров, а его выход - со входом четвертого сдвигового регистра, второй и третий входы третьего сум матора соединеьхл с выходами пятого и пер,вого сдвиговых регистров, а его выХод - с первым входом четвертого сумматора, второй вход которого подключен к выходу шес,того савигового регистра, а выход - ко вхооду этого регистра, выход четвертого сдвиго521570 Я) тйд Це мв ф в,3 1СОЕдии(хи (ф ВХОДОМ ПЖ ОГО :;сдвигового регистра,НФ чертеже представлена блок-схема ойи-" ываемого устройства.Оно сООтощф из сумматоров 1 не 4 й сдвиговых регистров 5-10, регистра 11, блока 12 амяти, блока 3,3 анализа знака, блока 14ализа сходимости и блока 15 управления, ыход регистра 11 соединен со входамирвого и второго сдвиговых регистров 8 и . 8, Выход первого (знакового) разряда третьего сдвигового регистпа 5 соединен со входом блока 13 анализа знака, выход которого соединен с первыми (управляющими)входами сумматоров 1-3, На второй (управяемый) вход сумматора 1 подсоединен выод блока 12 памяти. На второй вход сумма. тора 2 подсоединен выход второго сдвигового регистра 8. На второй вход суммато ра 3 подсоединен выход пятого сдвигового регистра 6, На второй вход сумматора 4 подсрединен выход сумматора 3, Выход каж-.ого из сумматоров 1, 2 и 4 соединен соответственно через третий, четвертый и шесрой сдвиговые регистры 5, 7 и 10 со своим .Язетьнм ВхоцомеВтОРОЙ ВыхоД ТРетьего сдви н 1 тового ры истре о соединен с биохом 14 вне.;а скодимостий выход поспеднего ооединеи 1 се нтдаом басни 15 уирввденвн. Выходы иоо,ледиего соединены с сдвигающими входамисдвиговых:регистров и входом блока 12 памяти, Выход четвертого сдвигового регистра 7 соединен со входом пятого одвигового региотра 6. Блок 1.3 анализа знака ,СОСТОИТ Иэ СуММатора 4 И ЛОГИЧЕСКИХ ЭЛЕМЕН-и тов. Блок 14 анализа сходимости представляет собой цифровую схему сравнения с логическим нулем. Блок 15 управления содержит генератор тактовых (сдвигающих) импульсасчетчикдешифратор, логическиеэлементы и схемы сброса (прерывания процесса вычисления), В качестве сумматоров 1-4 применены одноразрядные сумматоры - вычислители накопительного типа. В блок 1 2 памяти, который предотавляет собой одностороннее апоминающее устройство с поразрядной выборкой значений очередного раэяда каждым тактовым сдвнгающн имп ль Р сом, записаны константы виде 2 4), где , - номер итерваии. Входом устройстве евляются входы регистра 11 для аргумента Хвходы сдвигового регистра 5 для аргумен таоУВыходом устройства для функции Цй является выход сдвигового регистра 10, Вы ,ходом устройства для произведения аргумеи тов является выход сдвигового регистра 7, Структура устройства относится к параллель Но-последовательной и обеспечивает,оптимальное соотношение между быстродействи ,ем и аппаратурными затратами,В Описываемом устройстве реализуется раЭНОстпоееЯтбраЦНОННЫЙ аЛГОрнтм КоторЫй; последующее умножение Операциямн псевдоделения и псевдоумножения с сохранением,постоянной величины одного из операндов 0+1)Й . В Я -. д, Ц( ЯЦ) + у йсло разрядов аргументов.Раэностные рекурентные сооошения Выффчисляются параллельно в итерационномцессе, Каждое соотношение в устройствечиспйется последовательным путем в каж 3 дой итерации.ВЪачапьиом состоянии в регистр 11 (и в сдвиговые регистры 8 и 9) заносится значение операнда Х в параллельном коде, , в сдвиговый регистр 5 эаноситсягзначениейй операнда У, Сдвиговые регистри 6,7 и 101находются в "нулевом Состоянии, В любой ; итерации в выходов блока 15 управления вы,импульсов, которые продвигают содержание Эв, сдвиговых импульсов в сумматоры, Результаты очередного 1 действии с выходов сум маторов 1, 2 и 4 записываются младшимиразрядами вперед в освобождающиеся при:сдвиге старшие разряды сдвиговь(х регцст- фЬ ров 5, 7 и 6 и продвигаются к началу этихрегистров.Из блока 12 памяти в каждой итерациипоступает очередное значениеконстанты,1; ПО знаку результата в сдвиговом регистре 49 )5 в конце каждой итсераии ,определяется ежим вычитания (спожения) для сумматоа 1 сложения (вычитания) для сумматоров 2 и 3. При отрицательном знаке режим раты сумматоров 2 и 3 меняется на обратЭ 45, ный. После 1 выполнения итераций в сдвиговом регистре 10 находится,значение функции произведения одного аргумента на квац-т второгой в сдвиговом ги 7 и р е стре рОееиэведение аргументов, а в сдвиговых ре гистрах 5, 6, 8 и 8 - нулевые значения.днако для большинства значений операндовХ и У процесс вычисления заканчиваетсяна итерации с номером меньше значени. .,При равенстве содержания сдвигового ре. бб гистра 5 нулю сигнал с блока 14 анализа1 сходимости останавливает подачу тактовых, импульсов с блока 15 управления на следующей иРерациинипроцесс вычисления . За,канчивается, Максимальное время вычисле О, ння в тактах равно Т 4 й +Йд.521570 СоставительТехред (О,амонов торД, Медьничение тор Л. Тюрин овая одписноеСовета Миння н открытийушсая наб., д. 864Йного комитет ламизоб. те ва, Ж, Р 792/527 ЦНИНПИ Го и дарстве 1 по де5, Мос род, ул. П г ате оФормула изобретения Устройство для определения функпин ййу б содержащее шесть сдвиговых ;.егистров, ре 1 гистр, выход которого соединен со входами щервого и второго сдвиговых регистров, блок управления, выходы которого подключены ко входам сдвиговых регистров и входу :блока памяти, сумматоры, блоки анализа сходимости и зжака, о т л и ч а ю щ е ес я тем, что, с целью упрощения устрой тва, вход блока анализа сходимости соеди- . нен с выходом третьего сдк адового региста, а 1 фыкод -бо нкодои бдока упраепеннн, нкод блока аналнаа анака подключен к ныхоу первого разряда третьего сдвигового реистра, а выход - к первым входам первоо, второго и третьего сумматоров, второй 6н третий входы первого сумматора соединены с выходом блока памяти н выходом третьего сдвигового регистра, а выход - со входом третьего сдвигового регистра, втоб рой и третий входы второго сумматора сое,динены с выходами второго и четвертого сдвиговых регистров, а его выход - со входом четвертого сдвигового регистра, второйтретий входы третьего сумматора соедине,ны с выходами пятого ц первого сдвиговыхрегистров, а его выход - с первым входом четвертого сумматора, второй вход которого подключен к выходу шестого сдвигового егистра, а выход - ко входу этого регист, ра, выход четвертого сдвигового регистра 1 соеаннен со входом пятого сдвигового рею гистра

СмотретьЗаявка

1941186, 03.07.1973

ПРЕДПРИЯТИЕ ПЯ А-3327

РЕЙХЕНБЕРГ АНАТОЛИЙ ЛЕОНИДОВИЧ, ШЕВЧЕНКО РАИСА ЯКОВЛЕВНА

МПК / Метки

МПК: G06F 17/10, G06F 7/544

Метки: функции

Опубликовано: 15.07.1976

Код ссылки

<a href="https://patents.su/3-521570-ustrojjstvo-dlya-opredeleniya-funkcii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для определения функции</a>

Предыдущий патент: Устройство для моделирования очереди

Следующий патент: Адаптивный коррелометр

Случайный патент: Устройство для бурения скважин для установки полимерных гидроигл