Блок управления преобразователя напряжения в код последовательного приближения

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 873406

Автор: Панков

Текст

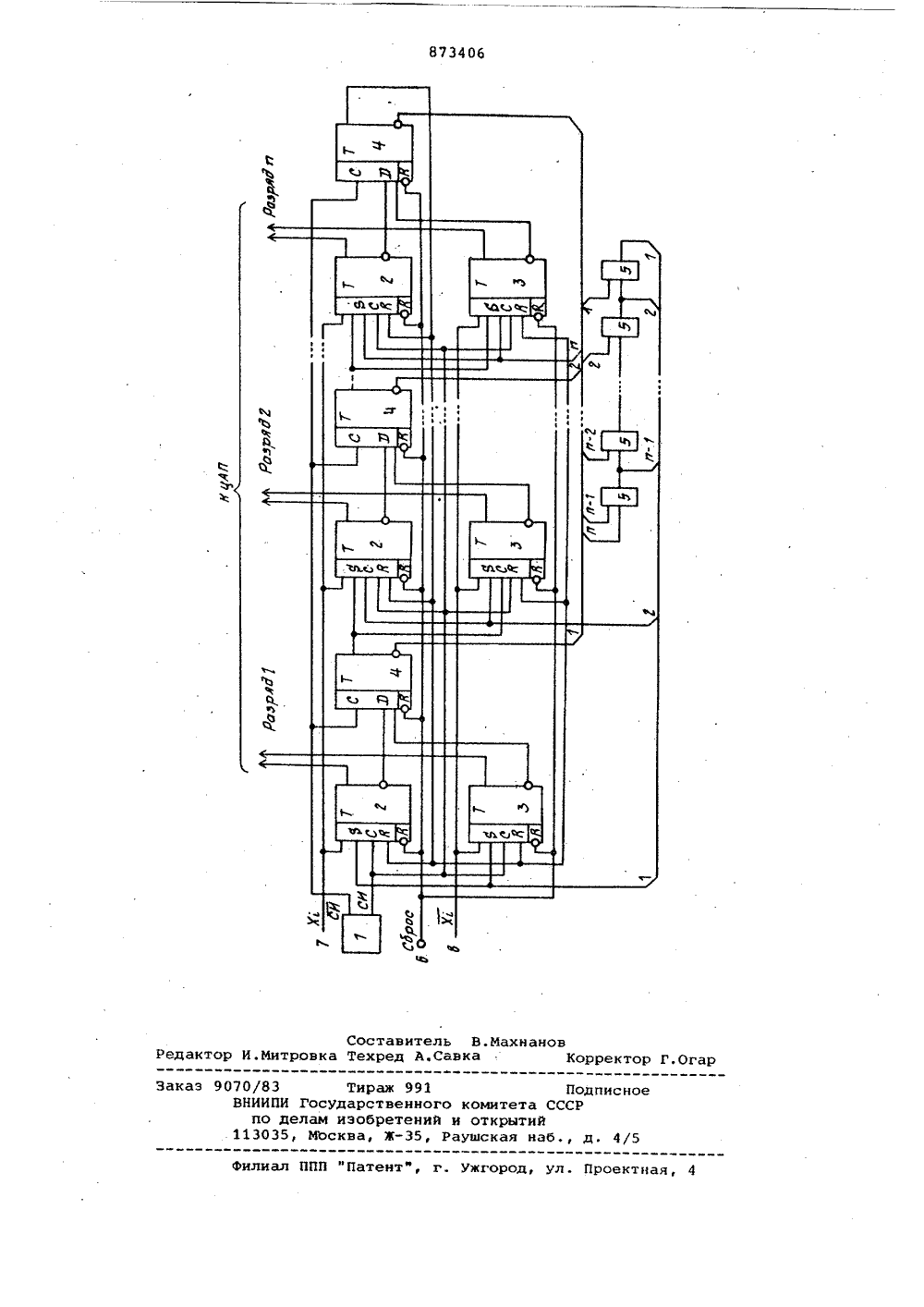

4 ОПИСАНИЕ ИЗОБРЕТЕНИЯ Союз Советскик Социалистических Республикп 11873406 К АВТОИЖОМУ СВИ ЕТЕЛЬСТВУ(22) Заявлено 03. 12. 79 (21) 284 7783/18-21 с присоединением заявки Йо -(23) ПриоритетГосударственный комитет СССР по дедам изобретений н открытий(71) Заявитель Пензенский политехнический институт(54) БЛОК УПРАВЛЕНИЯ ПРЕОБРАЗОВАТЕЛЯ НАПРЯЖЕНИЯ В КОД ПОСЛЕДОВАТЕЛЬНОГО ПРИБЛИЖЕНИЯИзобретение относится к измеритель ной и вычислительной технике и может быть использовано, в частности, в преобразователях напряжения в код последовательного приближения.Известен блок управления преобразователя напряжения в код последовательного приближения, содержащий генератор сигналов, распределитель сигналов и два триггера в каждом разряде, выход генератора сигналов соединен со входом распределителя сигналов, во нсех разрядах входы сброса в 1 нольф, входы, синхронизации и первые входы установки в "единицу" триггеров сое динены с выходами распределителя сигналов, соответственно, вторые входы установки в "единицу" первого и нторого триггеров соединены с шинами "прямого" и "инверсного" выходов бло ка сравнения, "прямой" выход первого триггера соединен с третьимвходом установки в "единицу" второго триггера, "прямой" выход второго триггера соединен с третьим входом установки, 25 в "единицу" первого триггера 13 .Вследствие раздельного выполнения распределителя сигналов, который обеспечивает также распределение тактон работы устройства, и информацион ных регистров на триггерах устройствосложно в изготовлении и требует. значительных затрат оборудования.Известен блок управления преобра" зователя напряжения в код последовательного приближения, содержащий генератор сигналов, первый выход которого соединен со входом синхронизации первого и нторого триггеров каждого разряда, второй выход - со входом синхронизации третьего триггера каждого разряда, вход сброса триггеров соединен с шиной сброса , перныф. вход установки в "единицу" первого и нторого триггеров соеди 61 нен соответственно с шинами прямого" и "инверсного" сигналов сравнения, второй вход установки в "еди" ницу" - с выходом элемента И данного разряда, первый выход первого и второго триггеров подключен к шинам уп" равления цифро-аналоговым преобразователем, второй выход первого триггера соединен с первым входом установки третьего триггера данного разряда, элементы И всех разрядов соединены последовательно 2,В этом устройстве на общих схемных элементах реализуются функции информационных регистров и распределителя тактов работы, такое совмещение функций дает уменьшение затрат оборудования по сравнению с затратами оборудования н известных устроЯ- ствах с выполнением функций информационных регистров и распределителя тактов работы на различных схемных элементах.Однако устройство сложно в изготовлении, так как в нем применены днухтактные триггера, каждый из которых ныполняется из двух однотактных триггеров. Общее число триггеров в и-разрядном устройстве составляет 4 и. Кроме того, в устройстве используется и элементов И-НЕ и и элементов Й. Из-за применения большого числа триггеров изготовление устройства сложно и требует значительных затрат оборудования.Цель изобретения - сокращение ап- паратурных затрат.Цель достигается тем, что в блок управления преобразователя напряжения в код последовательного приближения, содержащий генератор сигналов, перный выход которого соединен со входом синхронизации первого и второго триггеров каждого разряда, второй выход - со входом синхронизации третьего триггера каждого разряда, вход сброса триггеров соединен с шиной сброса, первый вход установки в "единицу" первого и второго триггеров соединен .соответственно с шинами "прямого" и "инверсного" сигналон сравнения, второй вход установки н "единицу" - с выходом элемента И данного разряда, первый выход первого и второго триггеров подключен к шинам управления цифро-аналоговым преобразователем, второй выход первого триггера соединен с первым входом установки третьего триггера данного разряда, элементы И всех разрядов соединены последовательно, н каждом разряде второй выход второго триггера соединен со вторым входом установки третьего триггера данного разряда, "прямой" выход которого соединен с третьим входом установки н "единицу" первого и второго триггеров следующего разряда, "инверсный" выход третьего триггера соединен со вторым входом элемента И,данного разряда, ппрямой" выход третьего триггера последнего разряда соединен со входом установки в "ноль" первого и второго триггеров всех разрядов. На чертеже представлен блок управления преобразователя напряжения в код последовательного приближения, содержащий генератор сигналов 1, триггеры 2,3 и 4, элементы И 5 в каждом разряде. Триггеры 2 и 3 синхронные й 5-триггеры, в качестве триггера 4 применяют синхронный О-триггер, вход О которого использу ЬО 65 линается логическая единица, которая Разрешает занес-ние результатовсравнения Х 1 и Х 1 н триггеры 2 и 3следующего разряда во втором тактеработы устройства. Одновременно сигналом логического ноля с "инверсного" ется для управления установки триггера 4 н состояние "ноль",Во всех разрядах входы сброса в"ноль" триггеров 2,3 и 4 соединенысо входом 6 устройства. Входы синхронизации триггеров 2,3 и 4 соединены свыходами генератора сигналов 1 соответственно, Первые входы установкив "единицу" триггеров 2 и 3 соединены с шинами 7 и 8 "прямого" и"инверсного" сигналов сравнения. Элементы И 5 соединены последовательно.В каждом разрядевторые входы установки в "единицу" триггеров 2 и 3соединены с выходами элемента И 5данного разряда. Выход триггера 215 соединен с первым входом .установкитриггера 4 данного разряда. В каждомразряде выход триггера 3 соединен совторым входом установки триггера 4данного разряда, "прямой" выход кото 20 рого соединен с третьими входами установки в "единицу" триггеров 2 и 3следующего разряда. "Инверсный" выход триггера 4 соединен со входом элемента И 5 данного разряда. "Прямой"выход триггера 4 последнего разрядасоединен со входами установки н "ноль"триггеров 2 и 3 всех разрядов.Устройство работает следующим образом.По сигналу, поступающему на вход бустройства триггеры 2,3 и 4 всехразрядов сбрасываются н "ноль". Этотсигнал необходим только для принудительного приведения устройства н ис.ходное состояние. После каждого цикла преобразования это состояние периодически восстанавливается без дополнительных сигналов на вход б устройства. При этом сигналами с "прямых" выходов триггеров 4 запрещает 40 ся занесение результатов сравненияпо сигналам Х, и Х; в триггеры 2 и 3всех разрядон, кроме первого разряда, На входах управления Установкойн "единицу" триггеров 2 и 3 перво 45 го Разряда пРисутствует н момент поступления очередного синхроимпульсаСИ от генератора сигналов 1 логическая единица с выхода элемента И 5перного разряда. Результат сравнения Х= 1 фиксируется в триггер 2,а результат сравнения Х = 1 - втриггер 3 первого разряда. По сигналу СИ состояние триггера 4 перногоразряда меняется с "ноля" на "единицу", так как схема совпадения повходу О , обеспечивающая установкутриггера 4 в "ноль", блокируетсязапрещающим сигналом с "инверсного"ныхода триггера 2 или 3. Далее навыхода триггера 4 первого разрядачерез элемент И 5 первого разряда запрещается повторное изменение состояния триггеров 2 и 3 первого разряда.АНалогичным образом происходит разрешение занесения результатов сравнения Х и Х 162,п) в триггеры 2 и 3,5следующих разрядов и запрещениеповторного изменения состояния триггеров 2 и 3 предшествующих разрядов.После занесения результатов сравнения Х и Х в триггеры 2 и 3 последнего разряда и сигнал логической единицы с,"прямого" выхода триггера 4последнего разряда поступает на вхо"ды установки в ."ноль" триггеров 2 и3 всех разрядов. В момент приходаочередного сигнала СИ триггеры 2 и3 всех разрядов переводятся в состояние "ноль". По сигналу СИ это состояние фиксируется триггерами 4всех разрядов. Устройство вновь переходит в исходное состояние. Ему;соответствует тактопределения стар"щего разряда кода преобразуемого на"пряжения.При необходимости управления со"стоянием триггера 4 может быть выполнено по сигналам с фпрямыхф выходов триггеров 2 и 3. В этом случаепо входу О реализуется схема собирания, вход О используется для управления установкой триггера 4 в состояние "ноль". При использовании вкачестве триггера 4 синхронного Явтриггера управление по входам установки й и 5 осуществляется по соотношениям355 = (Ю+ Ю)СНСИ1где 01,0 61 0 - сигналы с фпрямыхф и "инверсных" выходовтриггеров 2 и3,В устройстве используется Зл однотактных триггеров и о элементов И. 45Применение в каждом разряде устрой"ства трех однотактных триггеров вместо двух двухтактных триггеров со"кращает затраты оборудования на 25.Уменьшение числа схемных элементов. упрощает схему устррйства и повышает ее надежность. В преобразователенапряжения в код с предлагаеыам блоком управления повышается быстРО"действие, так как в данном устройстве сигналы на входы ЦАП поступаютс выходов 2 и З,меняющих свое состо"яние по переднему фронту сигнала СИ. В известном устройстве сигналы наЬвходы цАП поступают с выходов второй ступени двухтактных триггеров 2 и 3, которые меняют свое состояние по сигналам СИ. Последнее обстоятельство увеличивает каждый такт преобразования известного устройства на длительность синхимпульса СИ - 2-4 Т, где Г - среднее .время задержки элементов второй ступени двухтактных триггеров.Формула изобретенияБлок управления преобразователянапряжения в код последовательногоприближения, содержащий генераторсигналов, первый выход которого соединен ао входом синхронизации первого и второго триггеров каждогоразряда, второй выход - со входомсинхронизации третьего триггера каждого разряда, вход сброса триггеровсоединен с шиной сброса, первый входустановки в "единицу" первого и вто- .рого триггеров соединен соответственно с шинами фпрямогоф и "инверсионногоф сигналов сравнения, второй вход установки в "единицуф - свыходом элемента И данного разряда,первый выход первого и второго триггеров подключен к шинам управленияцифро-аналоговым преобразователем,второй выход первого триггера соединен с первым входом установки третьего триггера данного разряда, элементы И всех разрядов соединены последовательно, о т л и ч а ю щ и й с ятем, что, с целью сокращения аппаратурных затрат, в каждом разрядевторой выход второго триггера соединен со вторым входом установки третьего триггера данного разряда,фпрямойф выход которого соединен стретьим входом установки в фединицуфпервого и второго триггеров следующего разряда, финверсный" выход третьего триггера соединен со вторымвходом элемента И данного разряда,"прямой" выход третьего триггера последнего разряда соединен со входомустановки в фнольф первого и второго триггеров всех разрядов.Источники информации,принятые во внимание при экспертизе1. Патент ФРГ 9 1129716,кл.б 06 Г 13/ОО, 1962.2. Авторское свидетельство СССРпо заявке 9 2697549/21,кл, Н 03 К 13/17, 1978,(прототип ).91ного коний и о5, Рауш Тираж 9 дарствен иэобрете ква, Жписное наб лиал ППП "Патент", г. Ужгород, ул. Проектная, 4 з 9070/83 ВНИИПИ Го по делам 113035, МЬмит кр ка Па СССий

СмотретьЗаявка

2847783, 03.12.1979

ПЕНЗЕНСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

ПАНКОВ ЛЕОНИД НИКОЛАЕВИЧ

МПК / Метки

МПК: H03K 13/17

Метки: блок, код, последовательного, преобразователя, приближения

Опубликовано: 15.10.1981

Код ссылки

<a href="https://patents.su/4-873406-blok-upravleniya-preobrazovatelya-napryazheniya-v-kod-posledovatelnogo-priblizheniya.html" target="_blank" rel="follow" title="База патентов СССР">Блок управления преобразователя напряжения в код последовательного приближения</a>

Предыдущий патент: Аналого-цифровой преобразователь

Следующий патент: Устройство для преобразования напряжения в цифровой код

Случайный патент: Устройство для дозирования вязких материалов