Устройство для фильтрации сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

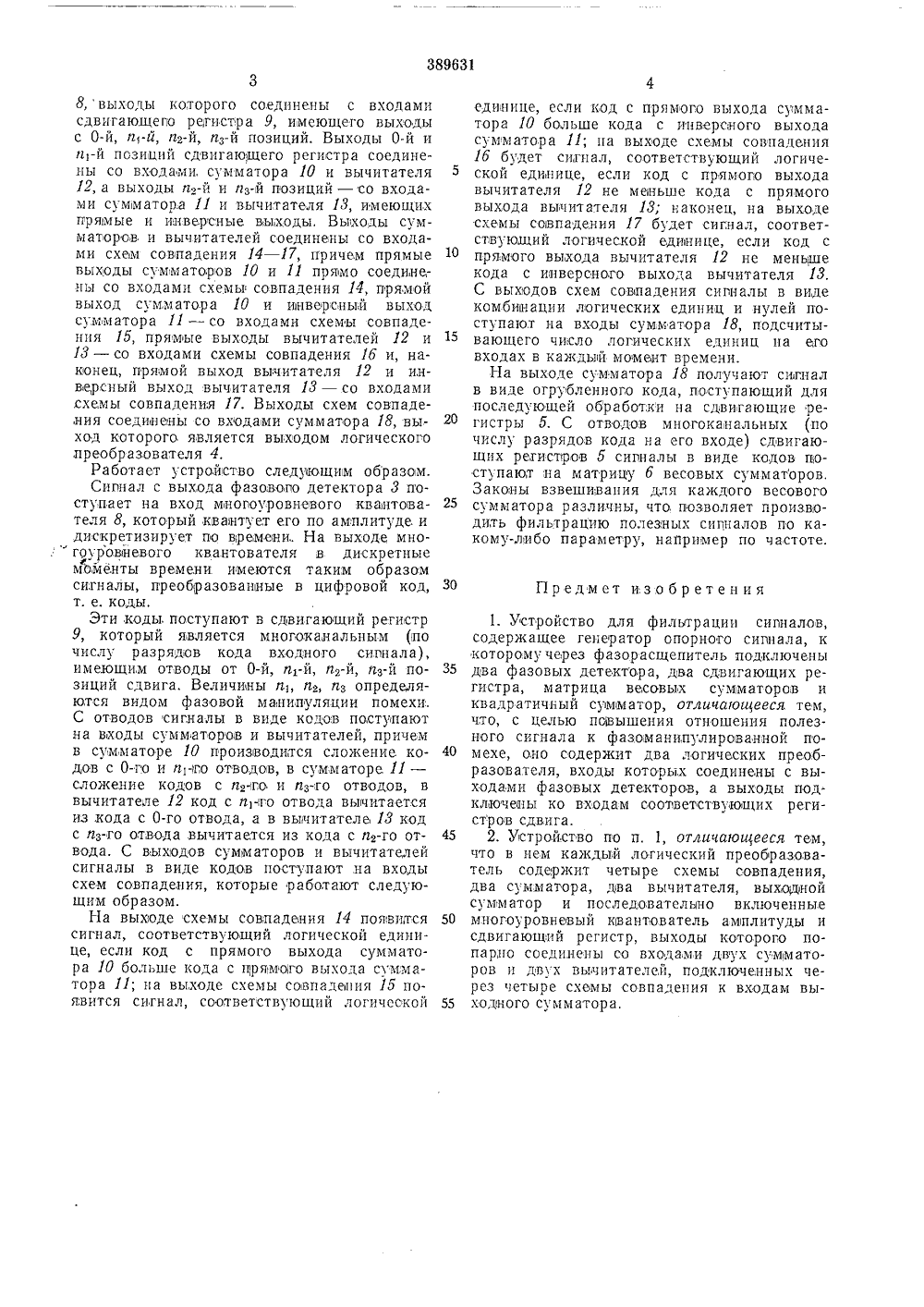

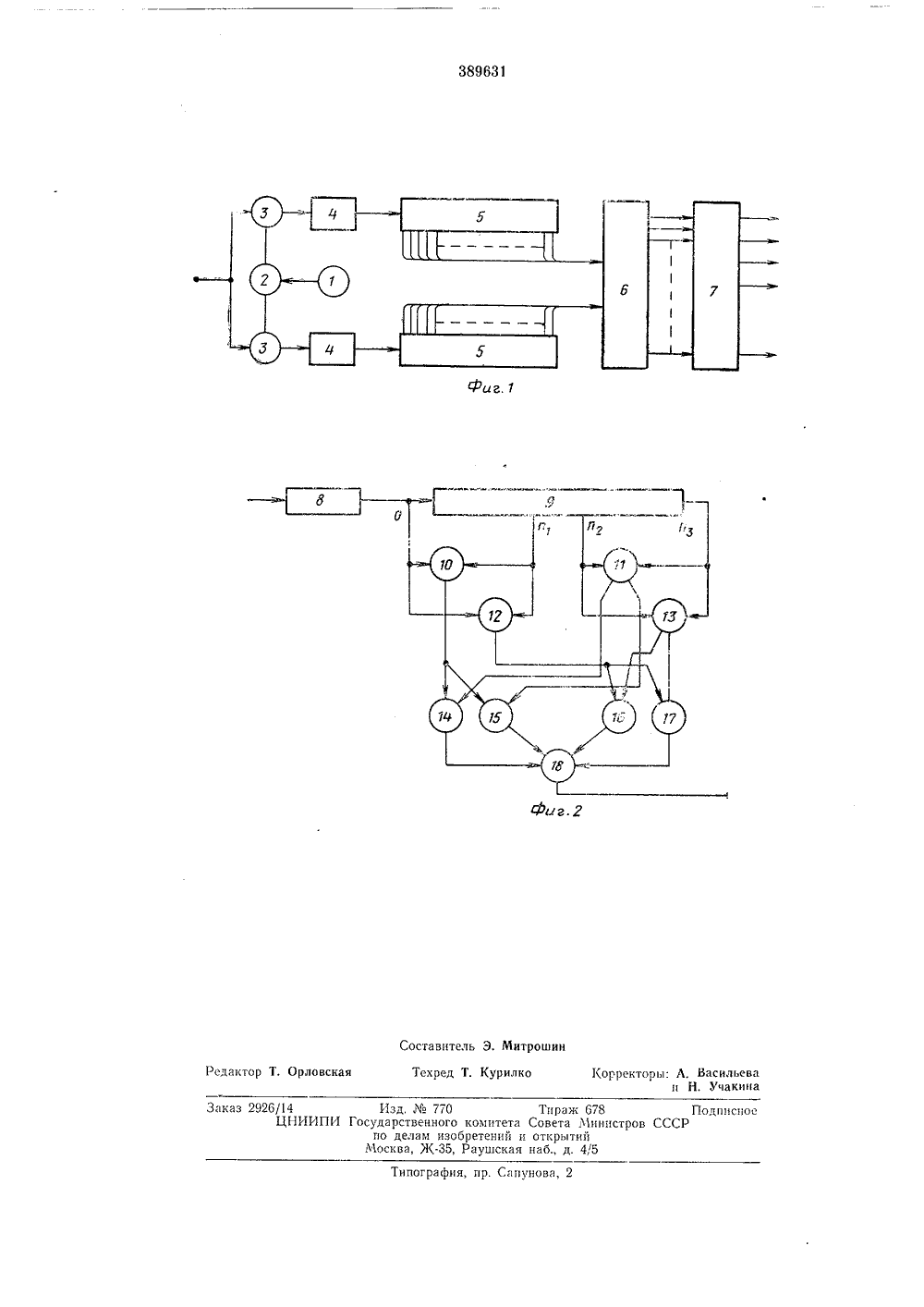

ИЗОБРЕТЕНИЯ ависимое от авт, свидетельствааявлено 26 ЛЧ.1971 ( 1649170/18-24).Кл, Н 041 з 7 присоединением заявкиГосударственный камнтет Совета Мнннстрав СССР ла делам изааретений н открытнйорите Бюллетень29ания 29.Х.1973 Опубликовано 05 Л 1.197 Дата опубликования оп УДК 621.372,54 (088.8 Авторыизобретеии В, К. Слока, В, Ф. Стручев, Д.. И, 1 Цетини аявитсль СТРОЙСТВО ДЛЯ ФИЛЬТРАЦИИ СИГНА Изобретение относится к радиотехнике.Известны устройства для фильтрации сигналов, содержащие генератор опорного сигнала, к которому через фазорасщепитель подсоединены два сдвигающих регистра,мат рицы весовых сумматоров и квадратичный сумматор. На выходе известных устройств фильтрации отношение сигнал - шум умвньшается, что затрудняет выделение полезааого сигнала и изменение его параметров. 10Предложенное устройство отличается тем, что оно содержит два логических преобразователя, входы которых соединены с выходами фазовых детекторов, а выходы подключены ко входам соответствующих регистров 15 сдвига.Каждый логический преобразователь содержит четыре схемы совпадения, два сумматора, два вычитателя, выходной сумматор и последовательно выключенные многоуровне вый квантователь амплитуды и сдвигающий рс истр, выходы которого попарно соединеиы со входами двух сумматоров и двух вычитателей, подключевных через четыре схемы совпадения ко входам выходного сумма тора. Это позволяет повысить на выходе фильтра отношение полезного сигнала к фазоманипулировгнной помехе.На фиг. 1 изображена блок-схема устройУстройство состоит из генератора опорного сигнала 1, фазорасщепителя 2, двух квадратурных каналов, включающих в себя фазовые детекторы 8, логические преобразователи 4, сдвигающие регистры с отводами 5, матрицы б и 7 весовых сумматоров и квадратичных сумматоров.На фиг. 2 показана структурная схема логического преобразователя. Преобразователь состоит из многоуровневого квантователя 8, сдвигающео регистра 9 с отводами на малое в сравнении с длительностью сигнала время, сумматоров 10, 11, вычитателей 12, 18, схем совпадения 14 - 17 и сумматора 18,Элементы устройства соединены следующим образом.Выход генератора опорного сигнала 1 соединен с фазорасщепителем 2, выход фазорасщепнтеля - с управляющими, Входами фазовых детекторов 3. Другие входы фазовых детекторов являются входом устройства, Выходы фазовых дстекторов соединены с логическими преобразователями, выходы которых соединены со сдвигающнмп регистрамп 5. К выходам сдвигающих регистров 5 подсоединсны входы матрицы б весовых сумматоров, к выходам которой подсоединены входы матрицы 7 квадратичных сумматоров,Входом логического преобразователя 4 является вход многоуровневого, квантователя8, выходы которого соединены с входами сдвнгающепо регистра 9, немеющего выходы с О-й, а-й, а-й, ад-й позиций. Выходы О-й и и 1-й позиций сдвигающего регистра соединены со входами, сумматора 10 и вычитателя 5 12, а выходы п.-й и п-й позиций - со входами сумматора 11 и вычитателя 13, имеющих нрягмые и инверсные выходы. Выходы сумматоров и вычитателей соединены со входами схеа совпадения 14 - 17, причем прямые 10 выходы суаматоров 10 и 11 пряао соедине; ны со входами схемы совпадения 14, прямой выход сумматора 10 и инверсный выход сумматора 11 - со входами схемы совпадения 15, прямые выходы вычитателей 12 и 15 13 - со входами схемы совпадения 1 б и, наконец, прямой выход вычитателя 12 и инверсный выход вычитателя 13 - со входами .схемы совпадения 17. Выходы схем совпаде,ния соединены со входами сумматора 18, вы ход которого является выходом логического преобразователя 4.Работает устройство следукщим образом.Сипнал с выхода фазового детектора 3 поступает на вход мнопоуровневого квантова теля 8, который квантует его по амплитуде, и дискретизирует по времениНа выходе мно гоуровйевого квантователя в дискретные моменты времени имеются таким образом сигналы, преобразованные в цифровой код, 30т. е. коды.Эти коды, поступают в сдвигающий регистр 9, который является многоканальным (по числу разрядов кода входного сипнала), имеющим отводы от О-й, п 1-й, п 2-й, п-й по- З 5 зиций сдвига. Величины аь ппз определяются видом фазовой манипуляции помехи.С отводов сигналы в виде кодов поступают на входы сумматоров и вычитателей, причем в сумматоре 10 производится сложение ко дов с О-го и а,иго отводов, в сумматоре 11 в сложение кодов с а 2-го и аз-го отводов, в вычитателе 12 код с и 1 чго отвода вычитается из,кода с О-го отвода, а в вычитателе 13 код с пз-го отвода вычитается из кода с а,-го от вода. С выходов сумматоров и вычитателей сигналы в виде кодов поступают на входы схем совпадения, которые работают следующим образом.На выходе схемы совпадения 14 появится 50 сигнал, соответствующий логической единице, если код с прямого выхода сумматора 10 больше кода с пряаово выхода сумматора П; на выходе схемы совпадения 15 появится сигнал, соответствующий логической 55 единице, если код с прямого выхода сумматора 10 больше кода с инверсного выхода сумаатора 11; па выходе схемы совпадения 1 б будет сигнал, соответствующий логической единице, если код с прямого выхода вычитателя 12 не меньше кода с прямого выхода вычитателя 13; наконец, на выходе схемы совпадения 17 будет сигнал, соответствующий логической единице, если код с прямого выхода вычитателя 12 не меньше кода с инверсного выхода вычитателя 13. С выходов схем совпадения сигналы в виде комбинации логических единиц и нулей поступают на входы сумматора 18, подсчитывающего число логических единиц па его входах в каждый момент времени.На выходе сумматора 18 получают сигнал в виде огрубленного кода, поступающий для последующей обработки на сдвигающие регистры б, С отводов многоканальных (по числу разрядов кода на его входе) сдвигающих регистров б сипналы в виде кодов проступают Ба матрицу б весовых сумматоров, Законы взвешивания для каждого весового сумматора различны, что, позволяет производить фильтрацию полезных сипналов по какому-либо параметру, например по частоте.Предмет изобретения1. Устройство для фильтрации сипналов, содержащее генератор опорного сипнала, к которому через фазорасщепитель подключены два фазовых детектора, два сдвигающих регистра, матрица весовых сумматоров и квадратичный сумматор, отличающееся тем, что, с целью повышения отношения полезного сигнала к фазоманипулированной помехе, оно содержит два логических преобразователя, входы которых соединены с выходами фазовых детекторов, а выходы подключевы ко входам соответствующих регистроев сдвига.2. Устройство по п, 1, отличающееся тем, что в нем каждый логический преобразователь содержит четыре схемы совпадения, два сумматора, два вычитателя, выходной сума атор и последовательно включенные многоуровневый квантователь амплитуды и сдвигающий регистр, выходы которого попарно соединены со входами двух сумматоров и двух вычитателей, подключенных через четыре схемы совпадения к входам выходного сумматора.389631фиг. 1Составитель Э. Митрошин Редактор Т. Орловская Техред Т. Курилко Корректоры: Л. Васильеван Н, Учакина Заказ 2926/14 Изд,770 Тираж 678 Подписное ЦНИИПИ Государственного комитета Совета а 1 пнистров СССРпо делам изобретений и открытий Москва, 7 К, Раушская наб., д. 4,5Типография, пр. Сапунова, 2

СмотретьЗаявка

1649170

В. К. Слока, В. Ф. Стручев, Д. В. Щелкин, В. И. Щетинин

МПК / Метки

МПК: H04B 1/62

Метки: сигналов, фильтрации

Опубликовано: 01.01.1973

Код ссылки

<a href="https://patents.su/3-389631-ustrojjstvo-dlya-filtracii-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для фильтрации сигналов</a>