Преобразователь последовательного кода в параллельный

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

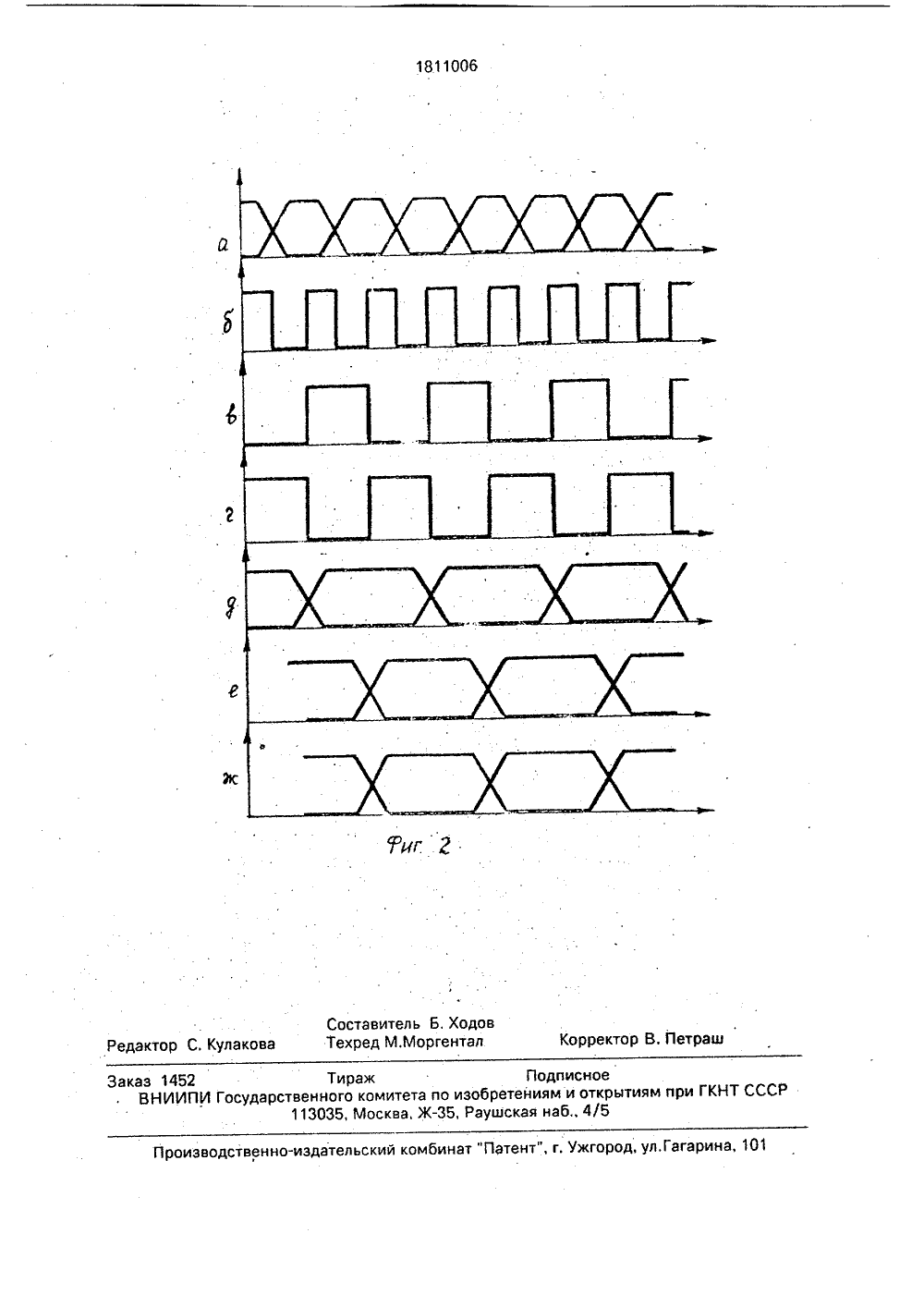

СОЮЗ СО ВЕТСКЙХСОЦИАЛИСТИЧЕСКИРЕСПУБЛИК 1 г) .Ц 06 А/00 ГОСУДАРСТВЕННОЕ ПАТЕНТВЕДОМСТВО СССР(ГОСПАТЕНТ СССР) САНИЕ ИЗОБРЕТЕНИ ЕТЕЛЬСТ АВТОРСКОМУ анных по ци за счетадов преоние егосодержииз которыхбразованиании. Каржит триг системах передачи д налам, В изобретени тиравания всех каск достигается повыше вия, Преобразовате кода в параллельный 1 (гп = 1 Р), в каждом и:2 узлов 2 прео триггер 6 синхрониз преобразования соде 2 ил. 1(71) Центральный научно-исследователь ский институт измерительной аппаратуры (72) К,Г.Вандышев и Н.И.Шишкин(54) ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ. (57) Изобретение относится к вычислительной технике и может быть использовано в ифровым каединого такбразователя быстродейстовательного т щ каскадов содержится я(к=.1, п 1), и ждый узел 2 геры 3,4 и 5.Изобретение относится к вычислительной технике и может найти применение вцифровых каналах передачи данных.Целью изобретения является повышение быстродействия преобразователя за 5счет единого тактирования всех каскадов.На фиг, 1 представлена блок-схема преобразователя; на фиг, 2 - временные диаграммы, поясняющие работупреобразователя, 10.Преобразователь последовательногокода в параллельный содержит гп каскадов1 (в = 1,Ж), в каждом из которых содержитсяп = 2 узлов 2 преобразования (с = 1, гп),каждый узел 2 преобразования содержит 15триггеры 3, 4 и 5, каждый каскад 1 содержиттриггер 6 синхронизации,На фиг. 1 позициями 7 и 8 обозначенысоответственно информационным входом ивходом синхронизации преобразователя, 20позициями 9 и 10 - соответственно информационные выходы и выход сигнала концапреобразования преобразователя,Устройство работает следующйм образом. 25Последовательность входных данных(фиг. 2 а) подается одновременно на входыпервого и второго триггеров 3 и 4 для записиинформации первого каскада 1.1 преобразования. Сопровождающий данные такти-. 30рующий сигнал (фиг. 2 б) подается на входтриггера 6,1 счетчика этого же каскада, Управление записью данных в первый и второй триггеры 3, 4 производится поочередно:в йервом такте запись производится в первьй триггер 3, к которому подключен третийтриггер 5, положительным фронтом сигнала(фиг, 2 в) с второго выхода триггера 6,1; вследующем такте - во второй триггер 4 положительным фронтом сигнала (фиг, 2 г) с 40первого выхода этого же триггера 6, Этимже сигналом (фиг, 2 г) производится перезапись информации иэ первого триггера 3 длязаписи информации в третий триггер 5. Таким образом, во втором такте происходит 45одновременное появление информации, содержащейся в двух последовательных вовремени тактах входных данных (фиг, 2, а),на выходах узла 2.1 (фиг. 2 е, ж), а частотаработы триггеров 3, 4 для записи информации(фиг. 2 д, ж) и триггера 5 задержки (фиг,2 е) узла 2.1 первого каскада 1,1 вдвое нижечастоты поступления входных данных (фиг.2 а).Так как все элементы схемы - триггеры 553, 4 для записи информации, триггеры 5 задержки и триггеры 6 - идентичны, то времена задержки входной информации и сигнала синхронизации одинаковы, Синхронность выходных данных с каждого каскада преобразования и сигнала синхронизации соответствующего триггера 6 обеспечивает возможность подключения всех элементов схемы без дополнительного фаэирования сигналов во времени. При этом в каждом последующем. каскаде происходит увеличение вдвое разрядности параллельных выходных данных при уменьшении вдвое частоты смены информации и сохранении синхронности данных и сигнала синхронизацииФормула изобретения Преобразователь последовательного кода в параллельный, содержащий в каждом из т каскадов (а = 1, 1 Ч) п = 2 узлов преобразования (К = 1, гл) выполненных на первом и втором триггерах, входы данных которьх объединены, вход данных первого триггера узла преобразования первого каскада является информационным входом преобразователя, о т л и ч а ю щ и,й с я тем, что, с целью повышения быстродействия преобразователя за счет единого тактирования всех каскадов, в каждый каскад введен триггер синхронизации и в каждыйузел преобразования - третий триггер, в каждом узле преобразования выход первого триггера соединен с входом данных третьего триггера, в каждом каскаде первый выход триггера синхронизации соединен с синхровходами второго и третьего триггеров узлов преобразования, второй выход триггера синхронизации соединен с синхровходами первых триггеров узлов преобразования данного каскада и с входом триггера синхронизации йоследующего каскада, выход триггера синхронизации последнего каскада является выходом сигнала конца преобразования преобразователя, выходы вторых и третьих триггеров каждого узла преобразования каждого каскада, кроме последнего, соединены с входами данных первых триггеров соответствующих узлов преобразования последующего каскада, выходы вторых и третьих триггеров узлов преобразования последнего каскада являются информационными выходами преобразователя, вход триггера синхронизации первого каскада является входом синхронизации преобразователя,1811006 а ставитель Б, Ход хред М,Моргентал Со ов Редактор С, Кулакова Те Корректор В. Петрашроизводственно-издательский комбинат "Патент", г. Ужго агарина, 101 аказ 1452 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж, Раушская наб., 4/5

СмотретьЗаявка

4752801, 23.10.1989

ЦЕНТРАЛЬНЫЙ НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ ИЗМЕРИТЕЛЬНОЙ АППАРАТУРЫ

ВАНДЫШЕВ КОНСТАНТИН ГЕОРГИЕВИЧ, ШИШКИН НИКОЛАЙ ИВАНОВИЧ

МПК / Метки

МПК: H03M 9/00

Метки: кода, параллельный, последовательного

Опубликовано: 23.04.1993

Код ссылки

<a href="https://patents.su/3-1811006-preobrazovatel-posledovatelnogo-koda-v-parallelnyjj.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь последовательного кода в параллельный</a>

Предыдущий патент: Устройство для декодирования импульсной последовательности

Следующий патент: Устройство для статистического обнаружения дискретных сигналов в каналах связи с межсимвольной интерференцией

Случайный патент: Запоминающий элемент