Формирователь импульсов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

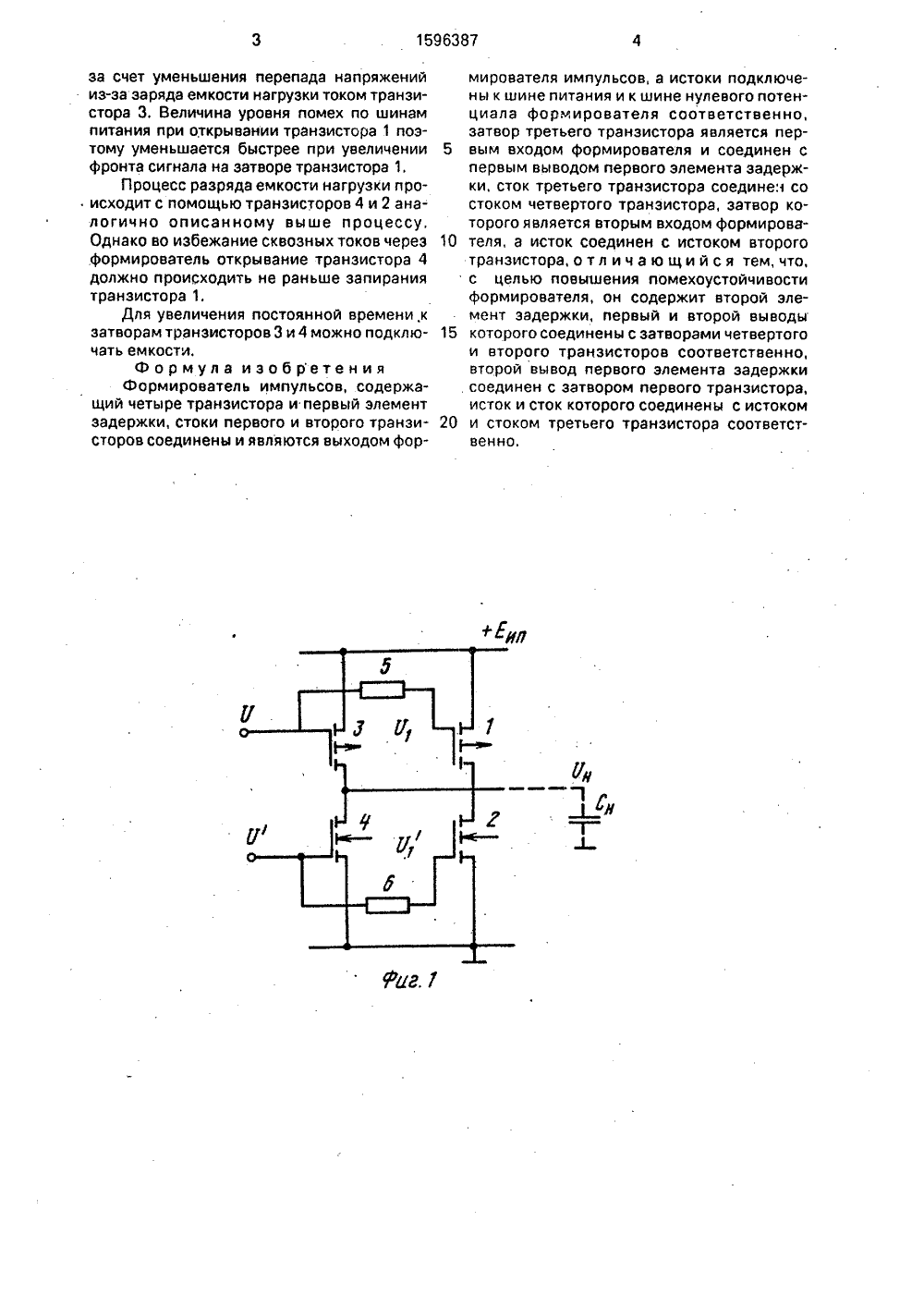

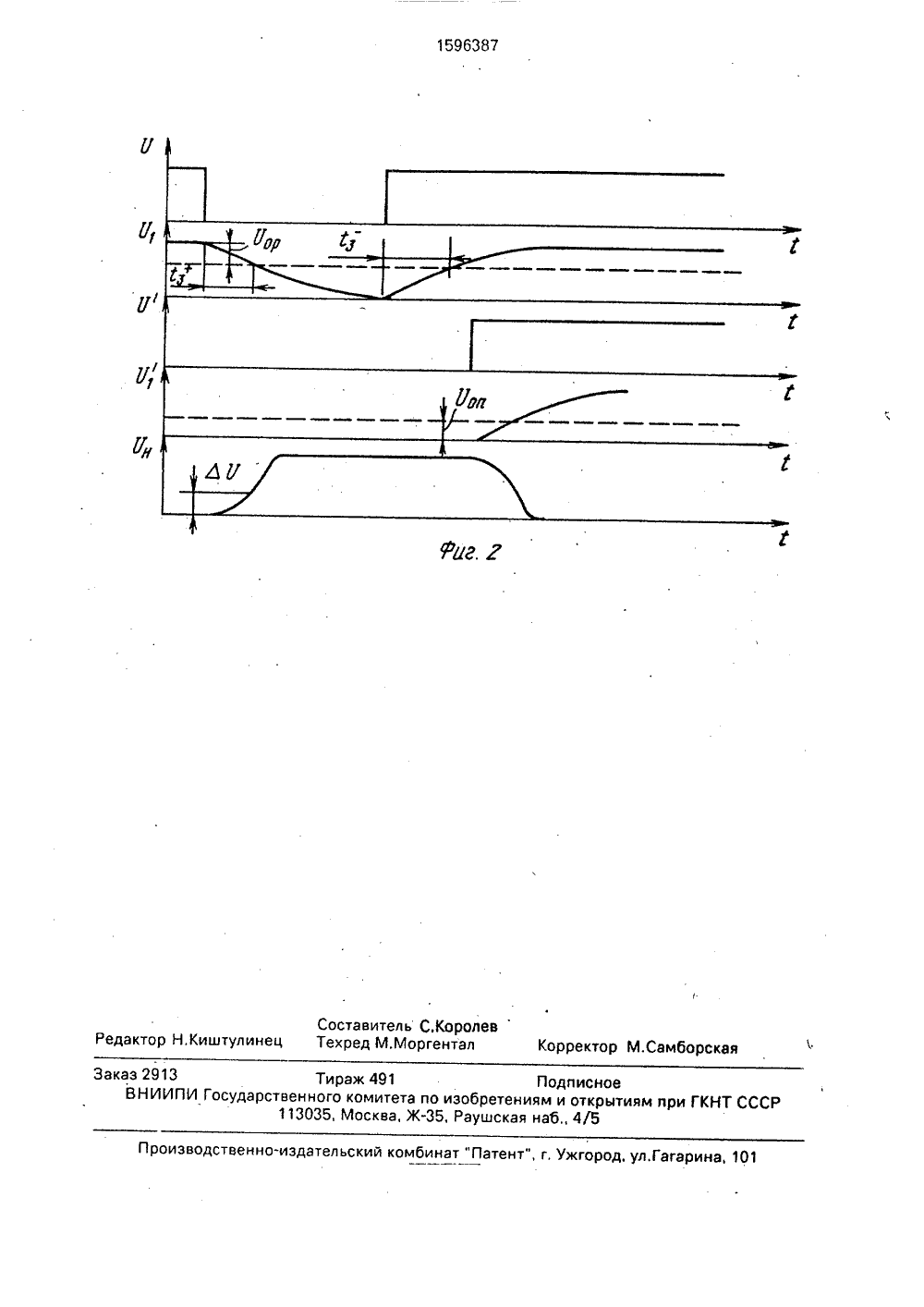

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 596387 1 С 7/00 1)5 ОПИСАНИЕ ИЗОБРЕТЕН АВТОРСКОМУ СВИДЕТЕЛЬСТВУ торы орах ГОСУДАРСТВЕННЫЙ КОМИТЕТ, ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ ПРИ ГКНТ СССР(56) Кармазинский А.Н. Синтез принципиальных схем цифровых элементов на МДПтранзисторах. - М,; Радио и связь, 1983,с. 256.Авторское свидетельство СССРМ 1092563, кл. 6 11 С 700, 1982,(57) Изобретение относится к вычислительной технике и электронике и наиболее эфИзобретение относится к вычислительной технике и электронике и наиболее эффективно может быть использовано в интегральных микросхемах памяти.Цель изобретения - повышение помехоустойчивости формирователя.На фиг. 1 представлена принципиальная электрическая схема формирователя; на фиг. 2 - временные диаграммы его работы.Формирователь импульсов содержит первый р-канальный МДП-транзистор 1, второй и-канальный МДП-транзистор 2, третий р-канальный МДП-транзистор 3, четвертый и-канальный МДП транзистор 4, первый и второй элементы задержки, образованные резисторами 5 и 6 и паразитными емкостями затворов транзисторов 1-4,Формирователь работает следующим образом.В начальный момент все транзис4 закрыты, т,е, напряжения на затв фективно может быть использовано в интегральных микросхемах памяти. Цель изобретения - повышение помехоустойчивости формирователя импульсов. Поставленная цель достигается тем, что формирователь содержит второй элемент задержки на резисторе 6 с соответствующими связями, Снижение уровня помех достигается тем, что транзисторы 3 и 4 на начальном этапе подзаряжают емкость нагрузки, а через некоторое время, определяемое сопротивлением резисторов 5 и 6, происходит отпирание транзисторов 1 и 2 формирователя, Величина сопротивлений также влияет на скорость их отпирания, что определяет быстродействие и уровень помех по шинам питания и земли интегральных микросхем. 2 ил. транзисторов 1 и 3 равны напряжению питания, а напряжения на затворах транзисторов 2 и 4 равны нулю. Заряд на емкости нагрузки отсутствует.При считывании сигнала "1" напряжение на затворе транзистора 3 падает до нуля. Транзистор 3 открывается и емкость нагрузки начинает заряжаться током этого транзистора. Величина тока транзистора 3 выбирается из расчета, чтобы возникающие помехи по шине питания не превышали допустимого уровня. В это время с постоянной времени, определяемой сопротивлением резистора 5 и емкостью затвора транзистора 1, падает напряжение на затворе транзистора 1. Транзистор 1 начинает открываться при спаде этого напряжения от питания на величину порогового напряжения транзистора 1. Снижение уровня помех по шине питания осуществляется не только за счет медленного открывания транзистора 1, но иза счет уменьшения перепада напряжений из-за заряда емкости нагрузки током транзистора 3. Величина уровня помех по шинам питания при открывании транзистора 1 поэтому уменьшается быстрее при увеличении фронта сигнала на затворе транзистора 1,Процесс разряда емкости нагрузки происходит с помощью транзисторов 4 и 2 аналогично описанному выше процессу, Однако во избежание сквозных токов через формирователь открывание транзистора 4 должно происходить не раньше запирания транзистора 1.Для увеличения постоянной времени к затворам транзисторов 3 и 4 можно подключать емкости.Формула изобретенияФормирователь импульсов, содержащий четыре транзистора и первый элемент задержки, стоки первого и второго транзисторов соединены и являются выходом формирователя импульсов, а истоки подключены к шине питания и к шине нулевого потенциала формирователя соответственно, затвор третьего транзистора является пер вым входом формирователя и соединен спервым выводом первого элемента задержки, сток третьего транзистора соединен со стоком четвертого транзистора, затвор которого является вторым входом формирова теля, а исток соединен с истоком второготранзистора, о т л и ч а ю щ и й с я тем, что, с целью повышения помехоустойчивости формирователя, он содержит второй элемент задержки, первый и второй выводы 15 которого соединены с затворами четвертогои второго транзисторов соответственно, второй вывод первого элемента задержки. соединен с затвором первого транзистора,исток и сток которого соединены с истоком 20 и стоком третьего транзистора соответственно.1596387Составитель С.КоролевРедактор Н,Киштулинец Техред М.Моргентал Корректор М.Самборская Заказ 2913 Тираж 491 Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР113035, Москва, Ж, Раушская наб 4/5Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

СмотретьЗаявка

4450607, 28.06.1988

МОСКОВСКИЙ ИНЖЕНЕРНО-ФИЗИЧЕСКИЙ ИНСТИТУТ

БЕРЕЗИН АНДРЕЙ СЕРГЕЕВИЧ, НОВИКОВ АНДРЕЙ ВАЛЕРЬЕВИЧ, ПОПЛЕВИН ПАВЕЛ БОРИСОВИЧ, БАРАНОВ ВАЛЕРИЙ ВИКТОРОВИЧ

МПК / Метки

Метки: импульсов, формирователь

Опубликовано: 30.09.1990

Код ссылки

<a href="https://patents.su/3-1596387-formirovatel-impulsov.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь импульсов</a>

Предыдущий патент: Устройство для контроля кодовой матрицы

Следующий патент: Адресный формирователь

Случайный патент: Устройство для измерения малых деформаций волокон материала конструкции