Аналого-дискретный сумматор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1095194

Автор: Косолапов

Текст

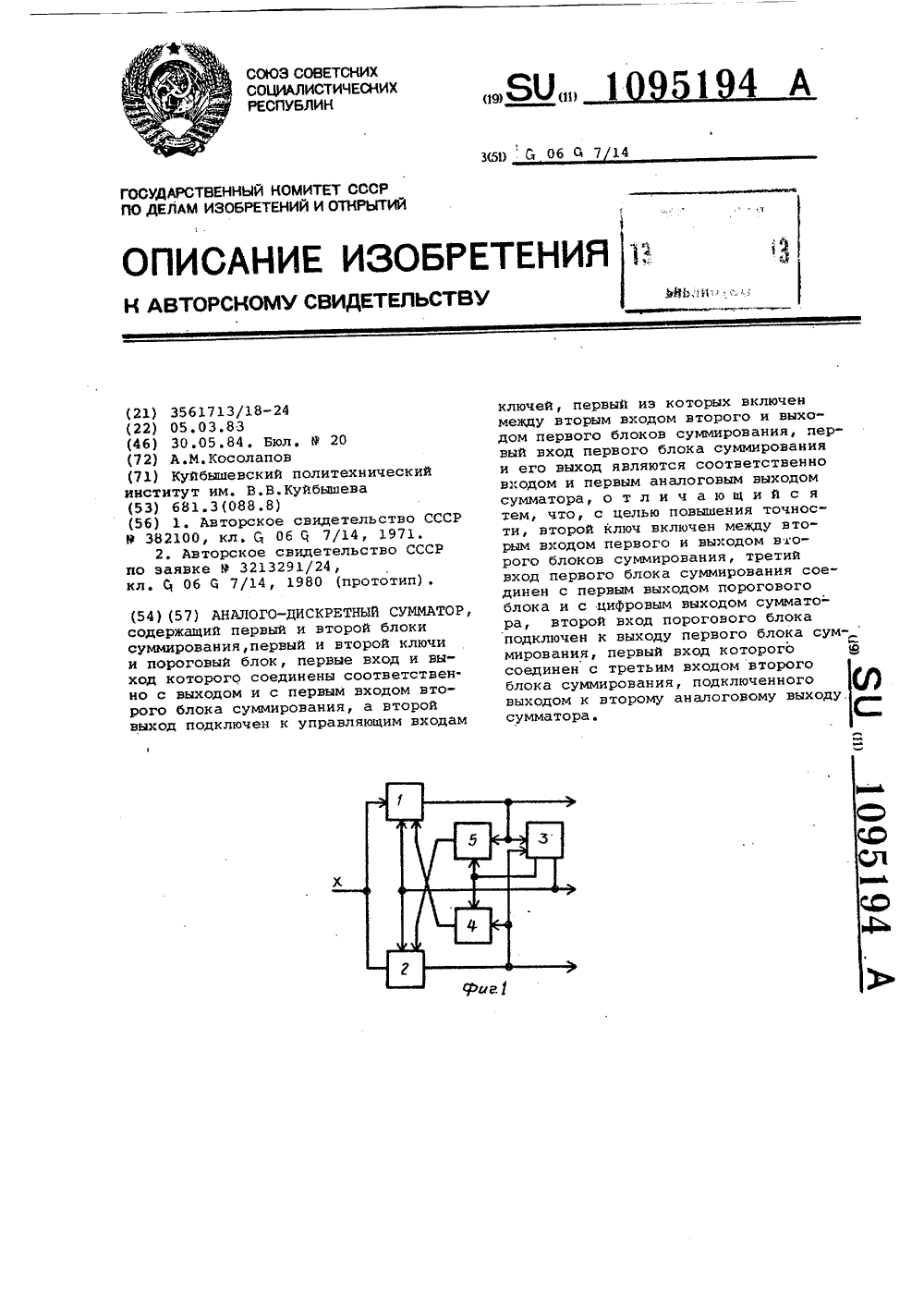

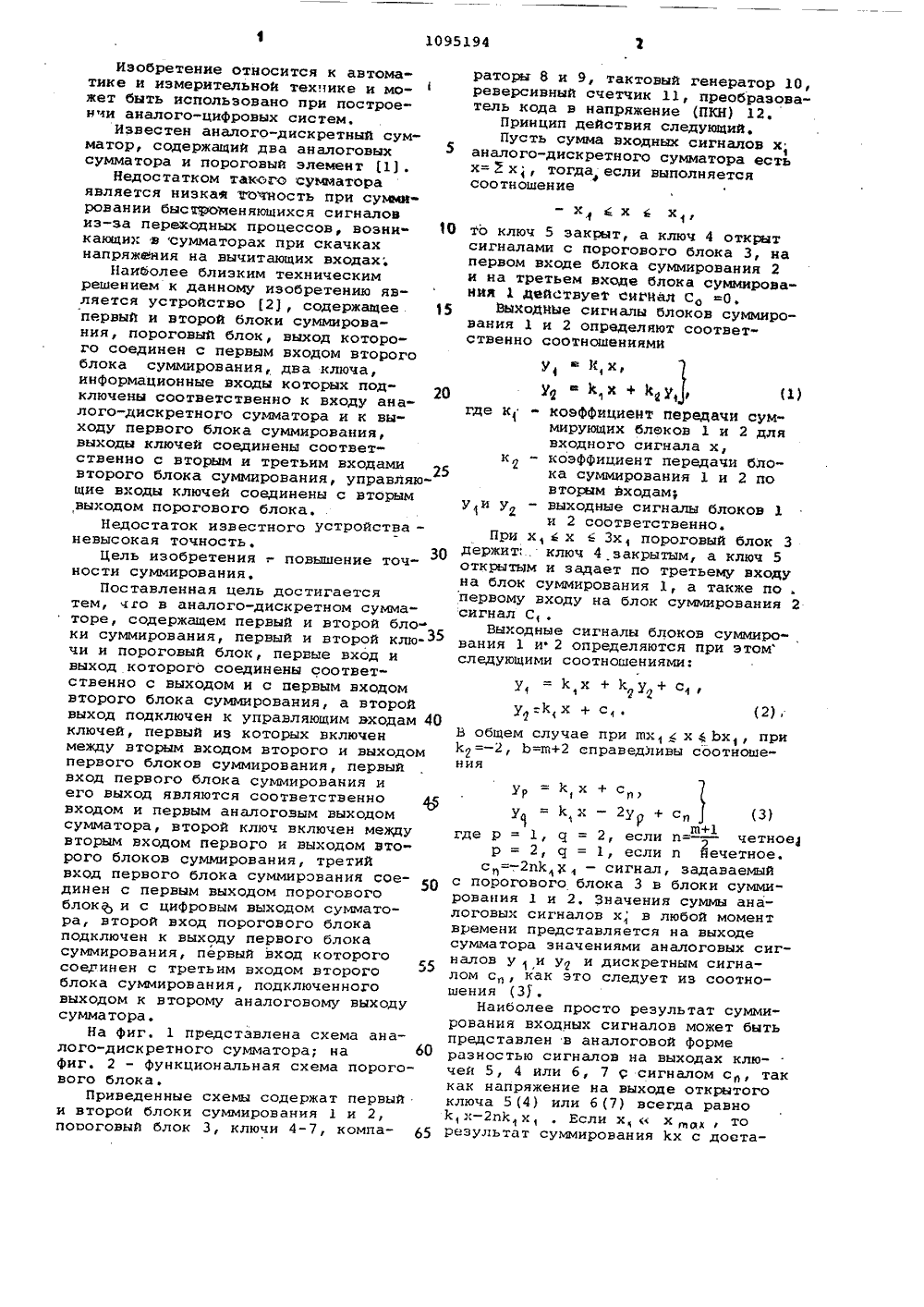

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИН 3(51) Ь 06 О 7 ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ПИСАНИЕ ИЗОБРЕТЕНИЯ йВТОРСНОМУ СВИДЕТЕЛЬСТВУ(56) 1. Авторское свидетельство ССС9 382100, кл. 5 06 ц 7/14, 1971,2Авторское свидетельство СССРпо заявке Р 3213291/24,кл. 0 06 й 7/14, 1980 (прототип) .(54)(57) АНАЛОГО-ДИСКРЕТНЫЙ СУММАТОР,содержащий первый и второй блокисуммирования, первый и второй ключии пороговый блок, первые вход и выход которого соединены соответственно с выходом и с первым входом второго блока суммирования, а второйвыход подключен к управляющим входам ключей, первый из которых включен между вторым входом второго и выходом первого блоков суммирования, первый вход первого блока суммирования и его выход являются соответственно входом и первым аналоговым выходом сумматора, о т л и ч а ю щ и й с я тем, что, с целью повышения точности, второй ключ включен между вторым входом первого и выходом второго блоков суммирования, третий вход первого блока суммирования соединен с первым выходом порогового блока и с цифровым выходом суммато- ра, второй вход порогового блока подключен к выходу первого блока сум-мирования, первый вход которого соединен с третьим входом второго блока суммирования, подключенного выходом к второму аналоговому выходу. сумматора,Изобретение относится к автоматике и измерительной технике и может быть использовано при построенчи аналого-цифровых систем.Известен аналого-дискретный сумматор, содержащий два аналоговым 5сумматора и пороговый элемент (1).Недостатком такого сумматораявляется низкая имность при суьввровании быстюменяющихся сигналовиз-за переходных процессов, возникающих з сумматорах при скачкахнапряжения на вычитающих входах;Наиболее близким техническимрешением к данному изобретению является устройство (2, содержащее . 15первый и второй блоки суммирования, пороговый блок, выход которого соединен с первым входом второгоблока суммирования, два ключа,информационные входы которых подключены соответственно к входу аналого-дискретного сумматора и к выходу первого блока суммирования,выходы ключей соединены соответственно с вторым и третьим входамивторого блока суммирования, управляющие входы ключей соединены с вторымвыходом порогового блока.Недостаток известного устройства -невысокая точность.Цель изобретения в , повышение точности суммирования.Поставленная цель достигаетсятем, чго в аналого-дискретном сумматоре, содержащем первый и второй блоки суммирования, первый и второй клю-З 5чи и пороговый блок, первые вход ивыход которого соединены соответственно с выходом и с первым входомвторого блока суммирования, а второйвыход подключен к управляющим входам 40ключей, первый из которых включенмежду вторым входом второго и выходомпервого блоков суммирования, первыйвход первого блока суммирования иего выход являются соответственно увходом и первым аналоговым выходомсумматора, второй ключ включен междувторым входом первого и выходом второго блоков суммирования, третийВход первого блока суммирования соединен с первым выходом пороговогоблока,и с цифровым выходом сумматора, второй вход порогового блокаподключен к выходу первого блокасуммирования, первый вход которогосоединен с третьим входом второгоблока суммирования, подключенноговыходом к второму аналоговому выходусумматора,На фиг. 1 представлена схема аналого-дискретного сумматора; на 60фиг. 2 - функциональная схема порогового блока.Приведенные схемы содержат первыйи второй блоки суммирования 1 и 2,пороговый блок 3, ключи 4-7, компа раторы 8 и 9, тактовый генератор 10, реверсивный счетчик 11, преобразователь кода в напряжение (ПКН) 12.Принцип действия следующий.Пусть сумма входных сигналов х аналого-дискретного сумматора есть х= Й х;, тогда если выполняется соотношение-х ххто ключ 5 закрыт, а ключ 4 открыт сигналами с порогового блока 3, на первом входе блока суммирования 2 и на третьем входе блока суммирования 1 действует сигнал С О.Выходные сигналы блоков суммирования 1 и 2 определяют соответственно соотношениямигде к( - коэФФициент передачи суммирующих блеков 1 и 2 длявходного сигнала х,к - коэффициент передачи блогка суммирования 1 и 2 повторым Входам;у 1 И У 2 - выходные сигналы блоков 1и 2 соответственно.При х, й х ы Зх, пороговый блок 3держит:. ключ 4 закрытым, а ключ 5открытым и задает по третьему входуна блок суммирования 1, а также по .первому входу на блок суммирования 2сигнал сВыходные сигналы блоков суммирования 1 и 2 определяются при этомследующими соотношениями:у, = ),х + ) у + с,у:),х + с. (2),В общем случае при шх 4 с х 4 Ьх, при=-2, Ь=в+2 справедливы соотношег=нияурух+у = Ех - 2 у + сд (3) где р = 1, с 1 = 2, если и= - четноер = 2, ц = 1, если и йечетное.с=-.2 пЕх, - сигнал, задаваемый с порогового блока 3 в блоки суммирования 1 и 2. Значения суммы аналоговых сигналов х в любой момент времени представляется на выходе сумматора значениями аналоговых сигналов уи у и дискретным сигналом с, как это следует из соотношения (3).Наиболее просто результат суммирования входных сигналов может быть представлен в аналоговой форме разностью сигналов на выходах ключей 5, 4 или б, 7 с сигналом с, так как напряжение на выходе открытого ключа 5(4) или б(7) всегда равно )с х 2 п)сх Если хх прок г то результат суммирования кх с доета1095194 сРиг. 3тавитель А.Масловред Л.Микеш Корректор О.Тиг Редактор В.Коэ Тираж 699осударственногам изобретений Москва, Ж,ПодлСССРйнаб., д аказ ЗбОО ВНИИ ПИ по д 113035комите и откры Раушска 4/ ППП Патент, г, Ужгород, ул. Проектн или точной точностью представляется квантованной величиной ся или соответствующим ей кодом, формируемым реверсивным счетчиком 11 порогового блока 3Пороговый блок 3 действует следующим образом.Пусть входной сигнал х возрастает от О, тогда при хх с=О, ключ 7 открыт, б закрыт сигналом с выхода младшего разряда счетчика 11, 10При х=х срабатывает компаратор 8, порог срабатывания которого Е=Ех, в результате на суммирующем входе счетчика 11 появляется сигнал ф 1, разрешающий изменения состояния 5 счетчика 11 под действием тактовых импульсов генератора 10. Тактовый импульс устанавливает счетчик 11 в состояние Б=,при этом с выхода ПКН 12 на входы суммирующих блоков 1, 2 поступает сигнал с, одновременно ключ 7 закроется, ключ б откроется, йапряжение на входе компаратора 8 станет. меньше Е, поэтому на .выходе компаратора 8 появится фОф, изменение состояния счетчика 11 прекращается. При увеличении х до.Зх вновь сработает компаратор 8, так как напряжение с выхода суммирующего блока 2 через открытый ключ б поступает на его вход. Счетчик 11 устанавливается э новое состояние Б.=2, сигнал с с выхода ПКН поступает на входы блоков суммирования 1, 2, э результате входной сигнал компаратора 8 станет маньше Е. При И=2 ключ б закрыт, а ключ 7 открыт.При уменьшении х, например, от хЗх, до х = Зх напряжение на входе компараторов достигает значе 1 ния Е=-1,х поэтому срабатывает компаратор 9, В результате счетчик 11 переводится э режим вычитания,при котором первый тактовый импульс приводит ецио в состояние 0=1 что вызывает изменение сигнала с выхода ПКН 12 и сигнала на входе компаратора 9. Сигнал на выходе компаратора 9 принимает значение 0 ф, поэтому состояние счетчика 11 фиксируется при В=1.Дальнейшее уменьшение или увеличение х вызывает изменения э состояниях элементов схемы, аналогичные рассмотренным выше, т.е. четным значениям Н, вафик нрованным в счетчике 11, соответ;твуют закрытые ключи 5, б и открытые ключи 4, 7, а нечетным значениям Н - закрытые ключи 4, 7 и открытые 5, б.Так.как ключи 7, б подключают входы компараторов 8, 9 только к тому блоку суммирования, который формирует разность суммы входных сигналов х и компенсирующего сигнала с, то режим работы порогового блока совместно с остальной схемой аналого-дискретного сумматора соответствует режиму работы АЦП следящего уравновешивания.Увеличивая число разрядов счетчика 11 и ПКН 2, можно при неизменной зоне линейности блоков суммирования 1, 2 обеспечить расширение рабочего диапазона х э сотни раз, сохраняя при этом высокую точность и чувствительность устройства. Отсутствие ключей, включаемых последовательно с источниками входных сигналов упрощает использование предлохенного устройства при большом числе входных сигналоэ х, повышает точность его за счет исключения погрешностей, обусловленных токами утечек нескольких входных ключей или взаимовлиянием источников при подключении их через общий входной ключ.

СмотретьЗаявка

3561713, 05.03.1983

КУЙБЫШЕВСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. В. КУЙБЫШЕВА

КОСОЛАПОВ АЛЕКСАНДР МИХАЙЛОВИЧ

МПК / Метки

МПК: G06G 7/14

Метки: аналого-дискретный, сумматор

Опубликовано: 30.05.1984

Код ссылки

<a href="https://patents.su/3-1095194-analogo-diskretnyjj-summator.html" target="_blank" rel="follow" title="База патентов СССР">Аналого-дискретный сумматор</a>

Предыдущий патент: Вычислительный прибор

Следующий патент: Множительно-делительное устройство

Случайный патент: Автобетоновоз