Устройство для обнаружения и исправления ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

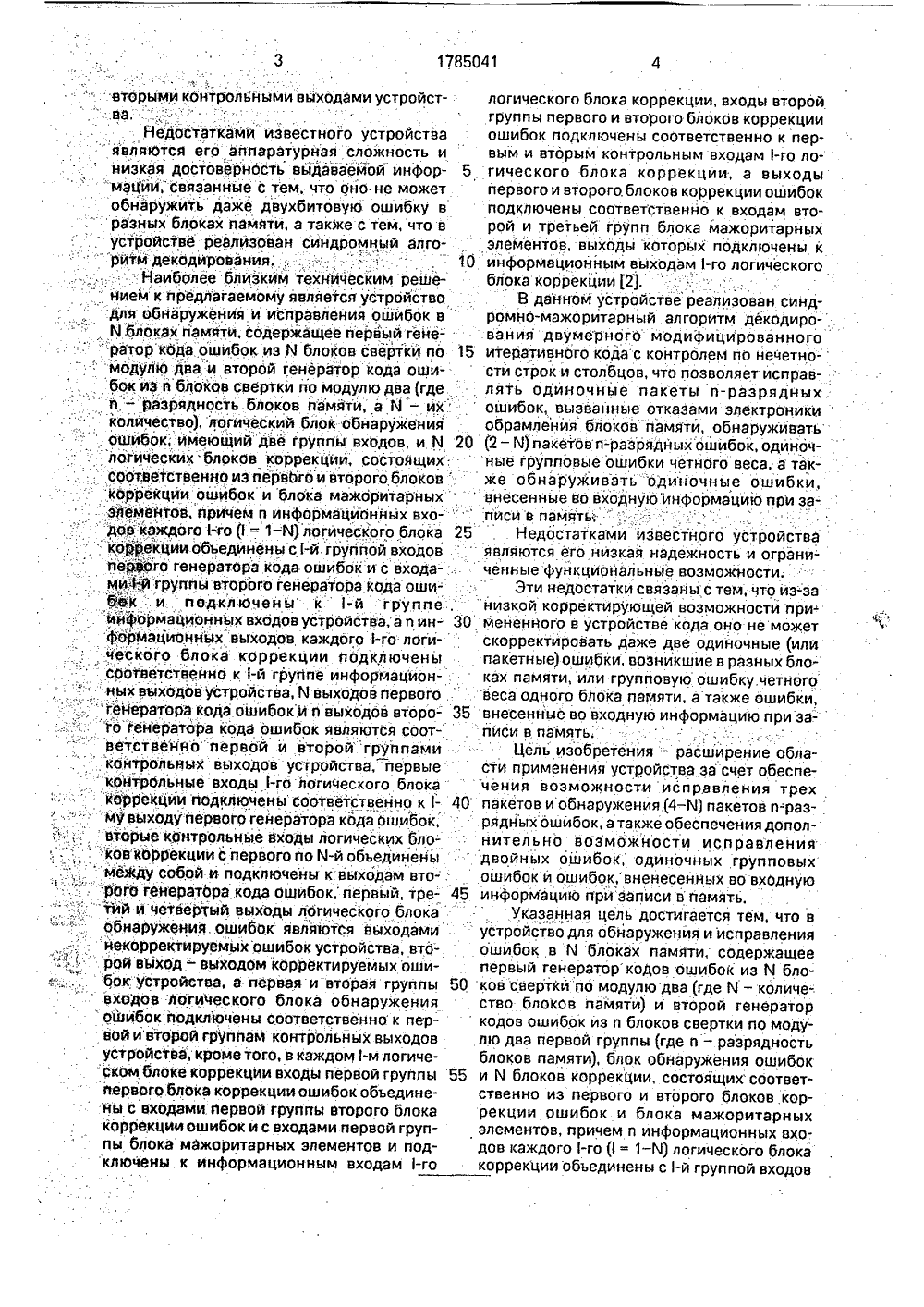

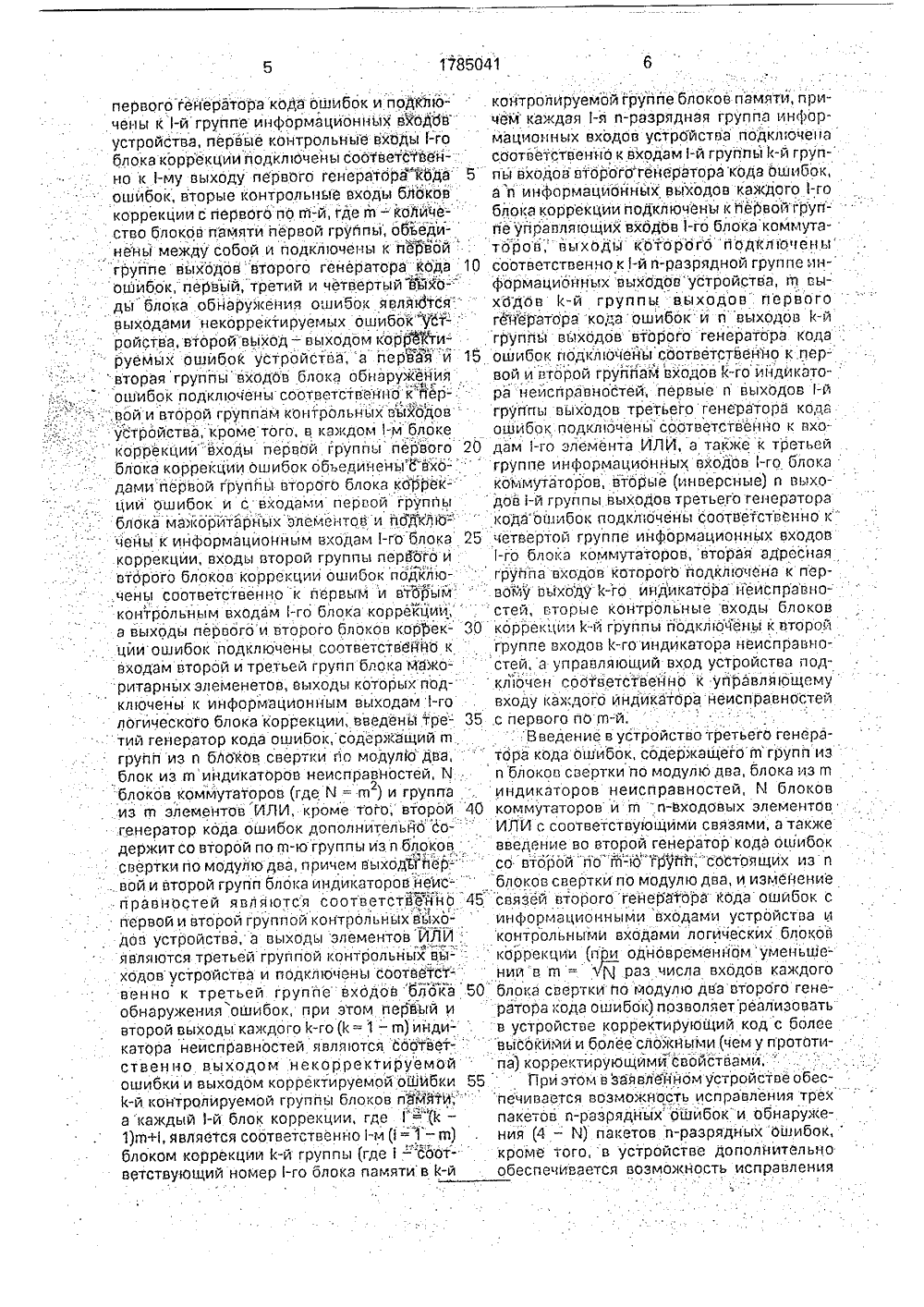

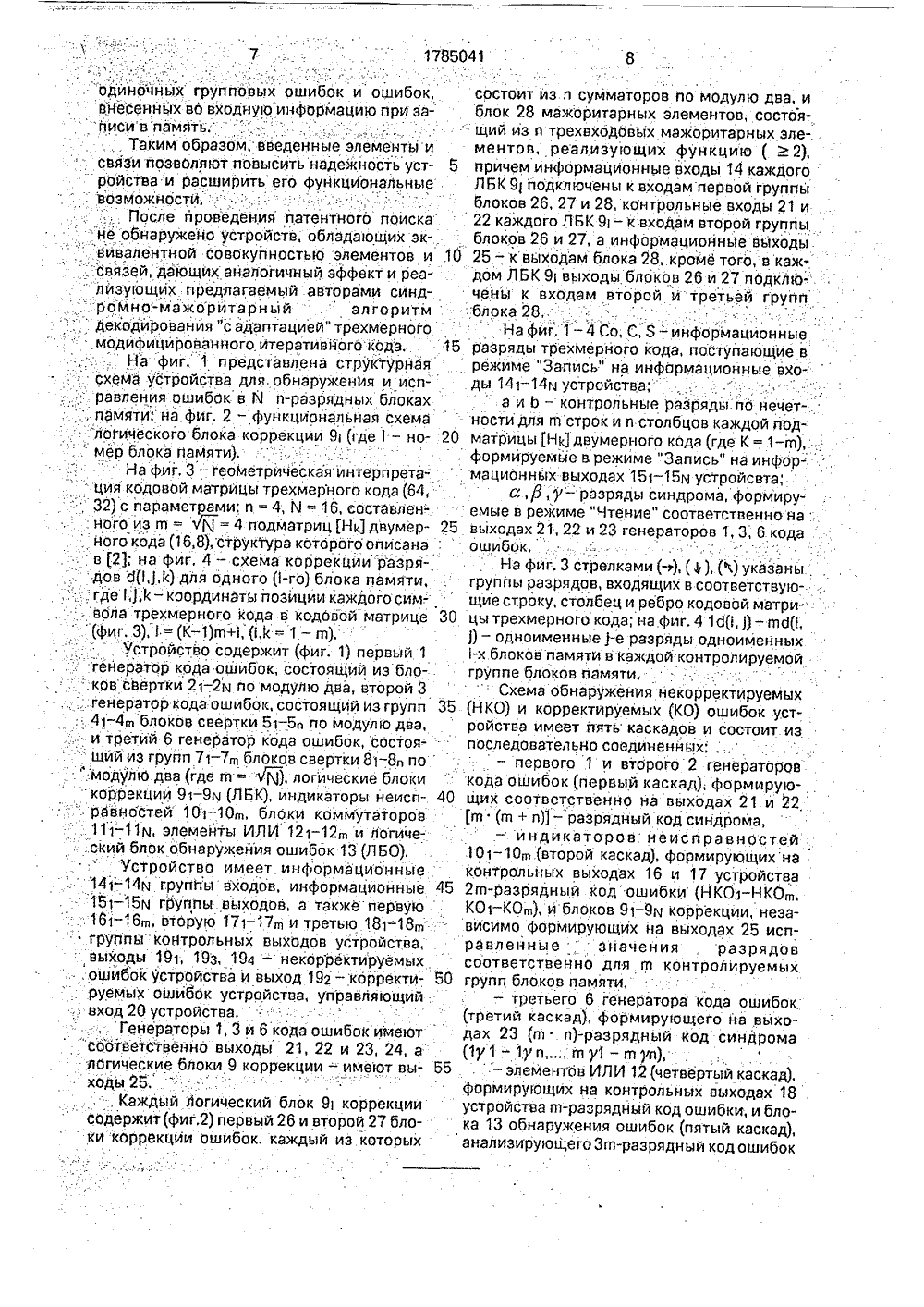

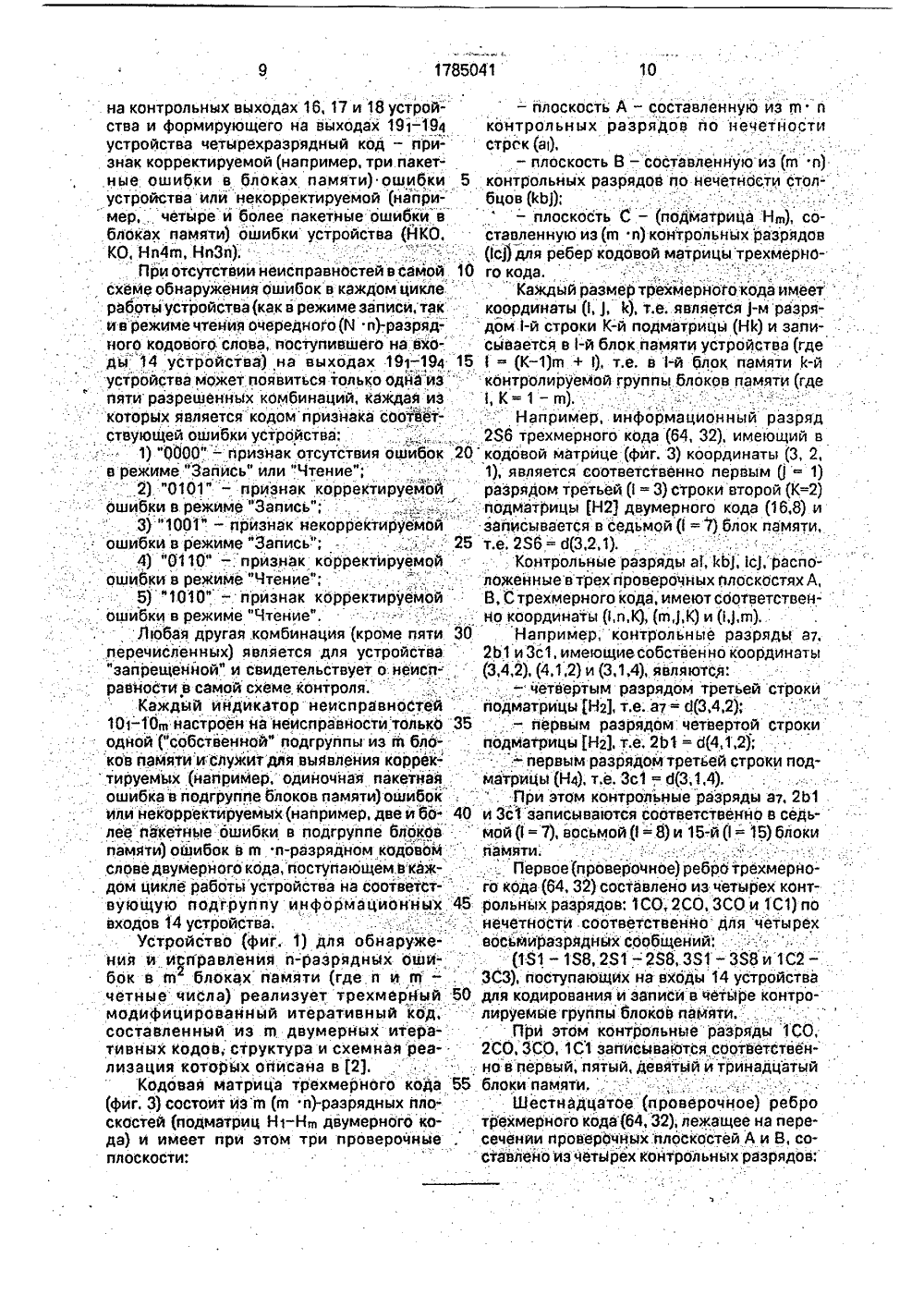

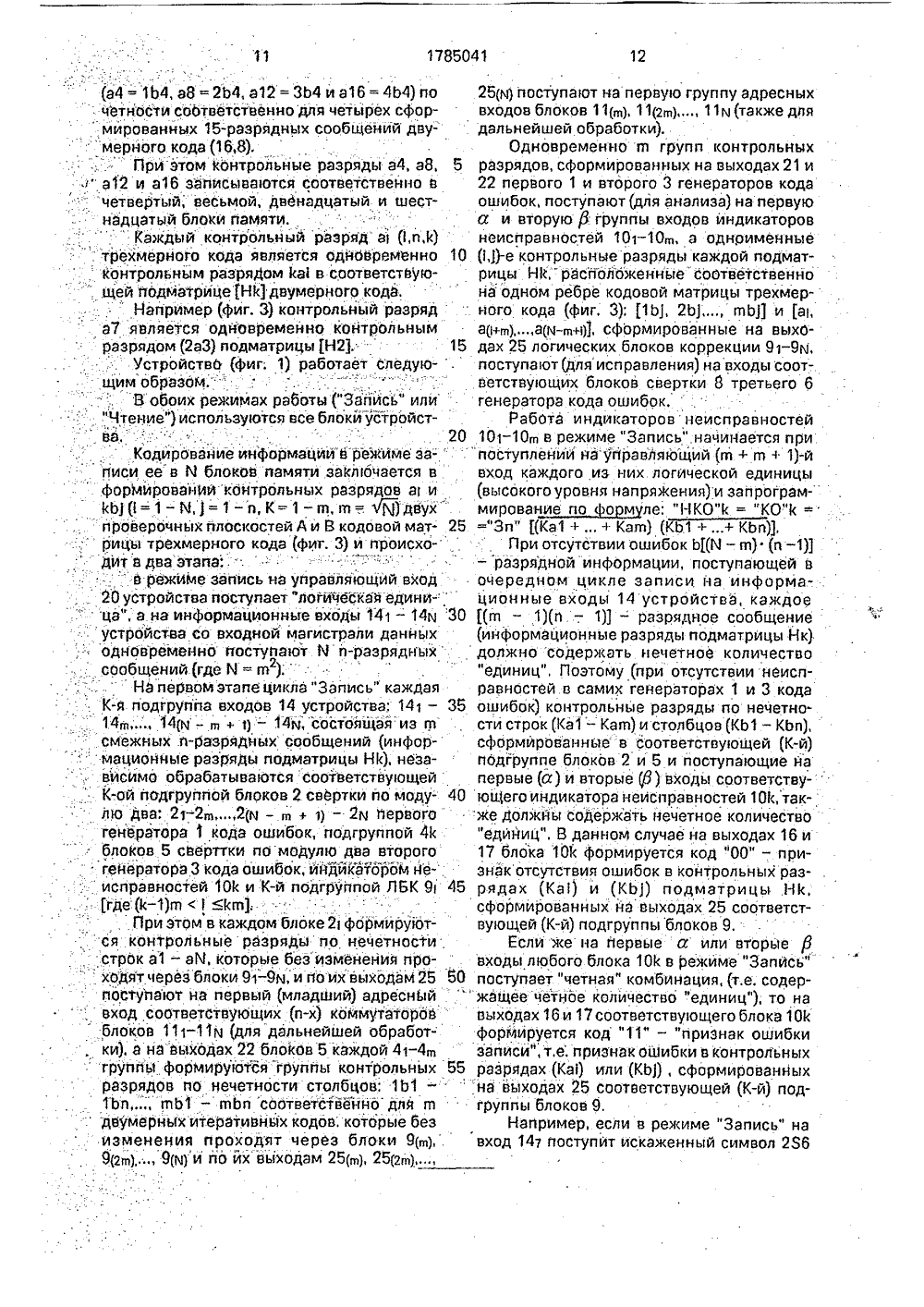

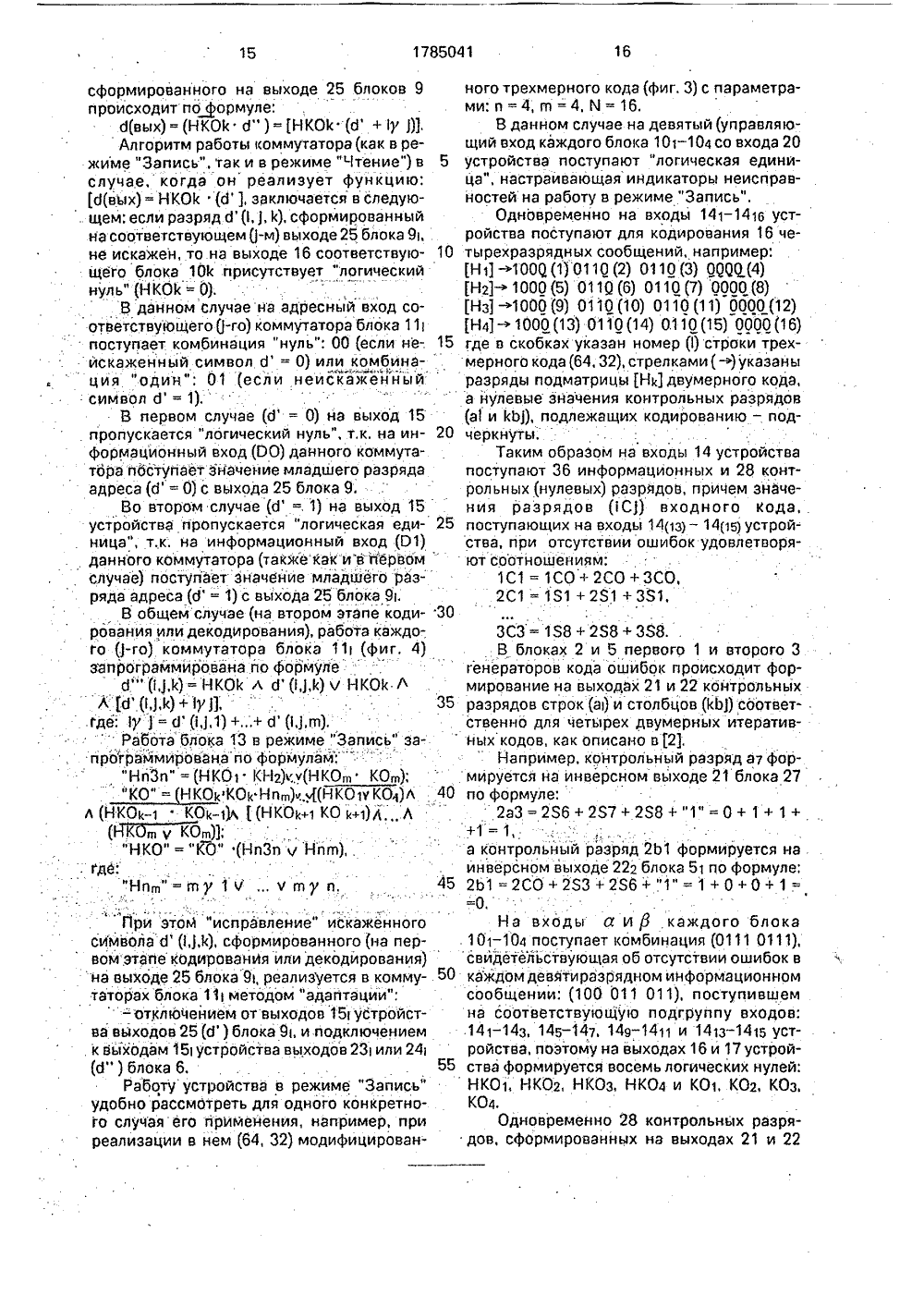

(5 ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕВЕДОМСТВО СССРГОСПАТЕНТ ССР) Ц ) БРЕТЕН(21) 4854339/24 .:" :.повых й пакетных ошибок в блоках памяти, (22) 07.06.90 Целью изобретения является -раСширение (46) 30.12,92. Бюл. М 48области примененияустройства за счет ис- (71)Научно-производственноеобьединение-правления трех пакеТов и обнаружения И "Агат" " пакетов и-разрядных ошйбок, Устройство (72)А.А.ВоловникиА.Б,Савинова : рМяобнаруженияиисправленияошибоксо- (56) 1, Авторское свидетельство СССРдержит первый генератЬр кодов ошибок, со- . М 1070605, кл, 8 11 С 29/00, 1984.: : .; стоящий из блоков Свертки по модулюдва,2. Авторское свидетельство СССР: второй генератор кодов ошибок, состоящйй М 1525746, кл, 8 11 С 29/00, 1988. из групйблоков сверткйпо модулю два, и (54)УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ И третий генератор кодов ошибок, состоящий ИСПРАВЛЕНИЯ ОШИБОК .., из групп блоков свертки по модулю два, (57) Изобретение относится к вычислитель- блоки коррекции, индйкаторы неисправноной технике и может быть использовано для . стей, блокикоммутаторов, элементы ИЛИ и обнаружения и исправления двойных, груп- блок обнаружения ошибок. 4 ил.Ф Изобретение относится к вычислитель- (2 п+1)-входовых ийдикаторов неисправноной технике и может быть использовано в стей подключены к выходам (и М)-входовокачестве устройства для обнаруженияи исго генератора кода ошибок и к одним из правленйя двойнцх, групповых и пакетйых входов элементов И, другие входы которых ошибок в блоках памяти. " .: соединены с выходами (2 п+1)-входовых индикаторов неисправностей, а"выходй элеИзвестно устройство для исправления ментов И подключены ко вторымвходам ошибок в блоках памяти Я, содержащее блока коррекции ошибок, выходы которого (и й)-входовцй генератор кода ошибок (где . являются выходами устройства, одни из вхои - разрядность блоков памяти, а И - их дов двухвходовцх сумматоров по "модулю количество), блбк коррекции ошибок, зле-два соединены с первйми вйходами (и й)- менты И и оп+1)-входовых индикаторов входового генератора кода ошибок, другие неисправностей, Й двухвходовцх суммато- входы двухвходовых сумматоров по модулю ров по модулю два и (и+1)-входовый два и один из входов(п+1)-входового сумма- сумматор по модулю два, причем входц тора по модулю два подключены к другим (и й)-входового генератора кода ошибок выходам (и И)-входового генератора кода подключены к первым входам блока коррек- ошибок, а выходы двухвходовыхсумматоцииошибокиявляютсявходамиустройства, ров по модулю два подключены к другим а й первых выходов (и й)-входового гене- входам (п+1)-входового сумматора по модураторакодаошибокявляютсяпервымикой- лю два и являются совместно с выходом трольными выходами устройства, входы(и+1)-входового сумматора по модулю два2019На контрольном выходе 162 устройства На выходе 18 блока 124 формируется формируется "логическая единица", посту-"логическая единица" по формуле: йающая на старший адреснйй вход сети со- Нпа = 4 у 14 у 2 4 у 3 4 у 4= ответствующих коммутаторов блоков - 1 иОЮ 0 = 1, а на выходе 19 устройства 11 ьэ, пропуская на выходы 15 (повходам 5, формируется код "0101" - корректируемой 03 и 04 коммутаторов) исправленные (на ошибки "Записи", разрещающий запись в втором этапе кодирования) значения конт- память 64-разрядного кодового слова с одрольных разрядов подматрицы Й 2, сформи- ним ошибочным 236 и двумя исправленныровайные на выходах 23 и 24 блока 6 ми а 7 и 2 Ь 1 сймволами.Так как на четвертом выходе 25 блока 97 10 На этомцикл "Запись" заканчивается. формируется искаженный (1 - 0) символ Запись в памятькодового слова только (аЯ, а напервом выходе 25 блока 98 форми- с одним ошибочным символом является корруется искаженный(0 - 1)символ(2 Ь 1),торектируемой ошйбкой устройства, йсйравйа" четвертом выходе 23 з и первом выходе ляемой в режиме "Чтение". 23 д блока 6 формируются две "логические 15 Необходимость исправления (методом единицы" по формулам: Зу 4 = аЗ+ а 7+ адаптации) двух контрольных разрядов (а) . +а 11+ а 15 = 1+0+ 1+1 = 1:;: 4 у 1=1 Ь 1+ и (кЬ, неправильно сформированных на + 2 Ь 1 + ЗЬ 1+ 4 Ь 1 - О + 1 + 0 + О - 1, а на выходах 25 блоков 9 (на первом этапе цикла выходе 15 устройства формируются семь" "Запись" ), обьясняется необходимостью изкбнтрольных разрядов подматрицы Й с ис бавления от трехбитовой ошибки типа: 236, йравленным(О -ф 1) символом"а 7 и"исправ- а 7, 2 Ь 1 некорректируемой конфигурации ленным (1 - 0) символом 2 Ь 1 по. формулам; (т,е. некорректируемой врежиме "Чтейие"), а 5(вых) = а 5+ Гу 4 = а 5+ О - а 5Ошибочный же информационный сймвол а 6(вых)-а 6+ 2 у 4 = а 6+ О=а 6 входного кода, например 236, методом а 7(вых) = а 7+ Зу 4 = а 7+ 1 = а 7:25 "адаптации"в режиме "Запись" исправить 2 Ь 1(вых) = 2 Ь 1+ 4 у 1 = 2 Ь 1+1: 2 Ь"1 нельзя (в отличие от режима "Чтение" ). 2 Ь 2(вых).= 2 Ь 2+ 4 у 2 = 2 Ь 2+ О = 2 Ь 2 И, наконец, рассмотрим случаи некор ЬЗ(вых) = 2 ЬЗ+ 4 у 3 = 2 ЬЗ+0 = 2 ЬЗректируемой ошибки "Записи", найример, а 8(вых) = а 8+ 4 у 4 - а 8+ 0- а 8двухбитовой ошибки "Записи", обйаруживаИсправление двух контрольных разрядов; 30 емой в режиме "Запись" или "Чтение", При а 7 и 2 Ь 1 нэ втором этапе кодирования мето- поступлении на входы 14 устройства двух дом адаптации происходит следующим об- ошибочных информационных символов, разом: - ;:;. :,:.;: Расположеннйх в разных подматрицахНа адресные входы четвертого коммутэ-трехмерного кода; например символа 238 тора блока 11 т поступает комбинация "два" 35 подматрицы Н 2 и символа 336 лодматрицы (10), поэтому на выход 15 т устройства по Нз, на выходах 16 устройства сформируется информационному входу 02 коммутатора две лбгйческие единицы: НКО 2 и НКОз, поэпроходит значение: Зу 4 = 1, т.е, йсйравлен-. тому навыходе 19 устройства сформируется ное (О - 1) значение символа а 7. а на адрес- . код "1001" - некорректируемой ошибки "Заные входы первого коммутатора блока 11 э 40 писи",иработаустройства прерывается. поступаеткомбийэцйя "три" (11),йоэтомуна . Припоступлениинавходы 14 устройствыход 15 а устройства по информационному ва двух ошибочных символов, расположен- ОЗ входукоммутатора проходитзначение ных в одной строке кодовой матрицы, . 4 у 1 = 0 с выхода 24 блока 6, т,е; исправлен- . например, символов 236 и 237 подматрицы ное (1 -ф 0) значение символа 2 Ь 1, в резуль 45 Нъ на выходах 16 и 17 устройства сформи.тате окончательно сформированное на Руются "логические нули", но на выходах 25 входах 145-14 эи выходах 15 яэустройст- . блока 9 а неправильно сформируются два ва 16-разрядное кодовое слово подматрицы контРольных разряда; 2 Ь 1 и 2 Ь 2, поэтому на Нр содержит только один искаженный сим-,выходах 234 и СлЕДоватЕлЬнО на выходе 184вол: 236 (на входе 147) и два исправленных 50 Устройства сформируются "логические едиметодом "адаптации" символа: ат и 2 Ь 1 (на ницы: 4 у 1, 4 у 2 и Нюц, а нв входы ЛБО 12 выходах 15 т и 15 в), и имеет следующий вид поступит "запрещенная:" комбинация(несо- (подчеркнут искаженный символ 236): ответствующая отсутствию ошибок или корректируемой ошибке "Записи" ); 55 ОООО ОООО 1. где знакозначает, что значение на выходах 18, 182 и 18 з устройства (т.е. кроме значения Нп на выходе 184 устройства) -1785041 дах 2 первой группы скорректированных вильно сформируются два контрольных разряда: (а 6) и (а 7), которые без измененияпоступят (на втором этапе кодирования) на 15 значений 1 Д . сГ (1,1,К) -сГ (1,п,1) каждогоблока памяти,выходы 15 устройства, а на выходе 19 уст- В индикаторах неисправностей ройства сформируется код "ОООО" - признак10- 10 сп (независимо друг от" друга) происотсутствия ошибкй, в результате чего 64- разрядное кодовое слово с четырехбитовой ходит обнаружениенекорректируемых (возникновение 2 - гп пакетов и-разрядных ошибкой в разрядах; 253; 236, а 6 и а 7 будет 20 ошибок) или кофректируемых ошибок (возникновение только одного пакета ошибок) в каждой из т = Я контролируемой группе записано по входам 14 и выходам 15 устройства в блоки памяти как безошибочное коблоков памяги, и формирование (на выходовое слово Такаядвухбитовая ошибка "Зайиси".(ти- дах 16 и 17) признаков некорректируемой па 253 и 256) является необнаруживаемой 25 НКОс-НКО и и корректируемой КО - КОсп ошибкой в режиме "Запись", но при этом ошйбки в соответствующей подгруппе блоявляется обнаруживаемой ошибкой устрой- ков памяти.ства, т.к, двухбитовая ошибка "Записи" дан-..Одновременно в блоках свертки 8 по ной конфигурации гара.нтированно модулю два третьего 6 генератора кода оши 30 обнаружится в режиме "Чтение" (см. случай бок - проверкой на четность и нечетность.четьсрежбитовой ошибки в описании работы "Чтение" ),Таким образом, как было показано, модифицированная структура примененного в каждого ребра кодовой матрицы (фиг, 3) - формируется(на прямых 23 и инверсных 24 выходах блоков 8) третья группа разрядов синдрома: ( уи ( у, которая одновременустройстве кода, а также синдромно-мажоно является второй группой скорректироритарный алгоритм кодирования с адапта-: ванных значений 1 Д": сГ(Ц,Е)+ у) каждогоцией на втором шаге (и,.правлением двух блока памяти,контрольных разрядов, сформированных на. На этом йервьсй этап декодированиязапервом шаге), позволяет гарантированно канчивается: в конце первого этапа цикла 40 исправлять в устройстве одиночные ошибки"Чтение" (фиг. 4)на первые адресные входы и обнаруживать двойные ошибки, внесенные в кодовое слово при "Записи",В режиме "Чтение" в устройстве реализуется синдромно-мажоритарный алгоритмдекодирования с адаптацией, что позволяет 45 каждого коммутатора блока 11 поступает первая группа скорректированных значений: 1 Д 1-го блока памяти (с выхода 25 блока 9 с), на вторые адресные входьс - признак НКОк (с выхода 16 блока 101 с), а на устройству исправлять три пакета и-разряд- третьи 02 и четвертые 03 информационные ных ошибок (при независимом их возникно- . входы - поступает вторая группа скоррективениив любых трех из К блоков памяти), а ровэнных значений: 1 Д" 1-го блока памяти(с также обнаруживать (4-М) пакета и-разряд-выходов 23; и 24 с блока 6),ных ошибок и трех-четырехбиговые (непа На втором этапе цикла "Чтение" исполькетн ые) ошибки.Декодирование информации в режиме"Чтение" происходит в два этапа,зуются блоки 11, 12 и 13. .В коммутаторах-корректорах блоков 111-11 и происходит исправление "некорНа первом этайе на управляющий вход ректируемой" ошибки каждого из й блоков 20 устройства поступает "логический нуль", перестраивающий индикаторы неисправностей 10 на работу в режиме "Чтение" и разрешающий считывание (И и)-разрядной информации из К блоков памяти на входы памяти (который при этом является 1-м блоком памяти К-й контролируемой группы блоков памяти) и формирование (на выходах 15 г 15 гс устройства) третьей группы окончадля блока 13 в режиме "Запись" безразлич-14 сч устройства. На первом этапе деконо, дирования трехмерйого кода используютсяСогласно логике работы блока 13, на блоки 1, 3. 6, 9 и 10, В блоках свертки по выходе 19 устройства формируется "запре- модулю два 2 и 5 (соответственно перво- щенная" комбинация "1000", и работа уст- го 1 и второго 3 генераторов кода оширойства прерывается. 5 бок) - проверкой на нечетность каждойПри поступлении навходы 14 устройст- строки и каждого столбца кодовой матрива двух ошибочных символов, расположен- цы (фйг. 3) - формируются (на выходах 21 и ных в разных строках одной подматрицы 22) первая и вторая группы разрядов синд- трехмерногокода; например, символов 233 рома: ас и кр).и 256 подматрицы Н 2, на выходах 16, 17 и 10 - В блоках о 1 - 9 сч происходит исправле устройства сформируются логические ние одиночной пакетной ошйбки каждого из нули, на выходах 25 блоков 9 о й 97 непра-: И блоков памяти и формирование на выхо- .тельйо скорректированных значений го мажоритарного элемента 28 с первыми, 1 Д(вых) - МД(вых) по формулам:- считанными из памяти значениями с(,),)Д(вых) =(НКОЛД)(НКО Д"), входа 14 устройства.гдеД:(сГ (,1,) - сГ (;и,) - первая группа Таким образом, при отсутствии ошибок скорректированных значений 1-го блока 5 вК-йконтролируемойгруппеблоковпамяти памяти, сформированная на выходах 25 на входы каждого мажоритарного элемента блока 9;:. ., " .: 28 - 28 л блока 9 поступают три одинаковыхД ", (сГ (,),) + у Д - вторая группа значения; 000 или 111, поэтому значения скоррекгированных значений 1-.го блока пэ- сГ(ц,) каждого разряда на выходе 25 блока мяти, сформированная на выходах 23 г 24 10 91 совпадаютсо значениями с(Ц ) разрядов третьего 6 генератора кода ошибок; входа 14 устройства".- гНКО" -признакнекорректируемой 1 Д = 1 Д(вх) НКОк КОк.ошибки К-ой контролируемой группы бло- Одновременно на выходах 16 и 17 кажковпамяти(логическая единица),сформиро- дого блока 101 формируется два логичеванный на выходе 16 блока 10,: "15 ских нуля: НК 01 и Кг.Й, т,е, формируетсяД(вых): (сГ" (,1,) - сГ "(1,и,) -третья код "ОО" - признак отсутствия ошибок в К-й группа скорректированных значений 1-го контролируемой группе блоков памяти, по- блока памяти, сформированная нэ выходах этому значения сГ" (Ц,1) камдого разряда на 15 блока 11; .:"., -.:.: выходе 15 блока 11 совпэдаютсо значени(у 3) = сГ (Ц,1) + .;, + сГ (гЦ,гп).20 ями разрядов сГ (Ц,1) на выходе 25 блока 9, В блоке 13 происходит анализ Згп - раз- т.е. со значениями. разрядов с(1 Щ на входе рядного кода ошибки, сформированного на14 устройства; 1 Д(вых) = 1 Д(вх) НКОс КО,кбйтрольных выходах 16,17 и 18 устройства,Если в каждой из гп контролируемой иформирование навыходах 19-194 устрой-группе блоков памяти независимо возникаства четырехразрядного кода "0110" или 25 ютодиночныеошибкиилиодиночныепаке- "1010" - -признаков корректируемой или не- ты ошибок типа "и нулей", или "и единиц" корректируемой ошибки устройства в режи- (возникновение 1 - гп пакетов ошибок одноме "Чтение", ;.: : .":временно в разнЬгх контролируемых групВ конце цикла."Чтение" (после форми- пэх блоков памяти является для устройства рования на выходе 19 устройствапризнака ЗО корректируемой ошибкой), то на гисоответотсутствия ошибок "0000" или "0110". - ствующих вьгходах 21 первого генератора признака корректируемой ошибки"уст- кодаошибокпоявляетсяунитэрный код,со-ройства в режиме "Чтение" ) скорректи- держащий одну единицу(а) и(ги - 1) нулей, рова нная (М и)-разрядная информация а на и соответствующих вьгходах 22 вторОго считывается с выходов 15 устрбйства на вы- З 5 генератора кода ошибок появляется код, ходную магистральданньгх,:"содержащий нечетйое количество "едиНэ этом очередной цикл "Чтение" за- ниц" Я 3 и нечетное количество нулей. В :канчивается, ":. :;.;.;:,. ":.-.:". результате на К-й группе выходов 21 и К-йНа первом этапе декодирования в кэж- групйе выходов 221. первого и второго генедом блоКе 9 Реализуется синдромнб-"мажо раторов кода ошибок, где 1 = ( - 1)гп + 1, ритарный элгорйтм декодирования формируется (ги + и)-разрядньгй синдром, разрядов 1-го блока памяти, Данный элго- содержащийчетное количество единиц(а, ритм"заключается в следующем: при отсут-Р Я и четное количество нулей, (располоствии ошибок в и,ги разрядахинформэцйи, женных на определенных позициях), посту- считаннойизгп блоков памяти К-й койтро пагощий одновременно в блок 9 и 101,.лйруемой группы блоков памяти, информа поэтому второе итретье значения: )Ц,)+ цияпроходит со входа 14 устройства: 1 Д(вх) + а 1 и (Ц,) + р Д каждого искаженного на выход 25 блока 9: 1 Д без изменения, символа входа 14 устройства, сформиротак как на гй соответствующих выходах ванные в блоках 26 и 27 блока 9 будут 21 первого гейератора кода ошибок, где 50 равны его инверсному значению: с(Ц,).(К - 1)ги (Ы гп; и на и соответствующих Таким образом, при возникновении выходах 221 второго генератора кода одийочной (корректируемой) пакетной ошибок, формируется "нулевой" (гп + и)- ошйбки в К-йконтролируемой группе блоразрядный синдром, поступающий одно- ков памяти, на входы соответствующих мавременно в блоки 9 и 101, поэтомУ 55 жоритарных элементов 28 - 28 блока 9 второе и третье значения: ,),) + а ) и поступает комбинация 011 или 100, т,е. одно 1 с(Ц,) +р)1 каждого сигнала входа 14искаженное(Оили 1)идваисправленньгх(11 устройства,"сформированные в блоках 26или 00) значения символа с(Ц,) входа 14 и 27 блока 9, совпадают на входе каждо- устройства, формируя на соответствующихвыходах 25 блока 9 инверсные(т.е, исправ- В элементах ИЛИ.121 - 12 п происходит ленные) значения искаженных разрядов 3-го формирование (на контрольных выходах 18 блока. памяти. устройства) признаков неисправностей НпСиндромно-мажоритарный алгоритм для каждой 3-й группы выходов 25 блоков 9 декодирования в каждой ЛБК 93 - 9 м реали- - по формулам; зуется методом "голосования" в мажоритар Нп =у 1 ч 3 у 2 чч 3 у и, ных элементах 281 - 28 по формулам:где 3 у) - соответствующие значения разряб (Ц,3 с) = б(Ц,3 с) . с 3(Ц,3) + сцчб(3 фс) Л дов синдрома, сформированные на выходах Лс 3(Ц,3 с)+ 3 ф Й ч с 3(Ц,3 с) + сц 3 д(Ц,3 с)+ 3 сЩ 233 блока 6).Например, при искажении первого раз- Работа ЛБО 13 в режиме "Чтейиен заряда информация третьего блока памяти 10 прогоаммиоовансапобоомулам: второй контролируемой группы блоков па- .мНп 4 уи=ИНК 01+ КО)у(НКОП,+ КОмяти(т.е. символа 2 убседьмогоблока пяамя- "КОи =(К 01 , чКОд) (НК 1 чч.(256)=236 4 (256+ а 7 с/ 236 Л 15 НКОпт); Л(236+ 2 Р 1 Щ(236 + ат )(236+ 2 Р 1иНКО" ="КО". (мНп 4 п" чНп 3)При возникновенииодиночной(коррека, Из этих Формул видно, чтов режиме тируемой) пакетной ошибки в 3-м блоке па-:, "Чтение" на йыходахс 19 устройства могут мяти (т,е, в 3-м блоке памяти К-йпоявиться только две мразрешенные" ком.контролируемой группы блоков памяти),на 20 бинации: м 0110 м (признак корректируемой выходах 16 и 17 блока 10 с появляетсякод:ошибки ус 1 Ройства) или "1010 и (некорректим 01 м (признак корректируемой ошибки К-й руемой ошибкиустройства), Появление люконтролируемой группы блоков памяти) йо бой другой "ненулевой" комбинации .формулам . -: - расценивается как "запрещенная", т е, сви"КОя" = пЗл"и Ка) Ка 1, Ка ) 25 леутельсттвуето неисправности в самса схем Ка(;+1)ччКаа ); ме контроля, . д(Кф 1+ Кф 2+;, + Кр и); .;.-: Таким образом, корректируемотй ошибиНКОси = (м 3 пн) (нКО,") (К а 1 ч, / кой в устройстве в режиме "Чтение" являетчл Кащ/КРМчКрп),ся: возникновение одиночных пакетныхЭта формула означает,что код н 01" (кор ошибок (КОК) в каждой подгруппе из т блоректируемой ошибки) формируется на выхо- ков памяти, куторьен независимо исправля- . . дах 16 и 17 блока 101 при поступлейии на .ются в блоках.91 - 9 р, или возникновение его первые е входов только одного едиййч- - некоРРектиРуемой ошибки (Н КОс) в одной ного символла Ф и поступлении на его вто- из и подгрупп блоков памяти (например, рые и входов нечетного количества 35 возникновение несколькихпакетныхошиединичных симводов 3 В), а код "10" (при- бок или гРУпповых ошибок четного веса), знак некорректируемой ошибки К-й контро-:. которая исправляется в- соответствующих лируемой группы блоков памяти) -: блоках коммутаторов 11 методбм "адаптаформируется при появлении двух и более" ции:откл 1 очейиемотвыхода 15 устройства. 40 выходов 25 блока 9 иподключением к выхо(Ка,1-Кап 1 ), или четного количества. ДУ 15 устРойствавыходов 23 и 24 блока 6В ервом случае возникновейия коррекКР 1 - КР и ) или при появлении любой тиРУемой ошибки "КО" на входах 14 УстРой- другой "запрещенной комбинации на вхо- ства (возникновение одиночных пакетных дах блока 10 с: .,5 ошибок иКОк" в разньх йодгруптпах.блокови ко . памяти), на контрольных выходах 16 и 18 тролируемой группы блоков памяти; 01 усройства сохраняются логические нули", или и 10 м формируется в парафазном виде а ана контрольных выходсах 17 - появляется в режиме "Запись" код ошибки имеет вид "11 м те в режиме "Запись" КОк=НКОк 50 Во втоРом слУчае (возникновение неваЭто различие учитывается блокомоб- скольких 1,2 а пакетных ошибок; или наружения ошибок 13, который, анализи гпупповых ошибок четного веса в одной Руя За - разрядный код ошибок на подруппе блоков памяти и возникновение контрольных выходах 16, 17 и 18 устроист- . только одночных пакетнысх Ошибок в дру 55 гих подгруппах блоков памяти), на контва, формирует четырехразрядный код на выходе 19 (признаков ошибки ст ойства) Рольных выходах 16 устройства появляется в режиме "Запись" или "Чтение- по раз унитарный в-разрядный код некорректируным формулам, емой ошибки К-й подгруппы блоков памяти:"Н КО:(НКО 1 ОИ КО(-1) 4НКО(к+),НКОДна соответствующем ("КО)") выходе 17 устройства появляется "логический нуль", а состояние остальных контрольных выходов 17и 18 - безразлично,Если же на входах 14 устройства появляются некорректируемые ошибки в двух иболее подгруппах блоках памяти (например,при возникновении четырех пакетных ошибок при отказах двух блоков памяти однойподгруппы блоков памяти и двух блоков памяти другой подгруппы блоков памяти ит.п.), на контрольных выходах 16 устройствапоявляются две и более "логические едини-,цы", а нз выходах 19 устройства формируется код "1010" некорректируемой ошибкиустройства, и работа устройства прерывается. Работа устройства также прерьвается вслучае вознйкновения неисправностей в самих блоках устройства. Например, при возйикновении неисправностей в генераторе 6кода ошибок или блоках 9 и отсутствии ошибок на входах 14 устройства (в блоках памяти) нэ контрольных выходах 16 и 17устройства сохраняотся логические нули, ана вьходах 18 появляются "логические единицы". В данном случае, согласно формуламработы блока 13, на выходах 19 устройстваформируется "запрещенный" код "1000", иработа устройства также прерывается.Рассмотрим работу устройства в режиме "Чтение" в случае полного отказа трех изМ блоковпамяти при реализации в устройстве трехмерного кода (64, 32) с параметрами; и = т = 4, кодовая матрица которого.представлена на фиг. 3.В работе устройства при отказах любыхтрех из 16 блоков памяти могут возникнутьпакетные ошибки различной конфигурации:а) трй пакетнье ошибки возникли в разных подгруппах блоков памяти, например; вЗ-м, 7-м и 11-м блоках памяти соответственно первой, второй и третьей подгруппы;б) три пакетные ошибки возникли в двухподгруппах блока памяти, например: в З-м,б-м и 7-м блоках памяти соответственнопервой и второй подгруппы;в) три пакетные ошибки возникли в одной подгруппе блоков памяти, например; вшестом, седьмом и восьмом блоках памятисоответственно второй подгруппы,При полном отказе любого 1-го блокапамяти на соответствующем входе 14 устройства возникает пакет однонаправленных ошибок типа "4 нуля" или "4 единицы";(разряды каждого из 16 блоков памяти расположейы на соответствующих им позицияхв подматрице Н(, контрольные разрядыстрок и столбцов отделены).При этом в информационные (1 - 3, 5 - 7,9-11 и 13 - 15) блоки памяти записана комбинация; "1110", а в контрольные (4, 8, 12 и 16)блоки памяти - соответственно комбинация, "0001".При полном отказе типа "4 нуля" втретьемседьмом и одиннадцатом блокахпамяти (пример а), на входы 14(з), 14 р) и 14(1 з)устройства и на первые входы блоков 9 з, 9 ти 9 ц поступает комбинация "0000" вместо"1110"; т.е. на входы 14 устройства поступает 64-разрядная комбинация с девятью искаженными (1 -О) символами:156, 157, 158256, 257, 258356, 357, 358,На входы блоков 101, 102 и 10 з поступаеткомбинация 00101110, а на входы блока 104поступают логические нули. На выходах 16и 18 устройства сохраняются "логическиенули", на вьходах 17 устройства формируется код 1110, а нэ выходе 19 устройства формируется код корректируемой ошибкиустройства: "0110".Так как в данном инье ошибки возникли в римере (з) три пакетразньх(первой, втоСогласно модифицированной структуре примененных в устройстве двумерных кодов (16,8) с контролем по нечетности строк и с контрольным разрядом по нечетности Со, при появлении на входе 14 устройства пакета ошибок типа "4 нуля" или "4 единицы"соответствующая (1-я) строка кодовой матрицы (фиг, 3) будет содержать четное (запрещенное) количество единиц, При этом . на выходе 21 блока 1 формируется "логическая единица", а на выходе 221 блока 3 - формируется нечетное количество единиц, на выходах 16, 17 .блока 101 формируется код 01, Одиночная пакетная ошибка 1-го блока памяти исправляется в блоке 9 и исправленные разряды 1-го блока памяти поступают с выхода 25 блока 9 на выход 15.: устройства. На выходе 19 блока 13 формируется код "0110" корректируемой ошибки устройства и исправленное 64-разрядное . кодовое слово постуйает с выходов 15 устройства на выходную магистраль данных,Пусть в каждой из четырех подгрупп блоков памяти записаны одинаковые 1,6- разрядные кодовые слова подматриц. Н-Н 4рой и третьей).подгруппах блоков памяти, то эти пакетные ошибки независимо исправляются в блоках 9:разряды 136, 137 и 138 - исправляются в блоке 9 з, разряды 236, 237, 238 - в блоке 9 р), а разряды 336, 337 и 338 - в блоке 9(11), согласно синдромно-мажоритарному алго-" ритму декодирования. описанномув (2),На выходах 25 блоков 9 з, 97 и 911 формируются исправленные значения разрядов соответственно З-го, 7-го и 11-го блоков па. 10 мяти; комбинация "1110", и на адресные входы четырех. коммутаторов (фиг, 4) блоков 11(з), 11 р) и 11(11) поступают соответствейно комбинации," 01, 01, 01 и 00, поэтомуна- выходы 15(з) 15 р) и 15(11) устройства пропускаются комбинации "1110" с выходов 25 соответственно блоков 9 з, 97 и 911. В конце цикла "Чтение" 64-разрядное кодовое сло- во с девятью исправленными (О -1) разрядами (т.е. с тремя исправленнь 1 ми пакетами20 ошибок) поступает с выходов 15 устройства на выходную магистраль данных.При полном отказе типа "4 йуля" в третьем, шестом и седьмом блоках памяти (пример б), на входы 14(з), 14(б) и 14 р) устройства и на первые входы блоков 9 з, 9 б и 97 поступает комбинация "0000" вместо "1110".На третью 14 р) - 14(12) и четвертую .14(1 з) - 14(1 б) подгруппы входов устройства поступают "правильные" 16-разрядные ком.- бинации подмэтриц Нз и Н 4 двумЕРного ко да (16,8):111) 0111 035 1 П О000, 1На первую 141-144 подгруппу входов устройства поступает "неправильная" 16- разрядная комбинация с одной пакетной ошибкой типа "4 нуля" в третьей строке подматрицы Н 1 (искаженные символы 136, 137 и 138 - подчеркнуты, а искаженная строка аз - отмечена стрелкой):1110111 ,О0000 -аз000;150А на вторую 14 бб подгруппу входовпоступает "неправильная" 16-.разрядная комбинация с двумя пакетными ошибками во второй и третьей строке подматрицы Н 2 (искаженные символы 233, 234, 235 и 236; 237, 238- подчеркнуты, а искаженные строки аб и а 7 - отмечены стрелкой);111 0000 0 -аб000 0 а 7 000 1Таким образом на входы 14 устройства (пример д) поступает 64-разрядная комбинация с девятью искаженными (1- 0) символами: 136, 137, 138, 233, 234, 235 и 236, 237, 238,На входы блоков 1 Оз и 104 поступают логические нули, нэ"входь 1 блока 101 поступает"комбинация 0010 1110, а на входы блока 102 - комбинация 0110 0000.На выходах 16 устройства формируется код 01100 (Н К 02), на выходах 17 устройства формируется код 1000 (К 01).Пакетная ошибка третьего блока памяти (искаженные символы 236, 137 и 138) исправляются в блоке 9 з согласно синдромномажоритарному алгоритму декодирования, описанному в 2), На выходах 25 блока 9 з формируется "правильная" комбинация 1110 (с исправленными 0-1 значениями 136, 137 и 138 третьего блока памяти), а на адресные входы четырех коммутаторов блока 11 з поступают соответственно комбинации: 01, 01, 01 и 00. Поэтому на выход 15 з устройства пропускается "правильная" комбинация: 1110 с выхода 25 блока 9 з (т,е. младшие разряды адреса четырех коммутаторов).Пакетные же ошибки шестого и седьмого блоков памятине могут быть исправлены в блоках 9 б и 97, т.к, на информационные 14 и контрольные 22 входы (фиг. 2) блоков 9 б и 97, а следовательно, на первый и третий вход каждого МЭ 28 в этих блоках, поступают логические нули, Поэтому на выходах блоков 9 б и 97 формируются "неправильные" комбинации: 0000, а на выходах 232 и 23 з блока 6 формируется комбинация; 1110 по формулам:2 у 1 = 2 у 2 = 2 уЗ =3 у 1 =Зу 2 =.3 уЗ= =1+0+1+1=1.На адресные входы четыРех коммутаторов блока 11 б и блока 117 поступает комбинация 10, поэтому на выходы 15 б и 15 т устройства пропускается "правильная" комбинация: 1110 соответственно с выходов 232 и 23 з блока 6 (т,е. третьи 02 информационные входы коммутаторов блока 11 б и блока 117). На выходах 18 устройства формируется код 0110 по формулам; "Нп 2" = "Нпз" = =1 1 1 0= 1, На входы, блока 13 поступает 12-разрядная комбинация: 0100 1000 0110,а на выходах 19 устройства формируется код "КО": 0110.В конце цикла "Чтение" (пример б) 64- разрядное кодовое слово с девятью исправ. ленными (О-ф 1) разрядами:136, 137, 138, 233, 234, 235, 236, 237 и 238 трех блоков памяти (З-го, 6-го и 7-го) поступает с выхода 15 устройства на выходйую магистраль данных.При полном отказе трех блоков памяти в одной подгруппе (пример в);типа "4 нуля" - в шестом и седьмом блоках памяти и типа "4 единицы" в восьмом блоке памяти на первую 14 р) - 144), третью 14 р) - 14(2) и "четвертую 14 рз), - 14(ы) подгруппы входов устройства поступают "правильные 16-разрядные комбинации подматриц Н 1, Нз и Нз двумерного кода (16,8):1На вторую 14 р) -14(в) йодгруппу входов поступает неправильная 16-разрядная комбинация с тремя пакетными ошибками во второй, третьей и четвертой строке подматрицы Н 2 (искаженные символы 233, 234, 235, 2 Яб, 237, 238, 2 Ь 1, 2 Ь 2, 2 ЬЗ - подчеркнуты, а искаженные строки ав, а 7 ав - отмечены стрелками): 1 Оав 0 -ф ау 1 - ав Таким образом на входы 14 устройства (пример В) поступает 64-разрядная комбинация с шестью искаженными(1-ф 0) символами шестого и седьмого блоков памяти (233 -238) и тремя искаженными (О .+1) символами восьмого блока памяти (2 Ь 1, 2 Ю 2 и 2 ЬЗ), т,е. на входы 14 устройства поступает . 9 искаженных символов.На входы блоков 101, 10 з и 104 поступают "логйческие нули, а на входй блока 10 а поступает комбинация 0111 111 О, соответ- ствующая некорректируемой ошибке во второй подгруппе блоков памяти,.На выходах 16 устройства формируется код 0100 (Н КОг), а на выходах 17 - сохраняются логические нули,Пакетные ошибки шестого, седьмого и васьмого блоков памяти исправляются в блоках 9 в, 97 и 9 в согласно примененному в них синдромно-мажоритарному алгоритму декодирования (хотя и не всегда три пакетные ошибки, возникшие в одной подгруппе блоков памяти, могут быть исправлены в блбках 9). На информационные 14 в. 147 и конт- .рольные 21 в, 217, 222 входы блоков 9 в и 97поступают комбинации: 0000, 1111, 1110,поэтому на входы каждого МЭ 28 - 28 з этихблоков (фиг. 2, 4) поступает комбинация(011), а на входы блока 28 д - комбинация(010).Поэтому методом "голосования" на выходах 25 блоков 9 в и 97 формируется "правильная" комбинация," 1110 (сисправленными 0-1 значениями 233, 234,235 и 236, 237 и 238 шестого и седьмогоблока памяти). ,На информационные 14 в и контрольные21 в, 222 входы блока 9 в поступают комбинации: 1111, 1111, 1110, поэтому на входыкаждого МЭ 28-28 з блока 9 в поступает комбинация (100), а на входы блока 28 - комбинация (1 01),Поэтому на выходах 25 блока 9 в формируется "правильная" комбинация 0001(с ис 20 правленными "1 -+0" значениями 2 Ь 1,2 Ь 2 и2 ЬЗ восьмого блока памяти).На выходах 23 (уЯ блока 6 сохраняются"логические нули", а на выходах 24 ф блока б - соответственно сохраняются "логические единицы" т.к. в данном примере трипакетные ошибки (девять йскаженных символов входа 14 устройства) исправляютсяна первом этапе декодирования в блоках9 в, 97 и 9 в.Поэтому на выходах 25 блоков 9-9)вформируется "правильное" 64-разрядноекодовое слово: на выходах блоков 91 - 9 з,9 в 97, 9 э и 9 зю - формируется комбина-ция 1110, а на выходах блоков 9 д, 9 в, 912и 91 в - формируется комбинация 0001,На адресные входы четырех коммутато-ров (фиг, 4) блока 11 в и блока 11 7 поступаютсоответственно комбинации. 11, 11, 11 и 10,а на адресные входы четырех коммутаторовблока 11 в - комбинации: 10, 10, 10 и 11.Поэтому на выходы 15 в, 157 и 15 в ус гройства пропускаются "прайильные" комбинации: 1110, 1110 и 0001" соответственно свыходов 23 0 у 3 = 0). блока 6 (т.е. третьи 0245 инФормационные входы коммутаторов) илис выходов 24 ( у) = 1) блока 6 (т,е, четвертые03 информационные входы коммутаторов),На выходах 18 устройства сохраняются"логические нули", поэтому на входы блока13 поступает 12-разрядная комбинация;0100 0000 ОООО, а на выходах 19 устройстваформируется код "КО": 0110,Вконце цикла "Чтение" (пример в) 64 разрядное кодовое слово с тремя исправленными пакетными ошибками, а именно сшестьго исправленными (О - 1) разрядами;2 ЯЗ, 234, 2 Я 5 и 236, 237, 238 - шестого иседьмого блоков памяти, и с тремя исправненными (1-ф 0) разрядами: 2 Ь 1, 2 Ь 2, 2 ЬЗ -восьмого блока памяти, поступает с выхода15 устройства на выходную магистраль данных.Аналогично в устройстве могут быть исправлены или обнаружены четыре пакетйыеошибки определенной (корректируемой илинекорректируемой) конфигурации.Так, четыре пакетные ошибки в четырехразных подгруппах блоков памяти: е треть-ем, седьмом, 11-м и 15-м блоках памяти "О(пример а ) - могут быть исправлены в блоках 9 з, 97, 911 и 915.Четыре пакетйые ошибки в трех под-группах блоков памяти: в третьем, шестом, седьмом и 11-м блоках памяти "5(пример б ) - могут быть исправлены вблоках 9 з. 911 и 116, 117,Четыре пакетные ошибки в одной"подгруппе блоков памяти: в пятом, шестом,седьмом и восьмом (пример в) - могутбытьисправлены е блоках 115, 116, 117 и 118.В данных примерах: а, б и в., наконтрольных выходах 16, 17 и 18 устройстваформируется соответственно код ошибок;0000 1111 .ОООО (а ),или 0100 1010. 0110 (б),или 0100 .0000 1111 (в),а на выходах 19 устройства формируется код"корректируемой ошибки чтения"; 0110.Четыре пакетные ошибки в двух под.группах блоков памяти (некорректируемойконфигурации): во втором, третьем и шестом, седьмом блоках памяти, могут быть обнаружены в блоках 101, 102 и 13 устройства,При этом на контрольных выходах 16 и 17 35устройства формируется "запрещенная: .комбинация: 1100 0000, а на выходе 19- код"некорректируемой ошибки чтения": 1010,Аналогично в устройстве обнаруживаются идругие (4-И) пакетные ошибки некорректи 40руемой конфигурации,Кроме того, устройством гарантйрованно обнаруживаются все трехбитовые и четырехбитовые (непакетные) ошибки.Так, при возникновении некорректируемой трехбитовой ошибки на входах 146 и147 устройства; в разрядах 253, 236 и 257подматрицы Н 2(фиг. 3), и отсутствии ошибокна других входах 14 устройства, на входыа и р блока 102 поступит код: 0100 0100, 50который блок 102 "воспримет" за одиночнуюошибку в разряде 234, а следовательно,сформирует на выходах 162 и 172 код корректируемой ошибки "К 02": 01. Одновременноблок 92 "неправильно исправит разряд 234, 55в результате чего на выходах 25 блоков 96 и97 сформируется комбинация уже с четырьмя искаженными символами подматрицы Н 2: 233, 254, 236 и 237, а на выходах 232 и 23 з блока 6 - соответственно сформируются четыре "логические единицы:.2 у 1, 2 у 2, 3 у 1 и 3 уЯ.В результате на контрольных выходах 16, 17 и 18 устройства формируется "запрещенная" комбинация: ОООО 0100 0110, а на выходе 19 - код "некорректируемой ошибки чтения": 1010,При возйикновении некорректируемой четырехбитовой ошибки на входах 146 и 147 устройства: е разрядах 233, 236; а 6 и а 7 подматрицы Н 2. внесенной, например, в кодовое слово при "Записи" (см. описание работы устройства в режиме "Запись" ), т,е, прй поступлении двух неправильЙых информационных разрядов: 233 и 236, формировании дополнительно двух неправильных контрольнь 1 х разрядов: а 6 и а 7 и записи в память кодового слова ужес четырехбитовой ошибкой (необнаруживаемой блоком 13 в режиме "Запись" ) на контрольных выходах 16 и 17 устройства в режиме "Чтение" сохраняются "логические нули", но на выходах 232 и 23 з блока 6 сформируются четыре "логические единицы": 2 у 1, 2 уп, 3 у 1 и 3 упВ результате на входы блока 13 поступает "зайрещенная" комбинация: 0000 0000 0110, а на вь 1 ходе 19 устройства формируется код "1000",.соответствующий в данном примере двухбитовой (некорректируемой) ошибке записи, обнаруживаемой в режиме "Чтение", и работа устройства прерывается,Таким образом (как было показано) реализация в устройстве синдромно-мажори-тарного алгори 1 ма кодирования и декодирования с "адаптацией" на втором этапе, позволяет исправлять три пакетные ошибки, обнаруживать (4 - й) пакетные ошибки и трех-четырехбитовые (непакетные). ошибки некорректируемой информации.Кроме того данный алгоритм позволяет исправлять одиночные и обнаруживать двухбитовые ошибки, внесенные в кодовое слово при записи в память,Технико-зкономическое преимущество заявленного устройства, реализующего модифицированный трехмерный код с кодо-. вым расстоянием б - 8, по сравнению с известным устройством, реализующим модифицированный двумерный код с кодовым расстоянием д = 4, заключается в более высокой надежности и в существенном расширении его функциональных возможностей.Эти преимущества достигаются благодаряболее высоким и более сложным (комбйнированным) корректйрующим иобнаруживающим возможностям выбранного для устройства кода и обеспечиваютсаза счетреалйзации"в заявЛенномустройст-ве синдромномажоритарноГо алгоритмакодирования й декодирования с "адаптацией" (в два шага), а также за счетусложнения.Логики обнаружения ошибок.В известномустройстве примейен модифицйрованный двумерный код с койтролем по нечетности строк и столбцовкодовбйматрицы, й реализован синдромно-мажоритарный алгоритм декодирования (в одиншаг), что позволяет устройству:1) исправлять одиночные пакеты и-разрядных ошибок в Й блоках памяти;2) обнарукивать двухбйтовйе ошибки вбдном или разных блоках-памяти;, 3) обнаруживать одиночные ошибкй,внесенные во входную информацию при записи в память,Недостатками известного уСтройстваявляются его низкая надежность и ограниченнь 1 е функциональные возможности,Э ги недостатки связаны с тем, что из-занизкой корректирующей возможности примененного вустройстве кода, известное устройство не может скорректировать дажедва пакета й-разрядных ошибок (или двух битовую ошибку одного блока памяти), атакже Одйночную ошЙбку, внесеййую вовходную информацию при записй в память.В заявленном устройстве применен модицифированный тоехмерный код; составленный изц модифицированныхдвумерных кодов, с дополнительным контролем по четности для каждого ( Я - разрядного ребра кодовой матрицы, иреализован сийдромно-мажоритарный алгоритм кодирования и декодирования с"адаптацией" (в два шага), а также за счетзначительного усложнения логйки обйаружения ошибок, что позволяет. устройству.1) исправлять три пакета и-разрядныхошибок в й блоках памяти;2) исправлять двухбитовые ошибки в одном или разных блоках памяти (и обнарукивать все трех- и четырехбитовые ошибки);Э) исправлять одиночные ошибки (и об наруживать все двойные ошибкй), внесенные во входную информацию при записи впамять.Ограниченные возможности известного, устройства (второй его недостаток) объясняется тем, что данное устройство предназначено только для исправления ошибокжестко заданной конфигурации, а именно: для исправления фиксированных одиночных (т.е, ограниченных разрядами одного блока памяти пакетов однотипных ошибоктипа "и нулей" или "и единиц"), вызванныхотказами блоков памяти или отказами эле ментов электроники обрамления.При такой постановке задачи структурадвумерного кода, примененного в извест 1 ном устройСтве, является оптимальной дляисйравленйя одиночных пакетных ошибок иобнаружения Двойных ошибок в полупроводниковых системах хранения информации,Расширенные (по сравнению с прототипом) Функцйональные возможности заявленного устрриства объясйяютСя гем, что"данное устройство способно исправлятьошибки различйой конфигурации, а именно,двойные, групповые и пакетные ошибки (иих сочетания), а также обнаруживать трехчетырехбитовые ошибки; двойные ошибкиЗаписи, и т,п, -Позтомузаявленное устрОйство можетбыть оптимально использовано в вычисли-тельных сетях, представляющих собой симбиоз ЭВМ, запоминающих устройств и:линий связи, имеющих разную специфйкувознйкновенйя ошибок и их конфигурацию,Прймеыение заявленного устройства ввычислительных сетях позволяет произво" дить коррекцию информации, поступающейиз Запомийающих устройств и линий связи,в одной тбчке, иследовательно, обеспечить:35- высокую суммарную надежность вычислительной сети,Заявленное устройство реализующеемодифицированныйтрехмерный код, можетбытьдополйительно использовано:- в системах передачиинформацйи пой каналам- для коррекции нескольких па кетов ошибок ("стертостей"), вызванных не-исправностями нескольких (двФ, три) кайалов или внешней помехой, одновре менно воздействующей на несколько. (два,три) каналов;- всистемаххрайения информации, вы, полоненных на магййтных носителях с й по движными головками, в которых лакуны намагнитной ленте могут привести к потере информации, СЧйтываемой несколькими (двумя, тремя) головками. Формула изобретенияУстройство для обнаружения и исправления ошибок, содержащее первый генератор кодов ошибок из И блоков свертки помодулЮ два и второй генератор кодов ошибок из и блоков свертки по модулю два первой группы (где И - число информационных входов, а и - разрядность информационных1785041 38входов), блок обнаружения ошибок и й бло- группы подключены к входамтретьей групков коррекцйи, причем информационные пы блока обнаружения ошибок и являютсявходы группы каждого блока коррекции со- контрольными выходами третьей группы усединены с соответствующими входами -тройства, информационными входами котогруппы первогогенератора кодов ошибкии 5 рого являются входы второго генератораявляются информационными входами соот- . кодов ошибок,каждый 1-й блок коррекцииветствующей группы устройства, первый (где 1=(к - 1)а+1) являетсясоответственно 1-мконтрольный вход каждого блока коррекции (где 1 = 1.,т. блокомкоррекции 1-й группыподключен к соответствующему выходу пер-(где 1 - соответствующий номер 1-го инфорвого генератора кодов ошибок, вторые кон мационного входа устройства в информацитрольные входы с пе)вого по щ-й блоков . онных входах 1 с-й;группы устройства),коррекции (где а =ЧЯ) объединены и под- выходы блоков коррекции подключены к соключены к выходам первой группы второго . ответствующим входам третьего генераторагенератора кодов ошибок, первый; третий кодов ошибок и управляющим входам групи четвертый выходы блока "обнаружения .15 пы соответствующего блока коммутаторов,ошибок являются выходами некорректиру-выходы которого являются соответствуюемых ошибок устройства, выходом коррек- щими информационными выходами устройтируемых ошибок которого является ства, прямыевыходы 1-й группы третьего,второй выход блока обнаружения ошибок,генератора кодов ошибок подключены соото т л и ч а ю щ е е ся тем, что, с целью 20 ветственно к входам 1-го элемента ИЛИ, арасширения областиприменения устройст- также к информационным входам первойва за счет исправления трех пакетов.и обна- группы 1-го блока коммутаторов, инверсныеружения М пакетов п-разрядных ошибок, в выходы 1-й группы третьего генератора конего введенытретий генератор кодовоши- дов ошибок подключены к соответствуюбок, содержащий гп групп блоков свертки по 25 щим информационным входам второймодули два, блок из в индикаторов иСправ- группы 1-го блока коммутаторов, адресностей, Й блоков коммутаторов и группа ":ныевходы группы которого подключеныэлементов ИЛИ, второй генератор кодов к соответствующим выходам первойошибок содержит со второй по гп-ю группы:. группы К-го индикатора неисправностей,блоков сверткипо модулюдва, причем вы входы первой и второй групп которого: ходы первой и второй групп блока индика- подключены соответственно к первым иторов неисправностей йодключены к вторым контрольным входам блоков кор. входам первой и второйгрупп блока Обна- рекции К-й группы; управляющие входыружения ошибок и являются соответственно"индикаторов неисправностей обаединеконтрольными йыходами первой и второй 35 ны и являются управляющим входом устгрупп. устройства, выходы элементов ИЛИ ройсгва." г" - - -Я 4, ЦЯЯ ЯЯгк гффф 7гг Ь(Авторыми контрольными выходами устройст- логического блока коррекции, входы второй ва;:.:.,группы первого и второго блоков коррекцииЙедаСтатками известного устройства ошибок подключены соответственно к перявляются его аппаратурная сложность и вым и вторым контрольным входам 1-го лониэкая достоверность выдаваемой инфор гического блока коррекции, а выходымации,"свяэанйые с тем. что оно не может первого и второго. блоков коррекции ошибокобйаружить даже двухбитовую ошибку в подключены соответственно к входам вторазных блоках памяти, а также с тем, что в рой и третьей групп блока мажоритарных устройстве реализован синдромный алго- элеМентов, выходы которых подключены к ритм декодирования.:, :,: 10 информационным выходам 1-го логическогоНаиболее близкйм техническим реше- блока коррекции 2).нием к предлагаемому является устройство 8 данном устройстве реализован синддля обйаружения и исправления ошибок в ромно-мажоритарный алгоритм декодиро- Й:бл 6 кахпамяти, содержащее первый гене- вания двумерного модифицированного ратор кода ошибок из й блоков свертки по 15 итеративного кода с контролем по нечетномодулю два и второй генератор кода оши- сти строк и столбцов, что позволяет исправбокиз в блоков свертки йо модулюдва(где лять Одиночные пакеты и-разрядныхй - разрядность блоков памяти, а й - их.: ошибок, вызванные отказами электроникиколичество), логический блок обнаружения обрамления блоков памяти, обнаруживать ошибок, имеющий две группы входов, и М 20 2 - 1 ч) пакетов п-разрядных ошибок, одиночлогических блоков коррекции, состоящих: ные групповые ошибки четного веса, а таксоотаетственноиэпервЬгоивторогоблоковже обнаруживать одиночные ошибки, Коррекции ошибок и блока мажоритарныхвнесеннйе ао входнуюинформацию при заэем 6 йтов, причем и информационных вхо- "писи в память:довкаждого Но(1 = 1-й) логического блока 25 Недостатками известного устройства корекцииобъедийеныс-й.группой входов являются его низкая надежность и ограниперЮго генератора кода ошибок и с входа-ценные фуйкциональнйе возможности.миМгруппы второго генератора кода оши-: . Эти недостатки связаны с тем, что из-за ба: и подключены к 1-й группе:, низкой корректирующей возможности при ийформациойных входов устройства, а и ин- ЗО мененвого в устройстве кода оно не может формационных.выходов каждого 1-го логи- скорректировать даже две одиночные (или ческого блока коррекции подключены пакетные) ошибки, возникшие в разных блосоответственно к 1-й группе информацион- ках памяти, или групповую ошибку. четного ных восходов устройства, И выходов первого . веса одного блока памяти, а также ошибки,генератора кода ошибок.И и выходов второ внесенные во входную информацию при эаго генератора кода ошибок являются соот- писи в память.ветственйо первой и второй"группами Цель изобретениярасширение облаконтрольных выходов устройства, первые сти применения устройства эа счет обеспе контрольные входы 1-го логического блока чения возможности исправления трехкбррекции подключены соответственно к 1- 40 пакетов и обнарукения.(4-й) пакетов и-разМу выходу первого генератора кода Ошибок, рядных ошибок, а также обеспечения дополвторые контрольные входы логических бло-: нительно возможности исправления ковкоррекцииспервогойой-йобъединеныдвойных ошибок, одиночных групповых ,меЖду собой и подключены к выходам вто- . ошибок и ошибок,вненесенйых во входнуюрого гейератОрй кода Ошибок, первый, тре информацию при записи в память, тйй и четвертый, выходы логического блока: Указанная цель достигается тем, что в Обнаружения. ошибок являются выходами устройство для обнаружения и исправления некорректируемыхошибокустройства, вто- ошибок в К блоках памяти, содержащее ".","Хрой выход - вйходом корректируемых оши- первый генераторкодов ошибок из Й блобок устройства, а первая и вторая группы 50 ков свертки по модулю два (где й - количевхбдов логического блока обнаружения ство блоков памяти) и второй генератороШибок подключены соответственно к пер- кодов ошибок из и блоков свертки по модувойи второй группам контрольнйх выходов лю два первой группы где и - разрядность устройсгва, крометого, в каждом-млогиче- блоков памяти), блок обнаружения ошибок Ском блоке коррекции входы первой группы 55 и И блоков коррекции, состоящихсоответпервогоблокакоррекцииошибокобъедине- ственно из первого и второго блоков корныс входами йервой группы второго блока рекции ошибок и блока мажоритарных коррекции ошибок и с входами первой груп- элементов, причем п информационных вхопы блока мажоритарных элементов и под- дов каждого 1-го (1 = 1-М) логического блока ключены к информационным входам 1-го коррекции объединены с 1-й группой входов1785041Составитель А. Савиноватор С. Кулакова Техред М.Морген гад Корректор В. ЙетрашЗаказ 4368 Тираж ПодписноеВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР113035, Москва, Ж, Раушская наб 4/5Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 1первогогейератора кода ошйбаки подкла-койтролируемойгруппеблоковпамяти,причены к 1-й группе информационных воДов чем каждая 1-я и-разрядная группа инфорустройства, первые контрольные вхбды 1-го мационных входов устройства падкл;оченаблока коррекции подклЮчены соответсТйен- - соответСтвенно к входам 1-й группы 1-й груп- но к 1-му выходу первого генератдраЪбда 5 пы входов вторагогенераторакода Ошибок, ошибок, вторые контрольные входы блоков аи информационных вьйодов каждого 1-го коррекции с первого по й-й, где в - Колйче- блока коррекции йодключены кпе 1 вой груп- ство блоков памяти первой груйпы, объеди- пе управляющихвходов 1-го блокакоммутанены между собой и подключены к первой торов, выходы котброго йадтл 1 ачены группе выходов второго генератора -кода 10 соответственна к 1-й и-разрядной группе иношибок, первый, третий и четвертый выхо- формационных выходов"уСтройства, т сыды блока абйаружения ошибок являквся - хбдов 1-й группы выходов" первого выходами некорректируемых ошибок "фУ-гВТератора кода ошибок и и выходов 1-й райства,второй выход - выходомкорре 1 ти- групйы выходов второго генератора кода руемых ошибок устройства, а йервая й 15 ошибок подключены соответственно к пер вторая группы входов блока обнаружения вой и второй группа 4 входов 1-го индикатаошибок подключены соответственна кйер-ра неисправностей, первйе и выходов 1-й ," .войи второй группам контрольных вйодов группы выходов третьего генератора кадаустройства, кроме того, в каждом 1-м блоке ошибок падкляченй соответственна к вхо.коррекции входы перваи группы первого 20 дам 1-га элемента ИЛИ, а такке к третьей блока коррекции ошибок объединеныс вхо-группе информационных входов 1-го блока дами первой группы второго блока козырек- коМмутаторов, вторые (инверсные) и выхации ошибок и с входами первой группы дов 1-й группы выхадовтретьего генератора блока мажоритарных элементов и падклю-" кадаайибак подключены соответственна к чейы к информационным входам 1-гоблока 25 четвертой группе информационных входов коррекции, входы второй группы первого и 1-го блока коммутаторов, вторая адресная втбрага блоков коррекции ошибокподклю-группа входов катарогЬ йадкл,ачана к перчены соответственно к первьгм и вгарымному"выходу 1-го индикатора неисправно- контрольным входам 1-га блока коррекции, "стей, вторые контрольные входы блоков а выходы первогои второго блоков каррек коррекции 1-й группы йодключенй к второй цйи ошибок подключены саатветствейно к группе входов 1-го индикатора неисправна- входам второй и третьей групп блока Мако-стей, а управляющий вход устройства падритарныхэлеменетаввыходы каторыхпад- клочек соответственна к управляющему ключены к информационным выходам 1-го . входу каждого индикатора неисправностей логического блока коррекции, введень 1 тре с первого па п-й.тий генератор кода ошибак,садеркащий п Введение в устройство третьего генерагрупп из и блоков свертки па модулю два,: тора када ошибок, содержащеговгрупп из блок из ги индикаторов неисправностей, И и блоков свертки по модулю два, блока иэ п блоков коммутаторов (где И = ги ) и группаиндикаторов неисправностей, И блоков . из а элементов ИЛИ, кроме того:, второй 40 коммутаторов и гп -и-ьхадавых элементовгенератор кода ошибок дополнительйосо-ИЛИ с соответствующими связями, а также держит со второй по ги-ю группы из и блоков введение ва второй генератор кода ошибок свертки по модулю два, причем выходй" пЪр.- са второй -па ги-ю"грИК" состоящих из и. вай и второй групп блока индикаторов неис-блоковсвертки по модулюдва, и изменениеправностей являются саатветствейна 45 связей второгогенератора-года ошибок сОпервой и второй группой контрольных выхо- информационными входами устрайсгва и дав устройства, а выходы элементов ЙЛИ: контрольными входами логических блоков являются третьей группой кантоольных вы-: коррекции (при одновременном уменьше- ходов устройства и подключены саотвдтсг- ний в ги = ъя раз числа входов каждого венно к третьей группе входов блока 50 блока свертки па модулю два второго генеобнарукения ошибок, при этом первый и ратаса кода ошибок) позволяетреализовать второй выходы каждого 1-го (1 = 1 - ги) инди-" в устройстве корректирующий код с более каторз неисправностей являются сОответ- высокими и более сложньгми (чем у протатиственно выходом некорректируемойпа) корректирующимисвойствам 1 л.ошибки и выходом карректируемой оШибки 55 При этом взаявленномустройствеабес 1-й контролируемой группы блоков памяти"; " печивается возможность исправления трех акаждый 1-й блок коррекции, где 1"(1 - пакетов и-разрядныхошибок и обнаруже)а+1, является соответственно 1-м (1 =1 - ги) . ния (4 - И) пакетов и-разрядных Ошибок, блоком коррекции 1-й группы (где 1 - "соот- кроме того, в устройстве допалйительна ветствующий номер 1-го алака памяти в 1-й обеспечивается возможность исправления7 .: 1785041 8одиночных групповых ошибок и ошибок, состоит из и сумматоров по модулю два, ивнесенных во входную инФормацию при за- блок 28 мажоритарных элементов; состояписив память,:":,:,; .щий из и трехвходовых мажоритарных эле-Тэким образом, введенные элементы и ментов, реализующих функцию ( 2),связи позвОляют повысить надежность уст причем информационные входы 14 каждогоройства и расширить его функциональные ЛБК 9 подключены к входам первой группывозможности ::.: ; блоков 26, 27 и 28, контрольные входы 21 иПосле проведения патентного поиска 22 каждого ЛБК 9 - к входам второй группыне обнаружено устройств, обладающих эк- блоков 26 и 27, а информационные выходывивалентной совокупностью элементов и .10 25 - к выходам блока 28, кроме того, в кажсвязей, дающих аналогичный эффект и реа- дом ЛБК 91 выходы блоков 26 и 27 подклюлизующих предлагаемый авторами синд- чены к входам второй и третьей груйпромно-мажоритарный алгоритм .: блока 28,декодирования "с адаптацией".грехмерногоНа фиг,1-4 Со, С; Я - информационныемодифицированного йтеративйого кода,. 15 разряды трехмерного кода, поступающие вЙа фиг, 1 представлена структурная режиме "Запись" на информационные вмосхема устройства для. обнаружения и исп-. дц 141-14 и устройства;равления ошибок в Й и-разрядных блоках а и Ь - контрольные разряды по нечег, памяти; на фиг. 2 - функциональная схема ности для в строк и и столбцов каждой подлогического блока коррекции 91 (где - но матрицы (Н 1 Ддвумерного кода (где К = 1 - в),мер блока памяти), . .:.: . формируемые в режиме "Запись" на инфорНа фиг, 3 - геометрическая интерпрета- мационнь х выходах 151-15 ы устройсвта,ция кодовой матрицы трехмерного кода (64, а,ф; у - разряды синдрома, формиру 32) с параметрами: и = 4, И = 16, составлен- емце в режиме "Чтение" соответственно на. ного из гп = Я =4 подматриц(Нк) двумер выходах 21,22 и 23 генераторов 1,3; 6 кода, ного кода (16,8), структура которого описана ошибок.в (2); на фиг, 4 - схема коррекции разря- На фиг. 3 стрелками(-), (4), (фс) указаныдов б(ЦА) для одного (1-го) блока памяти,:. группы разрядов, входящих в соответствуюгде Ц А - координаты позиции каждого сйм-щие строку, столбец и ребро кодовой матри, вола трехмерного кода в кодовой матрице 30 цы трехмерного кода; на фиг.41 сЗ(В,Д)-всФ(Ф,(фиг, 3), 1 = (К - 1)в+1, (1 А = 1. - в).- одноименные)-е разряды одноименныхУстройство содеркит (фиг. 1) первый 1 1-х блоков памяти в каждой контролируемойгенератор кода ошибок, состоящий из бло- . группе блоков памяти,,ков Свертки 21 - 2 и по модулю два, второй 3 : Схема обнаружения некорректируемыхгенератор кода ошибок, состоящий из групп 35 (НКО) и корректируемых (КО) ошибок уст 41-4 блоков свертки 51 - 5 п по модулю два,ройства имеет пять каскадов и состоит изи третйй 6 генератор кода ошибок, состоя- последовательно соедйненйых;,щий из групп 71-7 П блоков свертки 81-8, по- первого 1 и второго 2 генераторов"модулю два (где в = Я, логйческие блоки кода ошибок (первый каскад), формируюкоррекции 9 - 9 и(ЛБК), индикаторы неисп щих соответственно на выходах 21.и 22,равностей 101-10 п 1, блоки коммутаторов (в (в+ и- разрядный код синдрома,, 111-11 м, элементы ИЛИ 121-12 и логиче- - индикаторов неисправностейский блок обнарукения ошибок 13 (ЛБО), 101 - 10 п.(второй каскад), формирующих наУстройство имеет информационные контрольных выходах 16 и 17 устройства141-14 и группь 1 входов, информационнь 1 е 45 2 в-разрядный код ошибки (НК 01-НКОпь151 - 15 и группы выходов, а также первую КО 1 - КОп), и блоков 91-9 м коррекции, неза 161-16 п 1, вторую 171-17 п и третью 181 - 18 п: висимо формирующих на выходах 25 испгруппы контрольных выходов устройства, равленные,- зйачения разрядоввыходы 191, 19 з, 194 - некорректируемых соответственно для гп контролируемых, ошибок устройства и выход 192- корректи групп блоков памяти,руемых ошибок устройства, управляющий:,: - третьего 6 генератора кода ошибоквход 20 устройства,(третий каскад), формирующего йа выхоГенераторы 1, 3 и 6 кода ошибок имеют дах 23 (в и)-разрядный код синдрома"соответственно выходы 21, 22 и 23, 24, а (1 у 1 - 1 уи,;в у 1 - в уи),логические блоки 9 коррекции - имеют вы- элементбв ИЛИ 12(четвертый каскад),ходы 25. :формирующих на контрольных выходах 18Каждый Аогический блок 9 коррекции устройства в-разрядный код ошибки, и блосодержит(фиг.2) первый 26 и второй 27 бло- ка 13 обнаружения ошибок (пятый каскад),:ки коррекции ошибок, каждый из которых анализирующего 3 гп-разрядныйкодошибок9 10на контрольных выходах 16, 17 и 18 устрой- -плоскость А - составленную из 1 п иства и формирующего на выходах 191-194 контрольных разрядов по нечетностиустройства четырехразрядный код - прй- стрск (а 1),знак корректируемой (например, три йакет- - плоскость В - составленную из (щ и)ные ошибки в блоках памяти) ошибки 5 контрольных разрядов по нечетнбсти столустройства или некорректируемой (напри- бцов (ЕЬ 1);мер, четйреи более пакетные ошибкив- плоскость С. - (подматрица Н), соблоках памяти) ошибки устройства (ЙКО, ставленную из(а и) контрольныхразрядовКО, Нп 4 в, НпЗп); :- : (1 СД для ребер кодовой матрицы трехмерноПриотсутствиинеисправйостейвсамой 10 гокода.схеме обнаружения ошибок в каждом цикле : Каждый размер трехмерного кода имеетработы устройства(как в режиме записи, так . координаты (1, ), 1 с), т.е. является )-м разряив режиме чтения Очередного(й и)-разряд- дом 1-й строки К-й подматрицы (Н 1 с) и запиного кодового слова, поступившего на вхо-. сывается в 1-й блок памяти устройства (гдеды 14 устройства) на выходах 191-194 15 1- (К - 1)гл + 1), т.е. в 1-й блок памяти К-йустройства может появиться только Однй из "контролируемой группы блоков памяти (гдепяти разрешенных комбинаций, каждая из: 1, К= 1 - в).которых является кодом признака Соответ- :, Например, информационный разрядствующей ошибки устройства: :.,;., 236 трехмерного кода (64, 32), имеющий в1) "0000" - признак отсутствия ошибок,20 кодовой матрице (фиг. 3) координаты (3, 2,в режиме "Запись" или "Чтение";. 1), является соответственно первым Д - 1)2) "0101" - признак корректируемая разрядом третьей (1 = 3) строки второй (К=2)ошибки в режиме "Запись";;".-,- подматрицы (Н 2) двумерного кода (16,8) и3) "1001" - призйак некорректируемой заййсывается в Седьмой (1 = 7) блок памяти,ошибки в режиме "Запись"; ,:.,.: " 25 т.е. 236 = б(3,2,1).4) 10110" - . прйзнак корректируемай - . Контрольные разряды а 1, КЬ 3, 1 с). распоошибки в режиме "Чтение";:: ложенные в трех проверочных плоскостях А,5) "1010" - признак корректируемой В,С трехмерного кода, имеют соответственошибки в режиме "Чтение" : - .; . но координаты (1,и, К), (а,),К) и (Ц,п).Лабая другая. комбинация (кроме пяти 30 Например, контрольные разряды ау,перечисленных) является для устройства 2 Ь 1 и Зс 1, имеющиесобственно координаты"запрещенйой" и свидетельствует о. неисп- (3,4,2), (4,1,2) и (3,1,4), являются:равйости в самой схеме контроля,:. - четвертым разрядом третьей строкикаждый индикатор неисправностей . подматрицы (нг), т.е. а 7 = с 1(3,4,2);101-10 настроен нанеисправноститолько 35 - первым разрядом- четвертой строкиодной (" собственной" подгруппы из в бло-: подматрицы 1 Н 2, т.е, 2 Ь 1 = б(4,1,2);ков памягии.служится выявления коррек-:-первым разрядомтретьей строки под тируемых (например, одиночная пакетная матрицы (Н 4), те, Зс 1 -, б(3,1,4).ошибка в подгруппе блоков памяти) ошибок .При этом контрольные разряды ат, 2 Ь 1или некорректируемых(например, две ибо" 40 и Зс 1 записываются соответственно в седьлее пакетные: ошибки в подгруппе блоков:мой (1 = 7), восьмой(3 = 8) и 15-й (1 = 15) блокийамяти)ошибок в а и-раэрядном кодовом - памяти.слове двумерйого кода, поступающем.вкаж- Первое(проверочное) ребрб трехмернодом цикле работы устройства на соответст-го кода (64, 32) составлено из четырех контвующую подгруйпу информационным 45 рольных разрядов: 1 СО,2 СО,ЗСО и 1 С 1) повходов 14 устройства. . .:, нечетности соответственнодля четырехУстройство (фиг. 1) для обнаруже- . еосьмиразряднйх сообщений:ния и исправления и-разрядных оши-; (1 Я - 138,281-288, 331-338 и 1 С 2 бок в гп блоках памяти (где. и и в - .ЗСЗ), поступаюЩих на входы 14 устройствачетные числа) реализует трехмерный 50 для кодирования и записи в четыре контромодифицированный итеративный код,: лйруемйе груйпы блоков памяти.составленный из в двумерных итера-.Прй этом контрольные разряды 1 СО,тивйых кодов; структура и схемная реа СО. ЗСО, 1 С 1 заййсываются соответствен-лизация которых описана в 2)..,но в первый; пятый, девятый и тринадцатыйКодовая матрица трехмерного кода 55 блоки памяти.,(фиг. 3) состоит иза (а и)-разрядных пло- Щестнадцатое (проверочное) реброскостей (подматриц Н 1-Нп 1 двумерного о- трехмерного кода(64, 32), лежащее на переда) и имеет прй этом три проверочные . сечении проверочных.плоскостейАи В, соплоскости: ставлено иэ четь 1 рех контрольных разрядов:: четности собтветственнодля четырех сформированйых 15-разрядных сообщений дву мерного кода (16,8),При этом контрольные разряды а 4, а 8,а 12 и а 16 записываются соответственно вчетвертый; веСьмой, двенадцатый и шестнадцатый блоки памяти. Кэждый контрольный разряд а (1,п 3) 10 трехмерного кода является одновременно контрольным разрядом 1 а в соответствующей подматрице (НЦдвумерногокода." Например (Фиг. 3) контрольный разряд а 7 является одйовременно койтрольным разрядом (2 а 3) подматрицы ГН 23 Устройство (фиг; 1) работает следующимобразом. В обоих режимах работы ("Запись" или"Чтение" ) используются все блокйустройстКодирование информации" в реЖиме записи ее в й блоков памяти заключается в Формирований контрольных разрядов а 1 и щ(1=1 - К,1=1-п, К=1 - в, в=. Ядеух проверочных плоскостей А и В кодовой матрицы трехмерного кода (фиг. 3) и происходит в два этапа;в режиме запись на управляющий вход20 устройства поступает "логическа) едини 30 ца", а. нэ информационные входы 141 - 14 м устройства со входной магистрали данныходновременно поступают Й и-разрядн"ых сообщений (где й = в 2). Нэ первом этапе цикла "Запись" каждая35 К-я подгруппа входов 14 устройства: 141 -14 в 14(ч - в + 1) - 14 н,"состоящаяиз в смежных .и-рэзрядных сообщений (инфор. мационные разряды подматрицы Нк), незавйсимо обрабатываются соответствующей К-.ой подгруппой блоков 2 свертки по модулю два; 21-2 а.2(н - п + 1) - 2 и йервого генератора 1 иода ошибок, подгруппой 41: блоков 5 сверттки помодулю два второго гейератора 3 кода ошибок, ийдикатороМ неисправностей 101 и К-й подгруппой ЛБК 9(где (к)в с 1 Кв), При этом в каждом блоке 21 Фармируются контрольные разряды по нечетности строк а 1 - а(ч, которые без йзменения проходят через блоки 91 - 9 ы, и йо их"выходам 25 поступают на первый (младший) адреснйй вход соответствующих (и-х) коммутаторбвблоков 111-11 н (для дальнейшей обработки), э нэ выходах 22 блоков 5 каждой 41-4 п 1 разрядов по нечетности столбцов: 1 Ь 1 - 1 Ьп вЬ 1 - вЬп соответственно для в двумерных итерэтивйых кодов; которые без изменения проходят через блоки 9(п), 9(зп),.;., 9(в)и по йх "выходам 25(п 1), 25(2 в),групйы формируются группы контрольных 55 25(м) поступают на первую группу адресныхвходов блоков 11(рп), 11(2 П) 11 ы (также длядальнейшей обработки).Одновременно в групп контрольныхразрядов, сформированных на выходах 21 и22 первого 1 и второго 3 генераторов кодаошибок, поступают (для анализа) на первуюа и вторую ф группы входов индикаторовнеисправностей 101 - 10 п, а однрименные(Ц)-е контрольныеразряды каждой падматрицы НК расположенные соответственнона одном ребре кодовой матрицы трехмерного кода (Фиг, 3): (1 Ь), 2 Ь), вЬД и (аьа(+п),а(и-в+Д, сформированные на выходах 25 логических блоков коррекции 91 - 9 м,поступают(для исправления) на входы соот-.ветствующих блоков свертки Й третьего 6генератора кода ошибок,Работа индйкаторов неисправностей101-10 П в режиме "Запись" начинается припоступлении нэуправляющий (в + в + 1)-йвход каждого из них логической единицы="Зп" Ка 1++ Кав) (КЬ 1+ + КЬп),При отсутствии ошибок Ь 1(Й - в) (и -1 Я- разрядной информации, поступающей вочередном цикле записи на информационные входы 14 устройства, каждоев - 1)(п - . 1 -разрядное сообщение(информационные разряды подматрицы Нк)должно содержать нечетное количество"единиц", Поэтому (при отсутствии неисправностей в самих генераторах 1 и 3 кодаошибок) контрольные разряды по нечетностй строк (Ка 1 - Кав) и столбцов (КЬ 1 - КЬп),сформированные в соответствующей (К-й)подгруппе блоков 2 и 5 и поступающие напервые (а) и вторые ф) входы соответствуюЩего индикатора неисправностей 101 с, также далжйы содержать нечетное количество"едийиц". В данном случае на выходах 16 и17 блока 101 формируется код "00" - признакотсутствия ошибок в контрольных разрядах (Ка 1) и (КЬ 3) подматрицы НК,сформированных нэ выходах 25 соответствующей (К-й) подгруппы блоков 9.Если же на первые а или в 1 орые Рвходы любого блока 101 в режиме "Запйсь"поступает "четная" комбинация, (т.е. содержащее четное количество "единиц"), то нэвыходах 16 и 17 соответствующего блока 10 Кформируется код "11" - "признак ошибкизаписи", т.е. признак оШибки в контрольныхразрядах (Кэ) или (КЬ, сформированныхна выходах 25 соответствующей (К-й) подгруппы блоков 9,Например, если в режиме "Запись" навход 147 поступйт искаженный символ 236(3,1,2), то на вход блока 102 поступят две трехмерного кода, сформированная на вы"четные" комбинации, а на выходе 16 блока ходах 25 блоков 91-9 и;102 появится код "11", в блоке 97 неправиль-1 "(,пЛс) и б" (а,)Лс) - вторая (скорректино сформируется контрольный разряда 7, а - рованная) группа контрольных разрядовв блоке 9 анеправильносформируется конт (а)" и (3 сЬ)" трехмерного кода, сформиро- .рольный разряд 2 Ь 1.: ванная на выходах 23 и 24 генератора 6 кодаЗаканчивается первый этап цикла "За- ошибок, причемпись": ,"с(,пЛс)=б(,п,с)+(уп=-формированиемнавыходе 16 каййого:"мб(,пЛс)А (уп/ сГ(, и, с)л(у и) 3:индикатора неисправностей 10 с управляю б" (е,)Лс) =б(в,Р)+)пч у)И.=щего сигнала (признака ошибки в сфсорми- сГ (а,Яд(а уД)б (пз,)Лс) Л (пз, у.рованной подматрице Нс). который Последниедвеформулы поясняют алго-поступает на второй (старший) адресный ритмработы коммутатора, вслучае, когда онвход соответствующих блоков коммутато-реализует функцию фсложение по" модулюров 11, где(К)аКа; .: ." 15 два":б"=.б+у =(сГ л у 6 ГЛу),т.е. в случае- формированием на прямых 23 иин- формирования на выходе 15 устройства "исверсных 24 выходахтретьего 6 генератора правленного" контрольного разряда:кодаошйбок исправленных контроЛьньх а(вых) = б (,пЛс) или сЬ(вых) = б (в,)Лс),разрядов соответствующей йодматрицй "гс: причем в режиме "Чтение" в каждом комму(а +.уп) и (сЬ + л у, поступающйе на 20 таторе блоков 11 таким же образом реали-третьи (02) и четвертые (ОЗ) информацион зуется (на втором этапе декодирования)ные входы соответствующих блоков комму- исправление любого искаженного сймволататаров 11 ь и (по выходам 23) на элементь - б (ЦЛс) трехмерного кода сформированногоИЛИ 12 .; .". навыходах 25 ЛБК 91-9 и.- формированйем на йервых и вТорых 25 Алгоритмработы коммутатора(каквреконтрольных выходах 16 и 17 устройстважиме "Запись", так и в режиме "Чтение" ) в2 а - разрядного кода ошибки "Записи": случае, когда он реализует функцию "слохсеНКО - НКО, КО 1 - КОп,.:,: :нйепо модулю два": (сГ = б+ ), заключаетНавтором этапе цикла "Запись" вуст-ся в следующемройстве работают блоки 11, 12 п и 13. Блоки 30 если разряд сГ (, ), с), сформированныйкоммутаторов 111 в зависимости ат значе-на соответствуйщем(-м) выходе 25 блока 9,ний управляющих сигналов. (00, 01 или 10, искажен, то на выходе 16 соответствующего11), поступившихна адресный вход соот- блока 10 с присутствует "логическая единивететвующего коммутатора блока 111, йро- ца" (НКОс =. 1), на соответствующем (-м)пускают на выход 15 устройства для заййси 35 выходе 23 блока 6 присутствует "логическая6 память: или зйачения (Оо, 01) контроль-, единица)(у 3-1), а на соответствующем(3-м)ных разрядов (а и сЬ ) соответствующейвыходе 24 блока 6 присутствует "логическийподмэтрйцы Нс; сформированныена выхо-нуль" (у ) =. О),дах 25 блоков 9 (поступившиена младший: . В данном случае на адресньй вход со(первйй) разряд адреса, или значения (02; 40 ответствующего О-го) коммутатора поступаОЗ) исправленных контрольных разря- . ет комбинация "два": 10 (если искаженныйдов (а+ уп) и(сЬ + ту) соответствую-. символб=0)иликомбинация "три":11(еслищей подматрицы Нс, сформированные.: искаженныйсимволб=1).соответственнона выходах 23 или 24 гене-. В первом случае (б = О) на выход 15ратора 6 кода ошибок45 устройства пропускается "логическая единица", т.к. на информационнйй вход (О 2)Формирование на выходах 15 устройст- данного коммутатора поступает значениева третьей группы окончательно скорректи- разряда синдрома ( у)- 1) - с выхода 23рованных значений контрольных разрядов блока 6,а(вых) и сЬ 3(вых) происходит в соответству Во втором случае (б = 1) на выход 15ющих коммутаторах каждого блока 11 по устройствапропускается "логический нуль",формуле:.: т,к. на информацйонный вход(О 3) данногоа(вых) = б" (,п,с) = НКОМб(.пЛс)3 Ч коммутатора поступаетинверсное значениечНКОс Л б" (1,пЛсИ;, разряда синдрома (у= О) - с выхода 243 сЬ(вых) = б"(а,Р) = Н КОМ б (аьсИ 55 блока 6,ч Н КОс гб" (пъ,Р)3, Таким образом в каждом коммутаторегде б (,п,с) и сГ (е,)Лс) - первая группа зна- . блоков 11 "исправление" (на втором этапе)чений контрольных разрядов (а) и (3 сЬ любого искаженного символа б" (, ), с),сформированного на выходе 25 блоков 9 происходит поормуле: д(вых) = (Н К 03 с б" ) = (Н К 03 с (сГ + уАлгоритм работы коммутатора(как в режиме "Запись". гак и в режиме " тение") в 5 случае, когда он реализует функцию: (д(вых) = Н КОК (д , заключается в Следую. щем: если разряд сГ(1,), к), сформированный на соответствующем и-м) выходе 25 блока 9 ь не искажен, то на выходе 16 соответствую щего блока 10 К присутствует "логический нуль" (НК 01 с = О).В данном случае на адресный вход соответствующего О-го) коммутатора блока 11 поступает комбинация "нуль": 00 (если не-. 15 йскаженный символ д = О) или комбина-ция "один": 01 (если неискэже"нй"ый: символ сГ =1),В первом случае (д = О) на выход 15 пропускается "логический нуль", т.к, на ин формационный вход (00) данного коммутатбра поступает значение младшего разряда адреса (б = О) с выхода 25 блока 9.Во втором случае (д =, 1) на выход 15 устройства пропускается "логическая еди ница", т.к. на информационный вход (01) данного коммутатора (также как ив-первомслучае) поступает значение младшего Раз- ряда адреса (б = 1) с выхода 25 блока 9 ьВ общем случае (на втором этапе коди рования или декодирования), работа каждого (3-го) коммутатора блока 11 (фиг. 4) зэпРограммйрована по формулесГ" (Ц,1 с) = НКОК л сГ (Ц,К) / НК 01 с /Л б(Ц,К)+ Зу; :35 где: у ) = сГ (Ц,1)+,+ сГ (Ц,гл).Работа блока 13 в режиме "Запись" заироограммйрованапо формулам "НпЗп = (НКО 1 КН 2)кч(НКОпКОп);"Ка" =ЦКОИКПр Нщ 1 О 1 КОКПаа л (Н КОк КО-ф Н КО+1 КО +1) К Л рП 0 7 о,; "НКО" ="Кб" (НпЗпНпв), . где: "Нпщ"-ву 1 чч глу и. 45При этоМ "исправление" искаженного символа д (ЦЯ, сформированного (на первом этапе кодирования или декодирования) на выводе 25 блока 9, реализуется в комму тэторах блока 11 методом "адаптации";отключением от выходов 15 устройства выходов 25 (б) блока 9 ь и подключением к выходам 151 устройства выходов 231 или 24 (д" ) блока 6. 55Работу устройства в режиме "Запись" удобно рассмотреть для одного конкретного случая его примейения, например, при реализации в нем (64, 32) модифицированного трехмерного кода (фиг. 3) с параметрами: п=4, гп =4, И=16,В данном случае на девятый (управляющий вход каждого блока 101 - 104 со входа 20 устройства поступают "логическая единица", настраивающая индикаторы неисправностей на работу в режиме "Запись",Одновременно на входы 141 - 1416 устройства поступают для кодирования 16 четырехразрядных сообщений, например;(Н 1) 1000(1) 011 о (2) 0110 (3) оООсЕ(4) (Н 2)-+ 1000 (5) 0119 (6) 0110 (7) 0000 (8) (Нз 1 1000 (9) 0110 (10) 0110 (11) 0000 (12) (Н 4) -ф 1000 (1 3) 0110 (14) 0,110 (15) 0000 (1 6) где в скобках указан номер (1) строки трехмерного кода(64, 32), стрелками(-) указаны разряды подматрицы (Н 1 двумерного кода, а йулевые значения контрольных разрядов (а 1 и КЬ, подлежащих кодированию - подчеркнуты.Таким образом на входы 14 устройства поступают 36 информационных и 28 контрольных (нулевых) разрядов, причем значения разрядов (С входного кода, поступающих на входы 14(1 з 1 - 14(15) устройства, при отсутствии ошибок удовлетворяют соотношениям:1 С 1 = 1 СО+ 2 СО+ ЗСО,2 С 1 = 131 + 231 + 331,ЗСЗ = 138+ 238+ 338.В блоках 2 и 5 первого 1 и второго 3генераторов кода ошибок происходит формирование на выходах 21 и 22 кбнтрольныхразрядов строк (а) и столбцов (МЬД) соответ- .ственно для четырех двумерных итеративных кодов, как описано в(21,Например, контрольный разряд а 7 формируется на инверсном выходе 21 блока 27по формуле:2 аЗ = 236+ 237+ 238+ "1" = 0+ 1+ 1++1=1,а контрольный разряд 2 Ь 1 формируется на .инверсном выходе 222 блока 51 по формуле:2 Ь 1 = 2 СО+ 233 + 236+ "1" = 1+ О+ О+ 1 =На входы а и Р каждого блока 101-104 поступает комбинация (0111 0111), свидетельствующая об отсутствии ошибок в каждом девятиразрядном информационном сообщении: (100 011 011), поступившем на соответствующую подгруппу входов: 141-14 з, 145-147, 149 - 1411 и 141 з - 1415 устройства, поэтому на выходах 16 и 17 устройства формируется восемь логических нулей: НК 01, НК 02, НКОз, НК 04 и К 01, К 02, КОз, К 04.Одновременно 28 контрольных разрядов, сформированных на выходах 21 и 22(Н 1, Нз, Н 4) о подматрицы ом этапе кодии выходах 25 етное (непраи будет иметь еннйх символа блоков 1 и 3, без изменения проходят (фиг. .2) на выходы 25 блоков 91-916, т.к; на входы соответствующих мажоритарных элементов 28 блоков 9, формирующих контрольные разряды а, или Мь), поступает или комбина ция (О, а 1, 1) или.комбинация (О, 1, Кь, поэтому на адресные входы 16 и 25 соответствующих коммутаторов блоков 11, формирующих контрольйые разряды а(вых) и Кь)(вых) для записи в память (фиг. 4), по ступает или комбинация (О, а) или (О, КЬ, а на выходах 234 третьего 6 генератора када ошибок формируются четыре "логических нуля" по формулам:4 у 1 = 1 Ь 1+ 2 Ь 1+ ЗЬ 1+ 4 Ь 1 = О 15 4 у 2 = 1 Ь 2+ 2 Ь 2 + ЗЬ 2+ 4 Ь 2 = 0 4 у З=1 ЬЗ +гЬЗ+ ЗЬЗ +4 ЬЗ =О 4 у 4 = а 4 - а 8+ а 12+ а 16 = 0 .-:На этом первый этап цикла "Запйсь" заканчивается..20На втором этапе работают блоки 111-1116, 124 и 13 (блоки 121, 122 и 12 з в режиме "Запись" не участвуют),На выходе 18 блока 124 формируется "логический нуль" по формуле: : 25Нп 4=4 у 11 4 у 2 г 4 у 3 44 у 4 = 0, на выходе 19 устройства формируется код "0000" - признак отсутствия ошибок в режи-. ме "Запись", а на выходах 15 устройства-, связанных с соответствующими входами 16 30 блоков памяти;,формируются 28 контрольных разрядов трехмерного кода (64, 32), поступивших на первые (Оо) и вторые (01) информационные входы соответствующих коммутаторов блоков 11 с выходов 25 бло ков 9..Таким образом, четыре 16-разрядныхкодовых слова подматрц Н 1 - Н 4 (фйг. 3), сформированные для записи в память на входах 14 устройства (информационные 40 разряды) и выходах 15 устройства (контрольные разряды), содержат четное (правильное) количество "единиц" и будут иметь вид:45- (Н 1. Н 2 НЗ Н 4) Значения девяти информационных и семи контрольных разрядов, располагаются 50 (для наглядности) на соответствующих им позициям в каждой плоскости кодовой матриць 1 трехмерного кода, контрольные разряды строк и столбцов отделены.В конце цикла "Запись" в каждый из 16 55 блоков памяти записывается соответствующая строка сформированного трехмерйого кода (64, 32), при этом в первый, пятый, девятый и 13-й блоки памяти записывается комбинация (1000), а в остальные 12 блоков памяти - комбинация (011 1).Рассмотрим конкретный случай "исправления" одиночной ошибки, внесенной в 36-разрядное входное сообщение в режиме "Запись" методом "адаптации". (исправлением двух неправильно сформировайных контрольных разрядов).В данном случае на входы 14 устройства поступают три девятиразрядные комбинации: 100 011 011, содержащие нечетное (правильное) количество единиц и одна "четное" девятиразрядное сообщение,. например. с искаженным (О -+ 1) символом 236 (подчеркнут): 100 011 111, Согласно подматрице Н 2 (фиг. 3), на выходе 21 блока 27 и йа выходе 222 блока 51 неправильно сформируются два контрольййх разряда: а 7 = "0" (вместо "1") и 2 Ь 1 = "1" (вместо "0" ) по формуле: 2 аЗ =. 1+ 1+ 1+ "1" = 0 2 Ь 1 = 1+ О+ 1+ "1" =1 На входы блоков 101, 10 з и 104 поступает комбина ция (0111 0111), свидетел ьствующая об отсутствии ошибок в первом, третьем девятиразрядном сообщении (100 011 011), а на входы блока 102 поступа ет комбинация (0101 11.11), свидетельствующая об одиночной ошибке во второй подгруппе входов 145 - 14 в устройства, в результате чего каждое 16-разрядное кодовое слово подматриц н 1, Нз й н 4, сформированное на первом этапе кодирования.на соответствующих входах 14 устройства и выходах 25 блоков 9, будет иметьвид: а 16-разрядное кодовое слов Н 2, сформированное нэ перв рования на входах 145-14 з блоков 95-9 в, содержит не вильное) количество единиц вид (подчеркнуты три искаж 236, а 7 и 2 Ь 1):1000О 1111111 Ю - (Н 2) На контрольных выходах 161, 16 з и 164 устройства формируются "логические нули", поступающие на старший адресный вход коммутаторов блоков 111 - 114, 11 э, 111 з - 1116, пропуская на соответствующие выходы 15 устройства (по входам Оо и 01) коммутаторов) значения контрольных разрядов подматриц Н 1, Нз и Н 4, сформированные на первом этапе кодирования (на выходах 25 блоков 9),

СмотретьЗаявка

4854339, 07.06.1990

НАУЧНО-ПРОИЗВОДСТВЕННОЕ ОБЪЕДИНЕНИЕ "АГАТ"

ВОЛОВНИК АРКАДИЙ АВРАЛЬЕВИЧ, САВИНОВА АЛЕКСАНДРА БОРИСОВНА

МПК / Метки

МПК: G11C 29/00

Метки: исправления, обнаружения, ошибок

Опубликовано: 30.12.1992

Код ссылки

<a href="https://patents.su/21-1785041-ustrojjstvo-dlya-obnaruzheniya-i-ispravleniya-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обнаружения и исправления ошибок</a>

Предыдущий патент: Запоминающее устройство с автономным контролем

Следующий патент: Устройство для диагностирования оперативной памяти

Случайный патент: Барабан ленточного конвейера