Многоразрядный генератор испытательных последовательностей

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1133589

Авторы: Громаковский, Левина, Тюпин

Текст

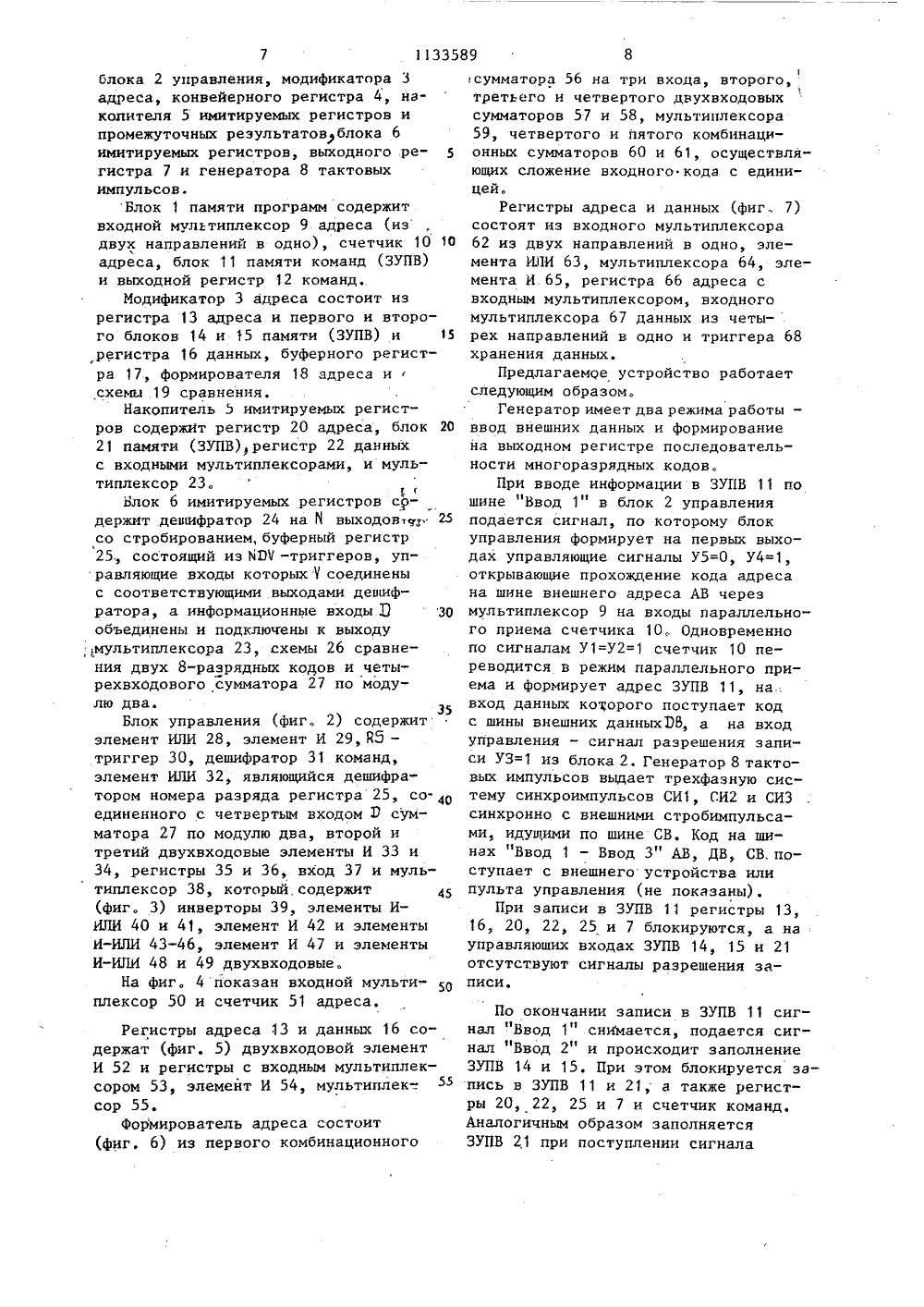

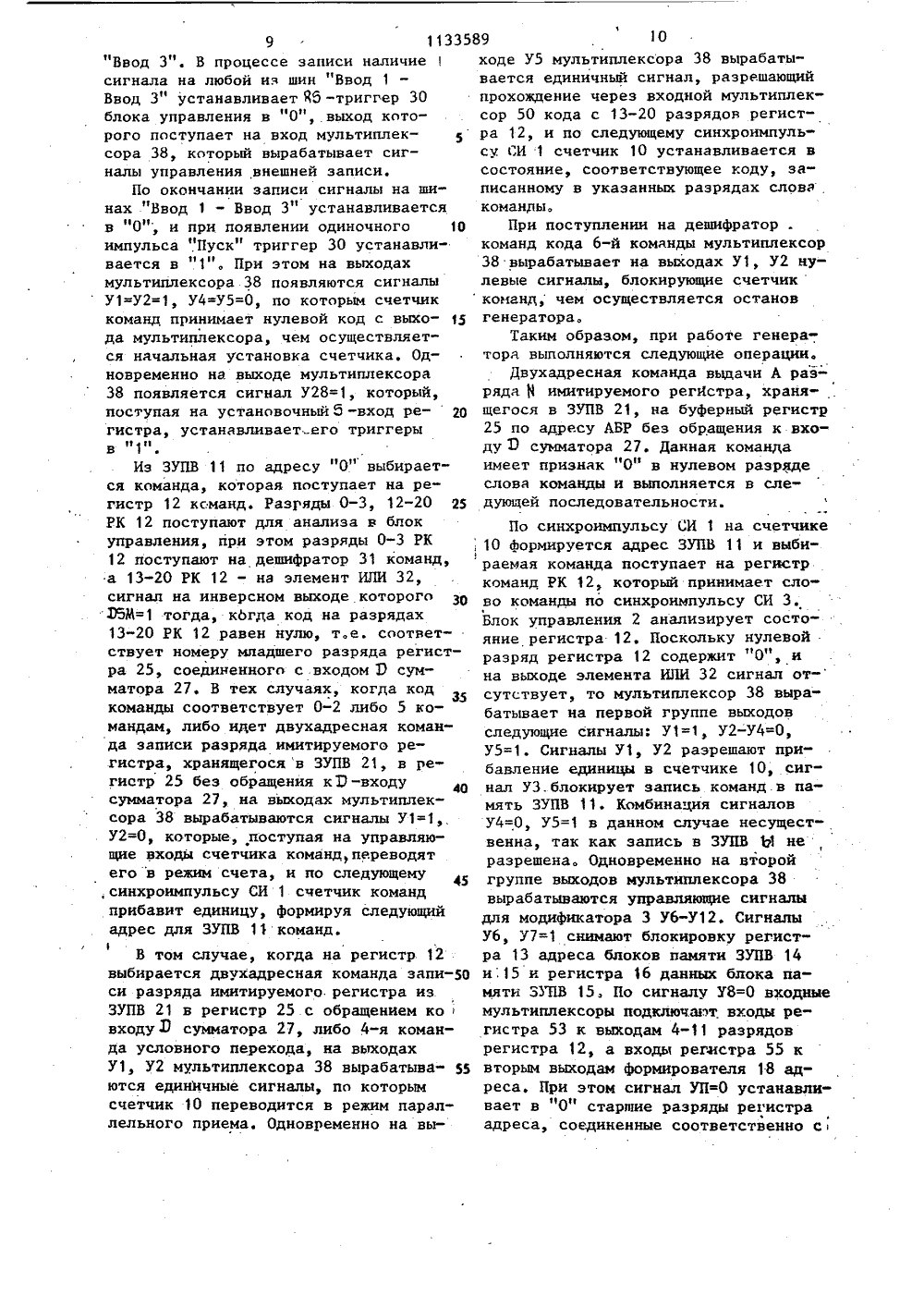

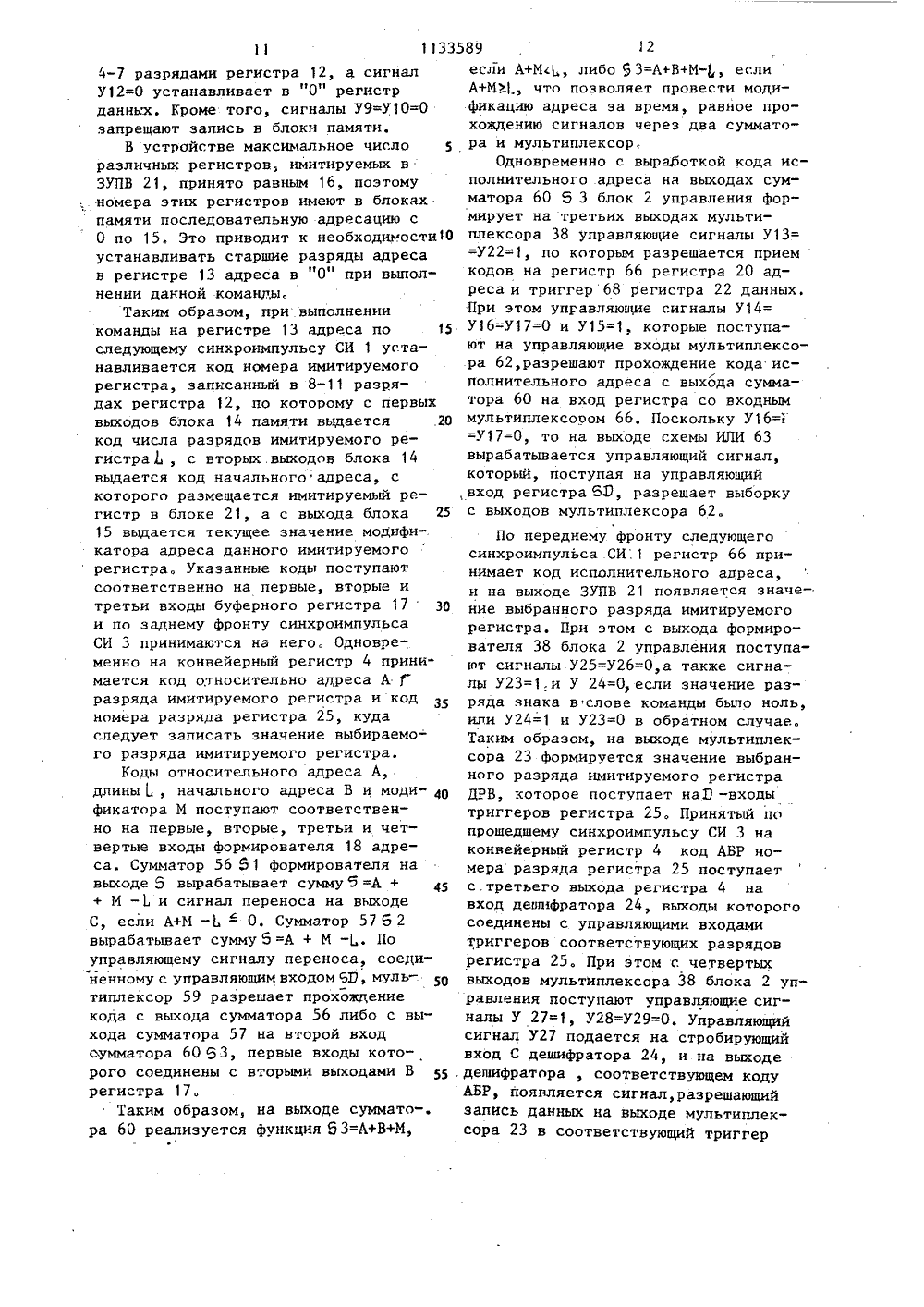

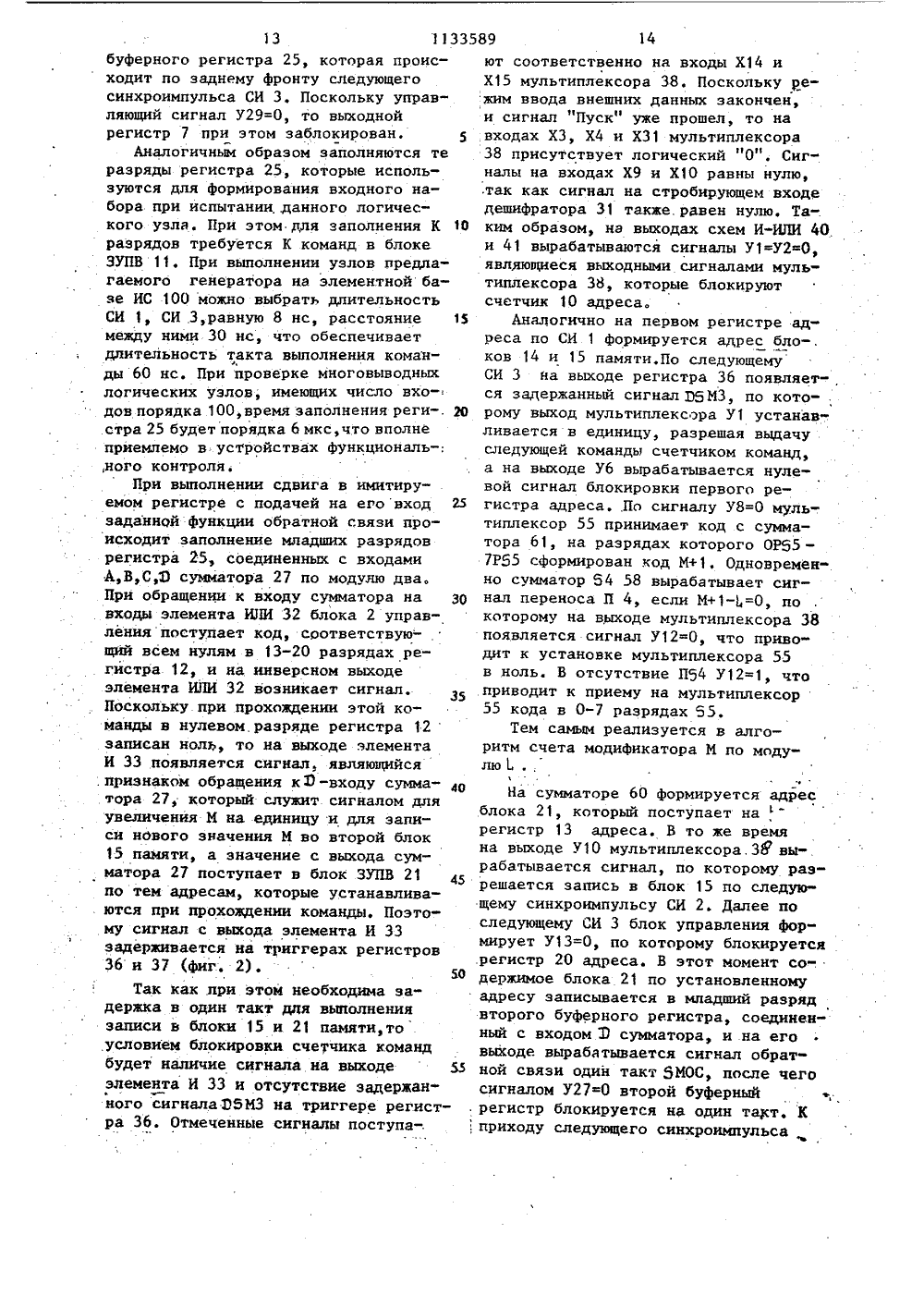

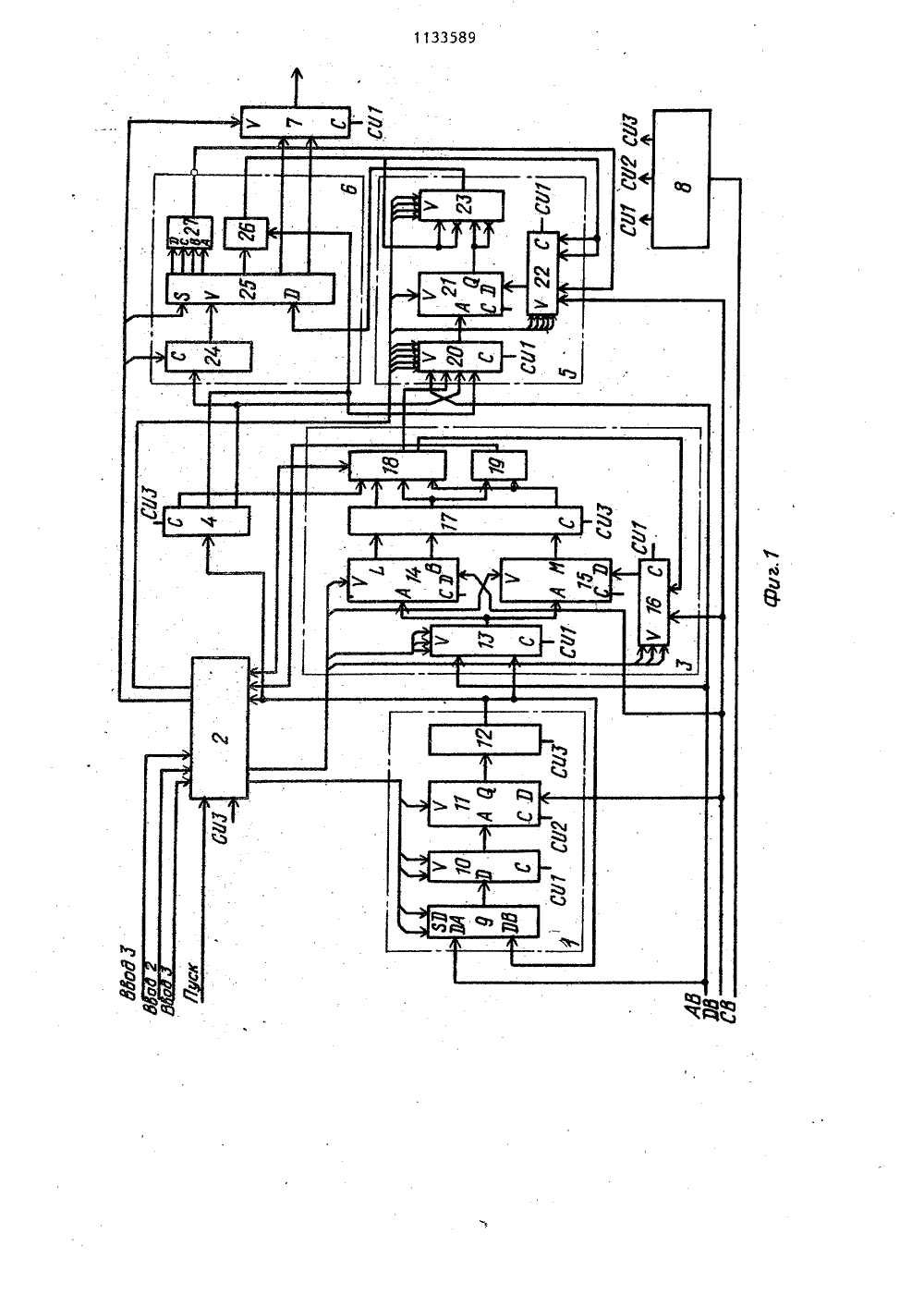

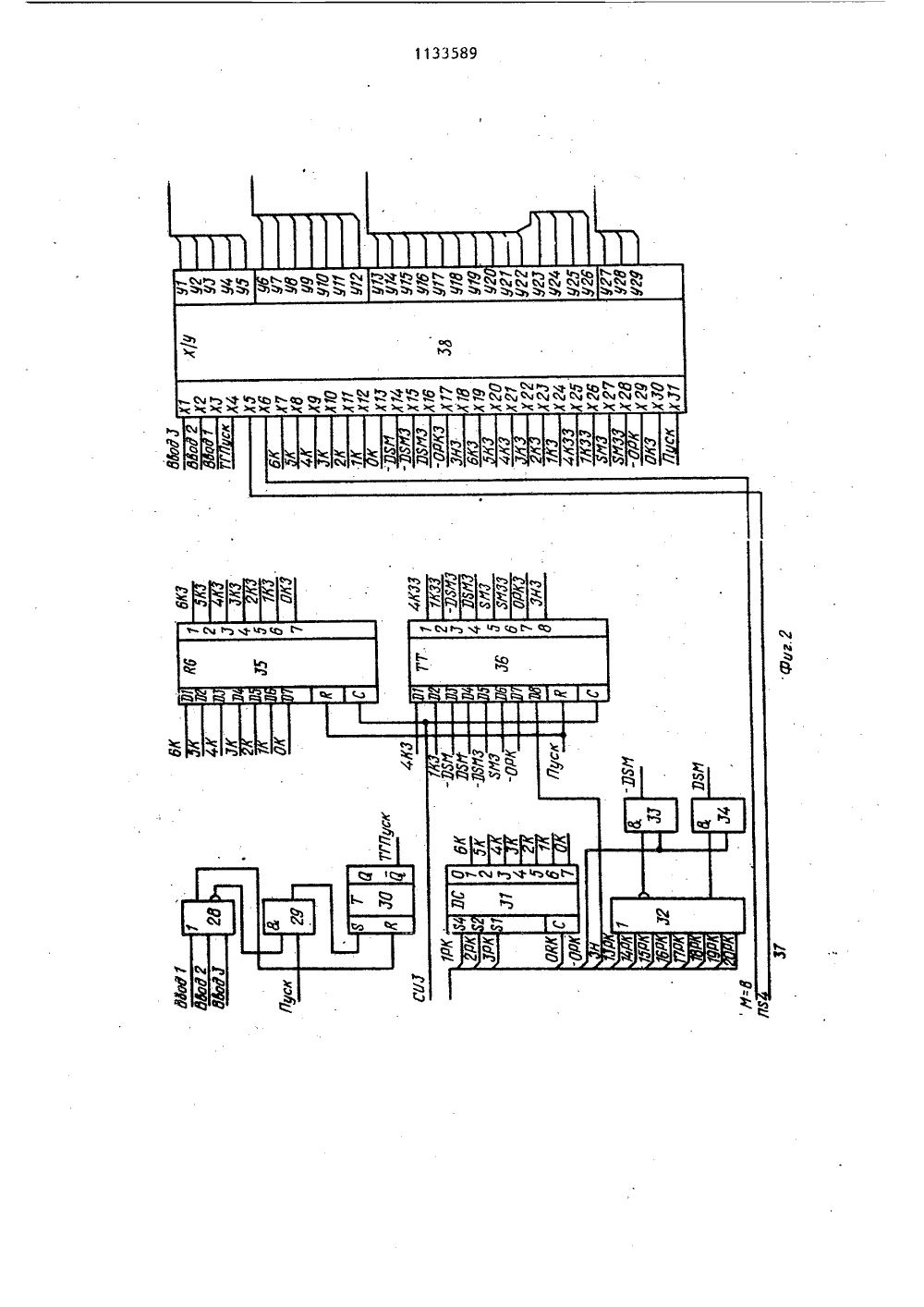

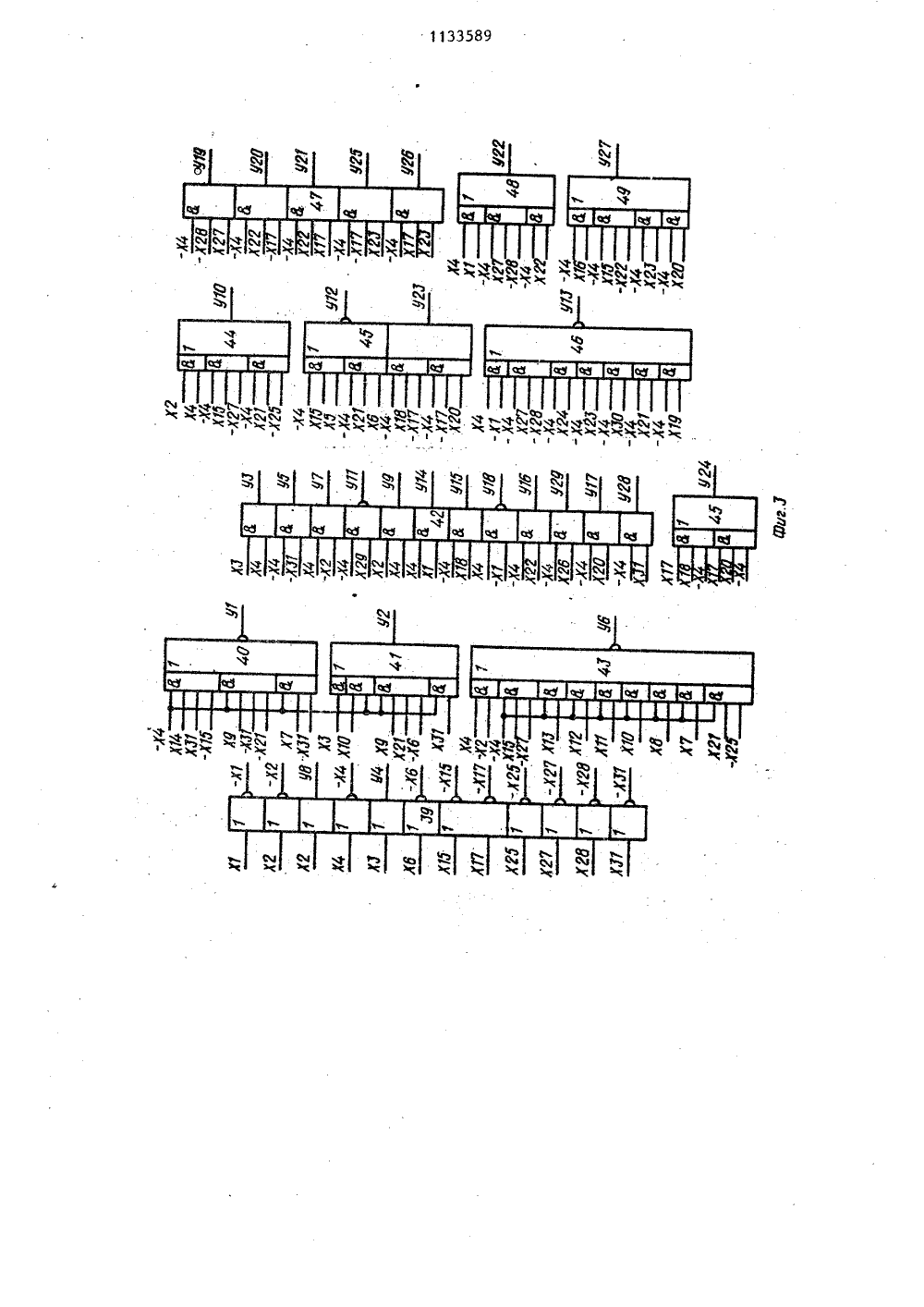

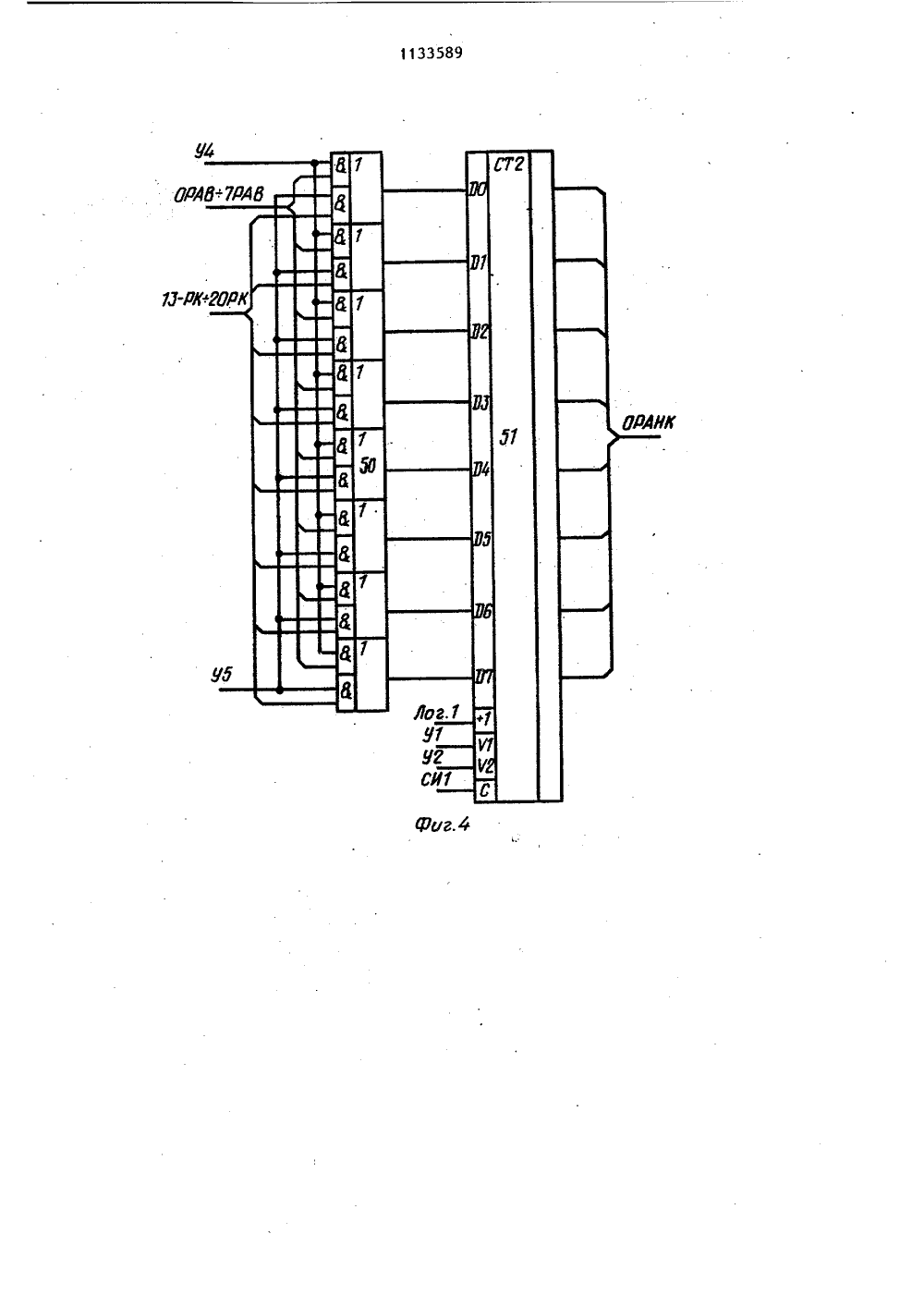

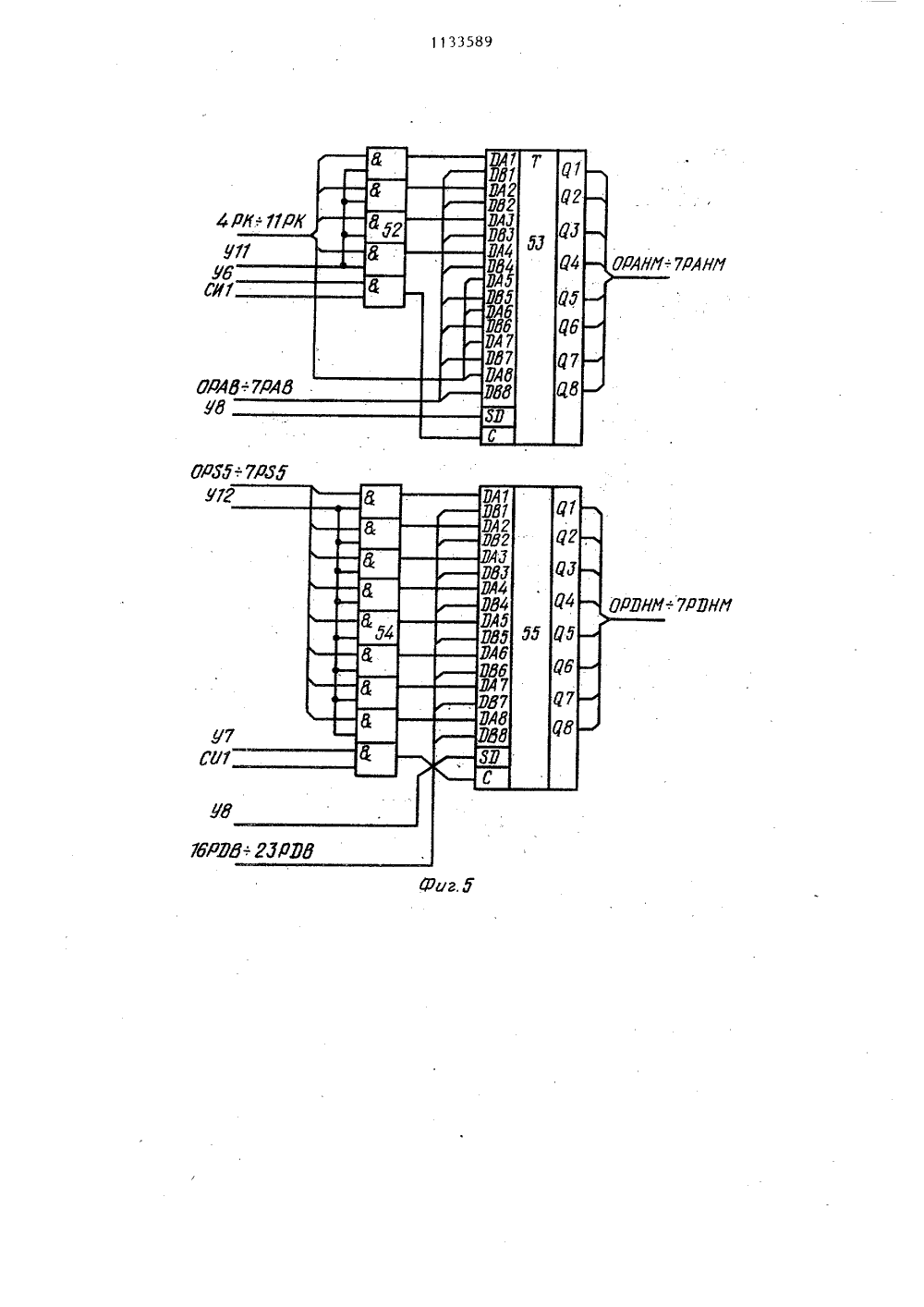

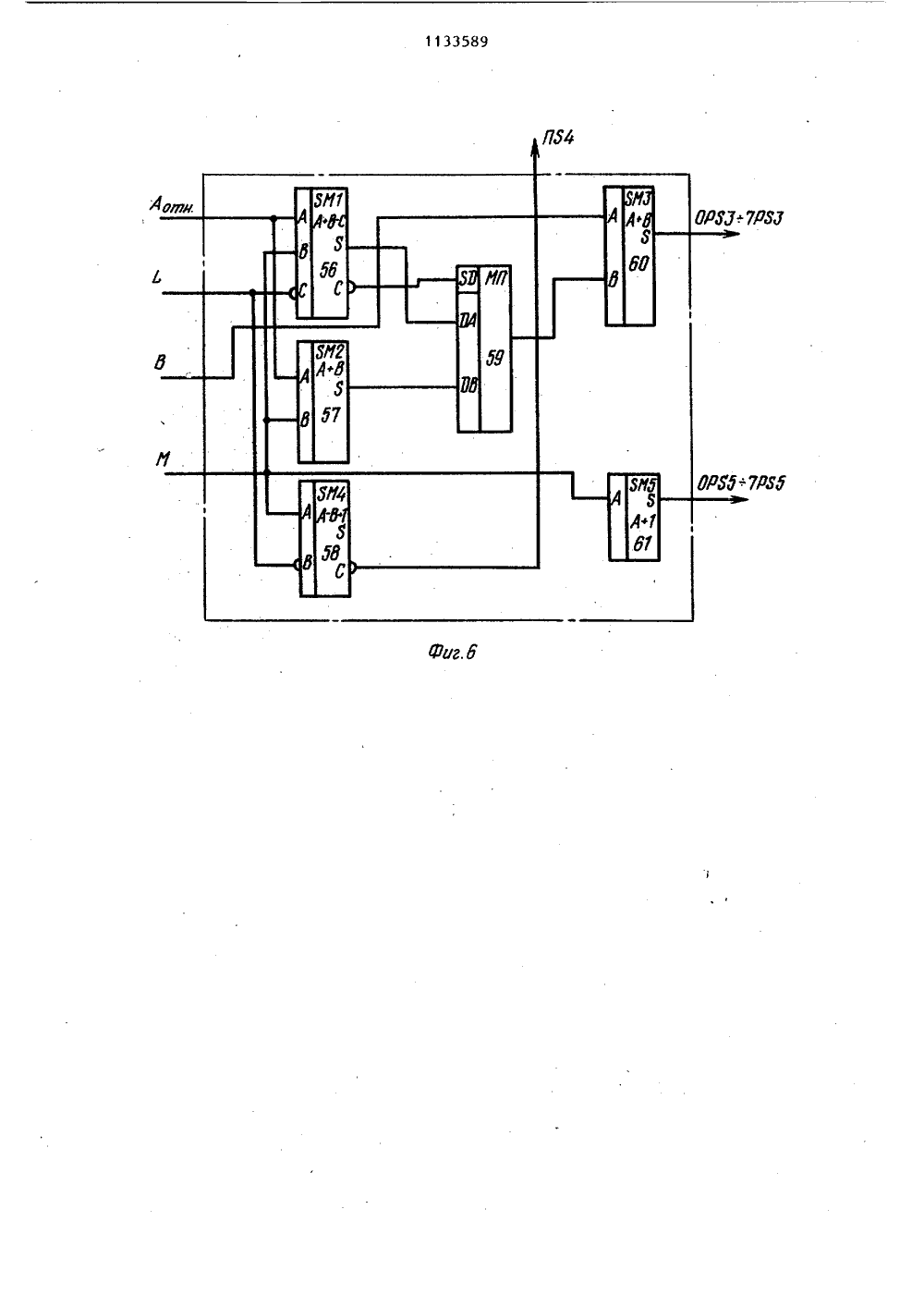

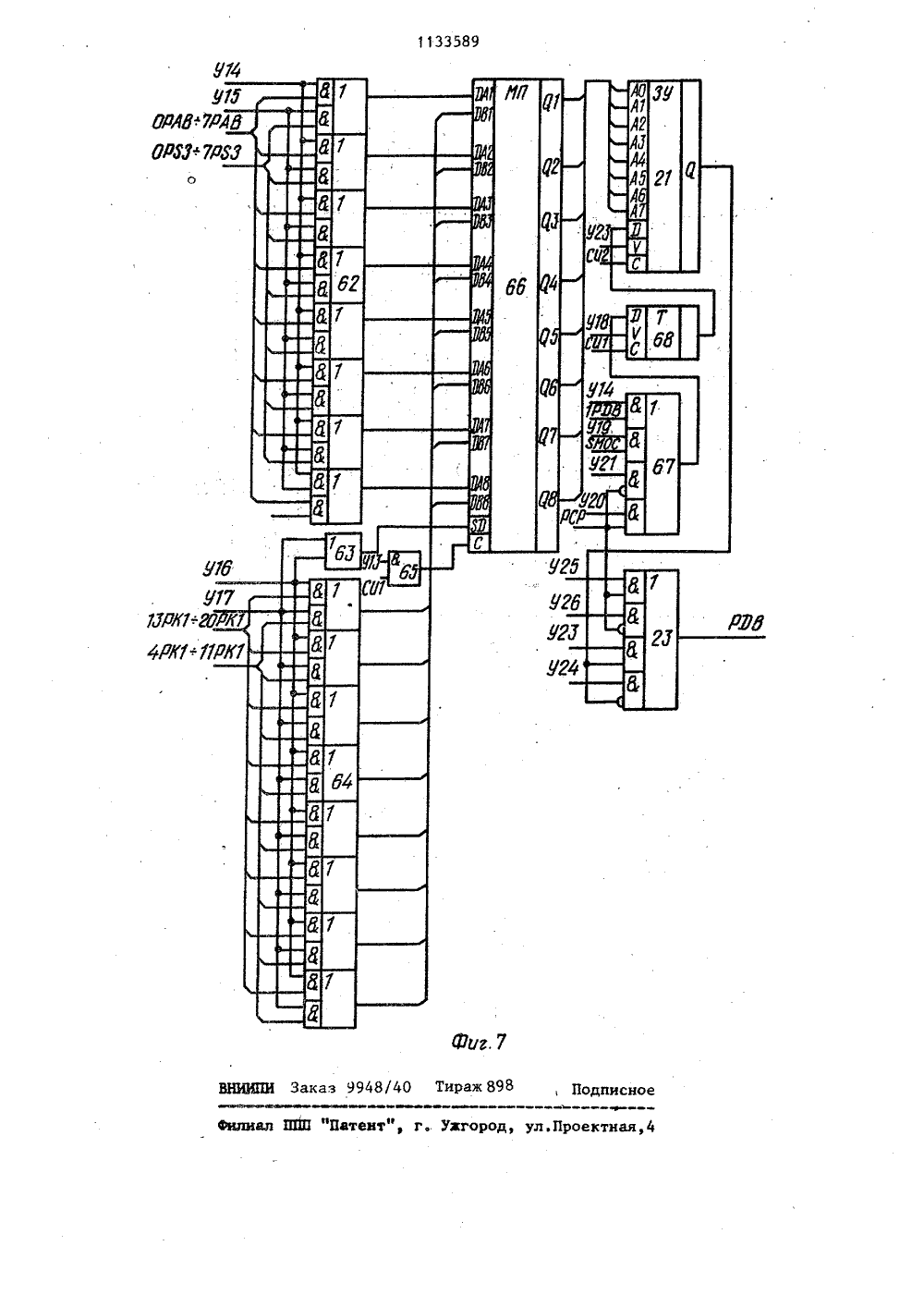

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК А 09) (111 4(51) С 06 Р 1/04 ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬГПФОПИСАНИЕ ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(56) 1. Патент США 9 4047008,кл. С 06 Р 7/00, опублик. 06.09.77.2. Авторское свидетельство СССР У 991397, кл, С 06 Р 1/04, 1981.(54)(57) ИНОГОРАЗРЯДНЬЫ ГЕНЕРАТОР ИСПЫТАТЕЛЪНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ, содержащий блок памяти программ, модификатор адреса, накопитель имитируемых регистров и промежуточных результатов, блок имитируемых регистров и генератор тактовых импульсов, нри этом модификатор адреса содержит регистр адреса, регистр данных,два блока памяти, буферный регистр и формирователь адреса, блок имитируемых регистров содержит дешифратор, буферный регистр и сумматор по модулю два, накопитель имитируемых регистров и промежуточных результатов содержит регистр адреса, регистр данных и блок памяти, при этом адресный вход блока памяти программ объединен с первым адресным входом регистра адреса модификатора адреса, с первым адресным входом регистра адреса накопителя имитируемых регистров и промежуточных результатов и является входом внешнего адреса многоразрядного генератора испытательных последовательностей, информационный выход блока памяти программ подключен к второму адресному входу регистра адреса модификатора адреса, стробирующие входы записи блока памяти накопителя имитируемых регистров и промежуточных результатов и блоков памяти модификатора адреса объединеныс первым стробирующим входом блокапамяти программ и подключены к первому выходу генератора тактовых импульсов, входы синхронизации регистровадреса и регистров данных модификатораадреса, накопителя имитируемых регистров и промежуточных результатов объединены с вторым синхронизирующим входомблока памяти программ и подключены квторому входу генератора тактовыхимпульсов, входы синхронизации буферных регистров модификатора адреса иблока имитируемых регистров объединены с третьим синхронизирующим входом блока памяти программ и подключе 1ны к третьему выходу генератора тактовых импульсов, выход регистра адреса подключен к адресным входампервого и второго блоков памяти модификатора адреса, информационныйвход первого блока памяти модификатора адреса объединен с информационным входом блока памяти программ .и с первым информационным входом регистра данных модификатора адреса ирегистра данных накопителя имитируемых регистров и промежуточных результатов и является входом внешнихданных. многоразрядного генератора испытательных последовательностей, выходы первого,и второго блоков памятиподключены к соответствующим информационным входам буферного регистрамодификатора адреса, первый, второйи третий выходы буферного регистрамодификатора адреса подключены квходам данных адреса, начального адреса, адреса входного смещениА фор 1133589 16Си 1 мультиплексор 38 блока управле- . ния формирует сигналы У 18=1, разрешающие прием на триггер 68 регистра данных, У 14=У 20=У 21=0, У 1.9=1, по которым на вход 3 триггера 68 поступа ет сигнал 5 МОС через мультиплексор 67, Одновременно сигналом У 22=1 разрешается запись в блок 21 памяти, и следующим синхроимпульсом Си 2 производится запись. При следующих обращениях к имитируемому в блоке 21 регистру модификация адреса происходит со значением М = (М+1)во 31., что эквивалентно сдвигу регистра на один разряд влево, причем значение выхода 5 МОС окажется записанным в его правый разряд.После заполнения требуемых разрядов буферного регистра 25 полученный набор может быть одновременно выдан О на испытуемый объект по команде выдачи содержимого буферного регистра 25 на выходной регистр 7. Данная команда имеет номер ноль, и при ее появлении на регистре 12 команд по СИ 3 блок 2 управления формирует управля.ющие сигналы У 1=1 и У 2=0, чем обеспечивается переход к следующей команде, Сигналами Уб=У 10=0 блокируется регистр 12 адреса, а также запись в ЗО блок 15, По следующему СИ 3 сигналами У 13=У 22=У 27=0 блокируется регистр 20 адреса, запись в блок 21 памяти и запись в буферный регистр 25, а по сле- дующему СИ 3 блок 2 управления выра батывает сигнал У 29=1, который разрешает прием на выходной регистр 7 кода, с третьих выходов буферного регистра 25, По следующему синхроимпульсу СИ,1 происходит выдача многораэряд ного кода на выходы генератора.Следует отметить, что данная команда позволяет сформировать многоразрядный код, изменение которого в одном разряде может происходить каж дые два такта работы генератора. Для этого достаточно в программе записать чередующуюся последовательность команд выдачи и команд считывания из блока 21 на регистр 25. Если 50 длительность такта генератора равна 60 нс, то с помощью команды выдачи на любом выходе генератора появляются испытательные стробимпульсы с минимальной длительностью 120 нс, что 55 существенно расширяет функциональные возможности предлагаемого генератора по сравнению с известным. Для деформирования кодов, разряды которых могут иметь функциональную зависимость, в систему команд генератора введены первая и вторая команды и, кроме того, схема 26 сравнения,первые входы которой соединены с 1 вторыми выходами буферного регистра 25, а вторые входы - с вторыми выходами конвейерного регистра 4.Принцип формирования произвольной логической функции от переменных, в качестве которых берутся разряды имитируемых регистров, заключается в следующем.Если на первые входы, например 4-входовой схемы сравнения, подать сигналы с разрядов А В СЗ имитируемых генераторов, а на вторые - код 1010, то навыходе схемы сравнения реализуется функцияГ,= АВ Сй.Далее значение этой функции можно записать в промежуточную память, подать на вторые входы схемы сравнения код 0101 и получить на выходе функциюР =АВС 2.Повторяя эту процедуру, получаем набор функций Г;, хранящихся в промежуточной памяти.Считывая инверсные значения Г; из промежуточной памяти на первые1 входы схемы сравнения, подадим на ее вторые входы код 1111 и получим на выходе функциюф - гзЗаписав инверсное значение ф в требуемый разряд буферного регистра 25, получим на его выходе значение ф = Р + Г 2+Г+ГФ А огичн й резул = тат получается, .если считать прямые значения и сравнить с кодом 0000,Данная программа .требует четырех команд считывания переменных А,ВАСЯ "трех команд сравнения и записи в про-. межуточную память (команда вычисленияможет быть выполнена как команда вычисления и записи инверсного значения Г,1 в требуемый разряд .буферного регистра), трех команд считывания из промежуточной памяти на буферный регистр и команды сравнения и записи результата на буферный регистр, т.е.11 однотактных команд.Команда 1 выполняется в один такт и проходит в следующем порядке. При появлении на регистре команд по синКоманда 2 выполняется в следующем порядке. После приема по заднему фронту СИ 3 команды на регистр 12 команд блок 2 управления сигналами У 1=1, У 2=0 подготавливает счетчик команд к выборке следующей по порядку команды, а по УЗ 0 блокируется запись в блок 11 памяти. Одновремен 55 1133589хроимпульсу СИ 3 кода первой команды блок 2 управления на первых выходах мультиплексора 38 вырабатывает управляющие сигналы У 1=1, У 2=0, по которым счетчик 10 адреса устанавлива-ется в режим счета, УЗ=0, чем блокируется запись в блок 11 памяти, значения сигналов У 4=0 и У 5=1 при этом несущественно для прохождения команды.На второй группе выходов мульти плексора 38 вырабатываются сигналы управления модификатором 3 адреса У 6=0, У 9=У 10=0, По сигналу У 6=0 блокируется регистр 13 адреса, а сигналами У 9=У 10=0 запрещается запись в блоки . 1 14 и 15 памяти, Остальные сигналы У 7, У 8, У 11 и У 12 при этом несущественны. По следующему синхроимпулъсу СИ 3 происходит передача содержимого регистра команд на конвей ерный регистр 4. Одновременно блок управления вырабатывает сигналы У 13= =О, У 22=0., по которым блокируется регистр 20 адреса и запись в блок 21 памяти, и сигналы У 24=1 и У 26=0, если 25 значения разряда знака 12 РК=О, или У 25=0 и У 26=1, если значение разряда знака. 12 РК=1, при этом У 23=У 24=0. Тем самым мультиплексор 23 разре-., шает прохождение прямого либо инверсного результата сравнения на выходе схемы 26 сравнения на информационный вход второго буферного регистра 25.Одновременно на стробирующий вход дешифратора 24 приходит разрешающий д сигнал У 27=1, на,информационные входы - код с третьих выходов конвейерного регистра 4, а на вторые входы схемы сравнения - код с вторых .выходов регистра 4.. 40Тем самым к моменту прихода следующего синхроимпульса СИ 3 на 9 -вход соответствующего триггера регистра 25 поступает разрешающий сигнал, а . на,О -вход - прямой либо инвертированный результат сравнения кода на первых входах схемы 26 с кодом на вторых выходах регистра 4. По заднему фронту СИ 3 результат записывается в выбранньй триггер регистра 25. О 18но вырабатываются сигналы У 6=У 9=У 10, по которым блокируется регистр 13 адреса и запись в блоки 14 и 15. По. заднему фронту следующего СИ 3. содержимое регистра 12 принимается на регистр 4, а блок 2 управления вырабатывает У 13=1, У 14=У 15=У 17=0 и У 16=1, по которым регистр 20 адреса . принимает код с третьих выходов регистра 4.Одновременно на вторые входы схе-, мы 26.сравнения поступает код с вто-: рых выходов регистра 4, результат сравнения поступает на вход мультиплексора 67 регистра 22 данных. С выхода мультиплексора 38 блока 2 управления на управляющие входы триггера 68 приходит разрешающий сигнал У 18=1, а на входы мультиплексора 67- сигналы У 20=1 и У 21=0, если записывается прямое значение результата сравнения, и У 20=0, У 21=1 - если инверсное. По следующему синхроимпульсу СИ 1 регистр 66 и триггер 68 принимают значение адреса и данных для блока 21. При этом на вход блока 21 поступает разрешающий сигнал У 22=1, и по следующему синхроимпульсу СИ 2 происходит запись в блок 21 памяти. Вместе с тем У 27=У 28=У 29=0, чем обеспечивается блокировка регистров 25 и 7Третья и четвертая команды явля-. ются командами безусловного и условного перехода. Введение их в состав команд генератора обеспечивает организацию циклов в программе, что позволяет существенно сэкономить память 11 команд при имитации регистров, работающих с различными частотами сдвигов.Команда 3 выполняется следующим образом. При поступлении на регистр 12 команд кода команды по синхроим- пульсу СИ 3 на выходе мультиплексора 38 блока 2 управления вырабатываются управляющие сигналы У 1=У 2=1 и УЗ=О, которыми счетчик команд переводится в режим приема данных с выхода мультиплексора 9, а запись в память 11 команд блокируется. Управляющие сигналы У 4 0 и У 5=1 разрешают прохождение кода следующей команды с регистра команд на выход мультиплексора 50 (фиг. 4), Одновременно вырабатываются сигналы УЬУ 9=У 10 О, блокирующие регистр 13 адреса и запись в блоки 14 и 15По следующемуСИ,1 счетчик 10 адреса принимает код с регистра команд. По следующему СИ 3 вырабатываются сигналы У 13=У 22= =О, блокирующие регистр 20 адреса и запись в блок 21 памяти, а также 5 У 27=0, поступающий на С-вход дешифратора 24, блокируя тем самым запись в регистр 25. По следующему СИ 3 сигналом У 29=0 запрещается прием на выходной регистр 7.10Команда 4 выполняется в два такта, поскольку необходимо время на форми-. рование условия перехода. При вводе данных в блок 14 по выбранному адресу записывается код конечного зна чения счетчика циклов В, а в блок 15 по тому же адресу - начальный нулевой код счетчика циклов М = О. Таким образом, счетчиком циклов является слово с данным адресом в блоке 15. 20 При поступлении на регистр 12 кода скоманды по СИ 3 блок 2 управлеия вырабатывает У 1=У 2=0 и УЗ=О, чем блокирует счетчик 10 адреса и запись в блок 11. 25Одновременно формируются У 6=У 7=1, У 8=У 9=У 10=0, У 11=1, У 12=1, Сигналами У 6 и У 7 разрешается прием на регистр 53 регистра 13 адреса и мультиплексор 55 регистра 16 данных, сигналами 30 У 8, У 11,и У 12 разрешается прохождение на триггера регистра 53 кода с 4-11 разрядов регистра команд, а на триггера регистра 55 - кода с выхода сумматора 615 5 0-7 Р 35, По следующе- З 5 му СИ 1 на регистр адреса принимается адрес слова в блоках 14 и 15, в котором записано конечное состояние счетчика циклов В и его текущее значение М. Эти данные поступают соот- м 0 ветственно на второй и третий входы буферного регистра 17 и по заднему фронту следующего синхроимпульса СИ 3 запоминаются на нем. Одновременно блок управления вырабатывает сиг налы У 13=У 22=У 27=0, блокирующие регистр 20 адреса, запись в блок 21 ив регистр 25,и сигнал У 10=1,разрешающий запись в блок 15.При этом на первых , входах схемы 19 сравнения находится 50 код конечного состояния счетчика циклов, а на вторых входах - код текущего значения.Если эти коды совпадают (М=В), то выходной сигнал схемы 19 сравнения, 55 поступающий в блок 2 управления приводит к выработке управляющих сигналов У 1=1, У 2=0 и У 12=0, так что по следую щему СИ 1 счетчик 10 адреса прибавит единицу, а на мультиплексор 55 примется нулевой код. В обратном случае (МфВ) У 1=У 2=1, У 12=1, У 4=0, У 5=1, а на счетчик 10 адреса примется код с регистра 12, а на мультиплексор 55 - код М + 1, сформированный на выходе сумматора 61 5 5, По следующему СИ 2 происходит запись нового значения счетчика циклов в блок 15.Команда 5 выполняет считывание из ЗУПВ 21 и запись выбранного значения на буферный регистр 25, при этом модификация адреса, указанного в слове команды, не производится. Данная команда совместно с первой и второй командами обеспечивает вычисление произвольных булевских функций от некоторого набора переменных, которыми являются разряды вторых выходов регистра 25.Команда выполняется в следуоцем порядке. После приема команды по СИ 3 на регистр 12 блок управления форми рует сигналы У 1=1, У 2=0 и УЗ=О, чем разрешается переход к следующей по порядку команде и блокируется запись в блоке 11.Одновременно вырабатываются сигналы управления модификатором 3 - У 6=У 9=У 10, которые блокируют регистр 13 адреса и запись в блоки 14 и 15. По следующему СИ 3 конвейерный регистр 4 принимает содержимое регистра команд, а блок 2 управления формирует сигналы У 13=1, У 14=У 15=У 16=0, У 17=1. Прн этом разрешается прием на регистр 66 регистра 20 адреса, элемент ИЛИ 63 вырабатывает на выходе уровень логической единицы, по которому входной мультиплексор регистра 66 разрешает прохождение кода с выходов мультиплексора 64, который .в свою очередь обеспечивает прохождение кода с вторых выходов конвейерного регистра 4 (4-11 разряды регистры команд, Одновременно вырабатывак- тся .сигналы управления, если значение знакового разряда регистра команд равно О, то У 23=0, У 24=1, если наобо" рот, то У 23=1, У 24=0, У 25=У 26=0, У 27=1, У 28=У 29=0, У 22=0.1Таким образом, по следующему СИ 1 на регйстр 20 адреса принимается адрес с вторых выходов регистра 4, запись в блок 21 блокируется. Мультиплексор 23 обеспечивает прохождение кода с выхода блока 21 на вход данныхрегистра 25. Дешифратор 24 по коду21 113358 на третьих выходах регистра 4 раз-. решает запись в соответствующий триггер регистра 25, и по следующему СИ 3 значение на выходе 21 с требуемым знаком записывается в выбранный разряд, регистра 25.Команда Ь предназначена для оста- нова генератора. В сочетании с командами Зи 4 она может служить для останова генератора по достижению заданного числа тактов работы.При появлении этой команды на регистре команд блок 2 управления вырабатывает управляющие сигналы, блокирующие последовательно по времени счетчика 10 адреса и регистр 13 адреса. Далее вырабатывается блокировка ааппси в блоки памяти, блокировка второго регистра адреса, второго буферного регистра и выходного регистра. На этом генератор останавливает свою работу.Таким образом, предлагаемый генератор обеспечивает формирование весьма широкого набора многоразрядных 9 22последовательностей, которые могутбыть использованы в качестве входных наборов при функциональном контроле практически любых логическихузлов, выполненных как на ИС, так иБИС с числом выводов порядка 100.При этом длительность такта в среднемсоставляет величину порядка 10 мкс,что позволяет подавать за время провер:и несколько миллионов входных наборов, чем обеспечивается высокоекачество контроля, полнота и достоверность. Довольно ограниченный наборкоманд не требует сложного математического обеспечения и вместе с темдает возможность автоматизироватьнабор условий проверки, что значительно увеличивает производительностьтруда оператора. Генератор не требуетбольшого оборудования. При использовании микросхем средней .степени интеграциисерии ИС 100 генератор можетбыть выполнен на 7-8 ТЭЗ, содержащих100 ИИС с учетом резисторныхсборок.мирователя адреса модификатора адреса, первый выход формирователя адресаподключен к второму информационномувходу регистра данных модификатораадреса, второй выход формирователяадреса модификатора адреса подключен,к второму адресному входу регистраадреса накопителя имитируемых регист.ров и промежуточных результатов, третий адресный вход регистра адреса Онакопителя имитируемых регистров ипромежуточных результатов объединенс первым входом дешифратора блокаимитируемых регистров, выход регистраадреса накопителя имитируемых регистров и промежуточных результатов подключен к адресному входу блока памяти накопителя имитируемых регистрови промежуточных результатов, выходрегистра данных которого подключен к роинформационному входу блока памятинакопителя, второй информационныйвход регистра данных которого подключен к выходу сумматора по модулюдва блока имитируемых регистров, груп-.5па входов сумматора по модулю двакоторого подключена к первой группевыходов буферного регистра блока имитируемых регистров, управляющий входбуферного регистра которого соединен с выходом дешифратора блока имитируемых регистров, вход генераторатактовых импульсов является синхронизирующим входом многоразрядногогенератора испытательных последовательностей, о т л и ч а ю щ и й с ятем, что, с целью повышения егобыстродействия, введены блок управления, мультиплексор, схемы сравнения,конвейерный регистр и выходной ре- .;.гистр, причем блок управления содержит два элемента ИЛИ, дешифратор команд, три элемента И, 5 -триггер,1два регистра и мультиплексор, причемгруппа входов первого элемента ИЛИобъединена с первой группой входовмультиплексора блока управления и является группой входов внешних данныхрежима работы многоразрядного генератора испытательных последовательностей, входы сброса первого и второго регистров объединены с первым входом первого элемента И блока управления и являются входом "Пуск" много.разрядного генератора испытательных 55последовательностей, синхронизирующиевходы первого и второго регистров блока управления и конвейерного регистра объединены и подключены к выходу ге- нератора тактовых импульсов, первый выход первого элемента ИЛИ подключен к К -входу Й 5-триггера блока управления, второй выход первого элемента ИЛИ которого соединен,с вторым входом первого элемента И блока управления, выход первого элемента И которого подключен к Б -входу 15 -триггера блока управления, выход 15-триггера которого подключен к входу Пуск триггера" мультиплексора блока управления, первые входы второго и третьего элементов И которого объединены с группой входов дешифратора команд блока управления, второй вход второго элемента И и третьего элемента И которого подключены к соответствующим выходам второго элемента ИЛИ блока управления, первый вход второго регистра блока управления объединен с группой входов дешифратора команд и второго элемента ИЛИ блока управления и является первым управляющим входом блока управления, подключенного к выходу блока памяти про-. грамм и к информационному входу конвейерного регистра, выходы дешифратора команд, входы-выходы первого и второго регистров и выходь,второго и третьего элементов И блока управления подключены к соответствующим входам мультиплексора блока управления, кроме входа И=В, который является вторым управляющим входом блока управления и подключен к выходу схемы сравнения модификатора адреса, первый и второй входы схемы сравнения модификатора адреса подключены соответственно к второму и третьему входам буферного регистра модификатора адреса и входу П 5 4 мультиплексора, который является третьим управляющим входом блока управления, подключенным к выходу относительного адреса формирователя адреса мо, дификатора адреса, тактовый входформирователя адреса которого соединен с первым выходом конвейерного регистра, второй и третий выходы которого подключены соответственно к первому входу дешифратора и первомувходу схемы сравнения блока имйтируемых р гистров, второй вход схемы сравнения которого подключен к первому выходу буферного регистра блока имитируемых регистров, третий и четвертый выходы буферного регистра ко1133589 аж 98 Филиал ППП ОРгОФ ОРИ 7 Р У 77 РО-:ЛУ 4 РФ+771133589 торого подключены соответственно кпервому и второму входам выходногорегистра, информационный вход буферного регистра блока имитируемых регистров подключен к выходу мультиплексора накопителя имитируемых регистров и промежуточных результатов,первая группа входов мультиплексоракоторого подключена к выходу блокапамяти накопителя имитируемых регистров и промежуточных результатов, вторая группа входов мультиплексора которого подключена к третьему и четвертому входам регистра данных накопителя имитируемых регистров и промежуточных результатов и к выходу схемы сравнения блока имитируемых регистров и третему входу выходного регист 1Изобретение относится к вычислительной технике и может быть использовано в качестве датчика входных наборов в устройствах автоматизированного контроля сложных цифровых узлов.Известен программируемый генератор псевдослучайных последовательностей, содержащий имитатор регистра сдвига-накопитель,блокпамяти программ и блок модификации адреса - сумматор, обеспечивающий имитацию сдвига при очередном обращении к запоминающему устройству с произвольной выборкой 1,Недостатком этого устройства являются ниэкие функциональные возможности, обусловленные тем, что за время выполнения программы ЗУПВ может . имитировать один регистр сдвига с заданными обратными связями. Наиболее близким к предлагаемому устройству являетсямногофункциональный генератор двоичных последовательностей, содержащий генератор тактовых импульсов и последовательно соединенные блок памяти программ, модификатор адреса, блок памяти для хранения значений разрядов имитируемых .регистров сдвига, и выходной регистр с сумматором обратной связи, выход которого через мультиплексор ра, синхронизирующий вход которогоподключен к первому выходу генераторатактовых импульсов, выход выходногорегистра является выходом многоразрядного генератора испытательных последовательностей, третья группа выходов мультиплексора блока управления является третьим управляющим выходом блока управления и подключенак управляющему входу блока памятипрограмм, четвертая группа выходовмультиплексора блока управления является четвертым управляющим выходомблока управления и подключена к группе управляющих входов регистра дан-.,ных, регистра адреса и к управляющимвходам первого и второго блоков памяти модификатора адреса. 2подключен к входу данных блока памяти 2,Недостатками известного устройстваявляются низкое быстродействие, не обходимость большого числа командпри организации регистров, работающихс разными частотами сдвигов, а такженевозможность формирования произвольных булевских функций от заданныхразрядов регистра.Целью изобретения является повышение быстродействия устройства. Указанная цель достигается тем, 15 что в многоразрядный генератор испытательных последовательностей, содержащий блок памяти программ, модификатор адреса, накопитель имитируемых регистров и промежуточных ре=.20 зультатов, блок имитируемых регистров.и генератор тактовых импульсов, приэтом модификатор адреса содержит регистр адреса, регистр данных, дваблока памяти, буферный регистр иформирователь адреса, блок имитируемых регистров содержит дешифратор,буферный регистр и сумматор по модулю два, накопитель имитируемых регистров и промежуточных результатов 30 содержит регистр адреса, регистрданных и блок памяти, при этом ад. ресный вход блока памяти программ объединен с первым адресным входом регистра3 11331адреса модификатора адреса, с первымадресным входом регистра адреса накопителя имитируемых регистров ипромежуточных результатов и является входом внешнего адреса многоразрядного генератора испытательныхпоследовательностей, информационныйвйход блока памяти программ подключенк второму адресному входу регистраадреса модификатора адреса, стробирующие входы записи блока памяти накопителя имитируемых регистров ипромежуточных результатов и блоковпамяти модификатора адреса объедииены с первым стробирующим входом блока памяти программ и подключены к первому выходу генератора тактовых импульсов, входы синхронизации регистров адреса и регистров данных модификатора адреса, накопителя имитируемых регистров и промежуточных результатов объединены с вторым синхронизирующим входом блока памяти программ и подключены к второму выходу генератора тактовых импульсов, входы синхронизации буферных регистров модификатора адреса и блока имитируемых регистров объединены с третьим синхронизирующим входом блока памяти программ и подключены кФ 30 третьему выходу генератора тактовых импульсов, выход регистра адреса модификатора адреса подключен к адресным входам первого и второго блоков памяти модификатора адреса, информационный вход первого блока памяти мо З 5 дификатора адреса объединен с информа ционным входом блока памяти программ и первым информационным входом регистра данных модификатора адреса и регистра данных накопителя имити руемых регистров и промежуточных результатов и является входом внешних данных многоразрядного генератораиспытательных последовательностей, выходы первого и второго блоков памяти подключены к соответствующим ин- . формационным входам буферного регистра модификатора адреса, первый, второй и третий выходы буферного регистра модификатора адреса подключены к 50 входай данных адреса, начального адреса, адреса входного смещения формирователя адреса модификатора адреса, первый выход формирователя адреса подключен к второму информаци 55 онному входу регистра данных модификатора адреса, второй выход формирователя адреса модификатора адреса подключен к второму адресному входу регистра адреса накопителя имитируемых регистров и промежуточных результатов, .третий адресный вход регистра адреса накопителя имитируемых регистров и промежуточных результатов объединен с первым входом дешифратора блока имитируемых регистров, выход регистра адреса накопителя имитируемых регистров и промежуточных результатов подключен к адресному входу блока памяти накопителя имитируемых регистров и промежуточных результатов, выход регистра данных которого подключен к информационному входу блока памяти накопителя, второй информационный вход регистра данныхкоторого подключен к выходу сумматора по модулю два блока имитируемых регистров, группа входов сумматора по модулю два которого подключена к первой группе выходов буферного регистра блока имитируемых регистров, управляющий вход буферного регистра которого соединен с выходом дешифратора блока имитируемых регистров, вход генератора тактовых импульсов является синхронизирующим входом многоразрядного генератора испытательных последовательностей, введены блок управления, мультиплексор, .схемы сравнения, конвейерный регистр и выходной регистр, причем блок управления содержит два элемента ИЛИ, дешифратор команд, три элемента. И, 85 - триггер, два регистра и мультиплексор, причем группа входов первого элемента ИЛИ объединена с первой группой входов мультиплексора блока управления и является входами внешних данныхрежима работы многоразрядного генератора испытательных последовательностей, входы сброса первого и второго регистров объединены с первым входом первого элемента И. блока управления и являются входом "Пуск"многоразрядного генератора испытательных последовательностей синхроь ниэирующие входы первого и второгорегистров блока управления и конвейерного регистра объединены и подключены к третьему выходу генератора тактовых импульсов, первый выход первого элемента ИЛИ. подключен к Й -вхо Юду Ю -триггера блока управления,второй выход первого элемента ИЛИкоторого соединен с вторым входомпервого элемента И блока управления,5113358 выход первого элемента И которого подключен к б -входу Ю -триггера блоКа управления, выход 85-триггера которого подключен к входу "Пуск триггера" мультиплексора блока управления, первые входы второго и третьего элементов И которого объединены с группой входов дешифратора команд блока управления, вторые входы второго элемента И и третьего элемента И 10 которого подключены к соответствующим выходам второго элемента ИЛИ блока управления, первый вход второго регистра блока управления объединен с группой входов дешифратора ко манд и второго элемента ИЛИ блока управления и является первым управляющим входом блока управления, подключенного к выходу блока памяти программ и к информационному входу 20 конвейерного регистра, выходы дешифратора команд, входы-выходы .первого и второго регистров и выходы второго и третьего элементов И блока управления подключены к соответствующим 25 входам мультиплексора блока управления, кроме входа М=В, который является вторым управляющим входом блока управления и подключен к выходу схемы сравнения модификатора адреса, З 0 первый и второи входы схемы сравнения модификатора адреса подключены соответственно к второму и третьему выходам буферного регистра модификатора адреса и входу П 54 мультиплексора, который является третьим управляющим входом блока управления, подключенным к выходу относительного адреса формирователя адреса модификатора адреса, тактовый вход формирователя адреса которого соединен с первым выходом конвейерного регистра, второй и третий выходы которого под-. ключены соответственно к первому входу дешифратора и первому входу схемы сравнения блока имитируемых регистров, второй вход схемы сравнения которого подключен к первому выходу буферного регистра блока имитируемых регистров, третий и четвертый выхо ды буферного регистра которого подключены соответственно к первому и второму входам выходного регистра, информационный вход буферного регистра блока имитируемых регистров - к 55 выходу мультиплексора накопителя имитируемых регистров и промежуточных результатов, первая группа входов мультиплексора которого подключенак выходу блока памяти накопителя имитируемых регистров и промежуточныхрезультатов, вторая группа входовмультиплексора которого подключенак третьему и четвертому входам регист"ра данных накопителя имитируемых регистров и промежуточных результатови к выходу схемы сравнения блока имитируемых регистров, управляющие входы мультиплексора, блока памяти, регистра адреса и регистра данных которого подключены.к первой группеуправляющих выходов мультиплексораблока управления, вторая группа выходов мультиплексора блока управле- .ния является вторым управляющим выходом блока управления и подключенак стробирующему входу дешифратора,единичному входу буферного регистраблока имитируемых регистров и третьему входу выходного регистра, синхронизирующий вход которого подключенк первому выходу генератора тактовыхимпульсов, выход выходного регистраявляется выходом многоразрядногогенератора испытательных последовательностей третья группа выходовмультиплексора блока управления является третьим управляющим выходомблока управления и подключена к управляющему входу блока памяти программ, четвертая группа выходовмультиплексора блока управления является четвертым управляющим выходомуправления и подключена к группеуправляющих входов регистра данных,регистра адреса и к управляющим входам первого и второго блоков памятимодификатора адреса,На фиг. 1 представлена структурная схема генератора; на фиг, 2 структурная схема блока управления; на фиг. 3 - функциональная схема формирователя управляющих сигналов блока управления; на фиг. 4 - функциональная схема входного мультиплексора н счетчика адреса блока памяти программы; на фиг. 5 - функциональная схема регистров адреса и данных блоков памяти модификатора адреса; на фиг. 6- функциональная схема формирователя адреса; на фиг. 7 - функциональная схема накопителя имитируемых регистров. с регистрами адреса и данных и выходным мультиплексором.Многоразрядный генератор состоит11335 блока 2 управления, модификатора 3 адреса, конвейерного регистра 4, накопителя 5 имитируемых регистров и промежуточных результатовблока 6 имитируемых регистров, выходного регистра 7 и генератора 8 тактовых импульсов.Блок 1 памяти программ содержит входной мультиплексор 9 адреса (из двух направлений в одно), счетчик 10 Оадреса, блок 11 памяти команд (ЗУПВ)и выходной регистр 12 команд.Модификатор 3 адреса состоит из регистра 13 адреса и первого и второго блоков 4 и 15 памяти (ЗУПВ) и 5 регистра 16 данных, буферного регистра 17, формирователя 18 адреса исхемы 19 сравнения.Накопитель 5 имитируемых регистров содержйт регистр 20 адреса, блок 20 21 памяти (ЗУПВ) регистр 22 данных с входными мультиплексорами, и мультиплексор 23.Блок 6 имитируемых регистров срдержит дешифратор 24 на 11 выходов.з" 25 со стробированием, буферный регистр 25 состоящий из МПН -триггеров, управляющие входы которых Н соединены с соответствующими выходами денифратора, а информационные входы 3 ЗО объединены и подключены к выходу ;мультиплексора 23, схемы 26 сравнения двух 8-разрядных кодов и четырехвходового сумматора 27 по модулю два.35Блок управления (фиг. 2) содержит элемент ИЛИ 28, элемент И 29, 82 - триггер 30, дешифратор 31 команд, элемент ИЛИ 32, являющийся дешифратором номера разряда регистра 25, соО единенного с четвертым входом 3 сумматора 27 по модулю два, второй и третий двухвходовые элементы И 33 и 34, регистры 35 и 36, вход 37 и мультиплексор 38, который содержит45 (фиг. 3) инверторы 39, элементы ИИЛИ 40 и 41, элемент И 42 и элементы И-ИЛИ 43-46, элемент И 47 и элементы И-ИЛИ 48 и 49 двухвходовые.На фиг. 4 показан входной мультиплексор 50 и счетчик 51 адреса. Регистры адреса 13 и данных 16 содержат (фиг, 5) двухвходовой элемент И 52 и регистры с входным мультиплексором 53, элемент И 54, мультиплек= сор 55.Формирователь адреса состоит (фиг. 6) из первого комбинационного 89 8сумматора 56 на три входа, второго,1 третьего и четвертого двухвходовых сумматоров 57 и 58, мультиплексора 59, четвертого и пятого комбинационных сумматоров 60 и 61, осуществляющих сложение входного кода с единицей.Регистры адреса и данных (фиг, 7) состоят из входного мультиплексора 62 иэ двух направлений в одно, элемента ИЛИ 63, мультиплексора 64, элемента И.65, регистра 66 адреса с входным мультиплексором, входного мультиплексора 67 данных из четы-рех направлений в одно и триггера 68 хранения данных.Предлагаемое устройство работает следующим образом.Генератор имеет два режима работы - ввод внешних данных и формирование на выходном регистре последовательности многоразрядных кодов.При вводе информации в ЗУПВ 11 по шине "Ввод 1" в блок 2 управления подается сигнал, по которому блок управления формирует на первых выходах управляющие сигналы У 5=0, У 4=1, открывающие прохождение кода адреса на шине внешнего адреса АВ через мультиплексор 9 на входы параллельного приема счетчика 10, Одновременно по сигналам У 1=У 2=1 счетчик 10 переводится в режим параллельного приема и формирует адрес ЗУПВ 11, на .вход данных которого поступает кодс шины внешних данных 28, а на вход управления - сигнал разрешения записи УЗ=1 из блока 2. Генератор 8 тактовых импульсов выдает трехфазную систему синхроимпульсов СИ 1, СИ 2 и СИЗсинхронно с внешними стробимпульсами, идущими по шине СВ. Код на шинах "Ввод 1 - Ввод 3" АВ, ДВ, СВ,поступает с внешнего устройства илипульта управления (не показаны),При записи в ЗУПВ 11 регистры 13,16., 20, 22, 25 и 7 блокируются, а науправляющих входах ЗУПВ 14, 15 и 21отсутствуют сигналы разренения записи. По окончании записи в ЗУПВ 11 сигнал "Ввод 1" снимается, подается сигнал "Ввод 2" и происходит заполнение ЗУПВ 14 и 15, При этом блокируется запись в ЗУПВ 11 и 21; а также регистры 20, 22, 25 и 7 и счетчик команд. Аналогичным образом заполняется ЗУПВ 21 при поступлении сигнала"Ввод 3". В процессе записи наличиесигнала на любой из шин "Ввод 1Ввод 3" устанавливает 85 -триггер 30блока управления в "0",.выход которого поступает на вход мультиплексора 38, который вырабатывает сигналы управления внешней записи,По окончании записи сигналы на шинах "Ввод 1 - Ввод 3" устанавливаетсяв "0", и при появлении одиночного 1 Оимпульса "Пуск" триггер 30 устанавливается в "1". Прн этом на выходахмультиплексора 38 появляются сигналыУ 1=У 2=1, У 4=У 5=0, по которым счетчиккоманд принимает нулевой код с выхода мультиплексора, чем осуществляется начальная установка счетчика. Одновременно на выходе мультиплексора38 появляется сигнал У 28=1, который,поступая на установочный 5 -вход ре-2 Огистра, устанавливает его триггерыв 11 1 фИз ЗУПВ 1 1 по адресу " 0" выбирает"ся команда, которая поступает на р егистр 1 2 команд . Разряды 0-3 , 1 2-20 25РК 1 2 поступают для анализа в блокуправления , при этом разряды 0-3 РК1 2 поступают на дешифратор 3 1 команд ,а 1 3-20 РК 1 2 - на элемент ИЛИ 3 2,сигнал на инверсном выходе которого35 М= 1 тогда , кЬгда код на разрядах1 3-20 РК 1 2 равен нулю, т . е . соответствует номеру младшего разряда регистра 25 , соединенного с входом Р сумматора 2 7 . В тех случаях , когда код35команды соответствует 0-2 либо 5 командам, либо идет двухадресная команда записи разряда имитируемого регистра, хранящегося в ЗУПВ 21, в регистр 25 без обращения кЗ -входусумматора 27, на выходах мультиплексора 38 вырабатываются сигналы У 1=1,.У 2=0, которые, поступая на управляющие входы счетчика команд, переводятего в режим счета, и по следующему,синхроимпульсу СИ 1 счетчик командприбавит единицу, формируя следующийадрес для ЗУПВ 11 команд.В том случае, когда на регистр 12выбирается двухадресная команда запи си разряда имитируемого регистра изЗУПВ 21 в регистр 25 с обращением ковходу 3 сумматора 27, либо 4-я команда условного перехода, на вь 1 ходахУ 1, У 2 мультиплексора 38 вырабатываются единичные сигналы, по которымсчетчик 10 переводится в режим параллельного приема. Одновременно на вы 89 10ходе У 5 мультиплексора 38 вырабатывается единичный сигнал, разрешающийпрохождение через входной мультиплексор 50 кода с 13-20 разрядов регистра 12, и по следующему синхроимпульсу СИ 1 счетчик 10 устанавливается всостояние, соответствующее коду, записанному в указанных разрядах словакоманды,При поступлении на дешифратор .команд кода 6-й команды мультиплексор38 вырабатывает на выходах У 1, У 2 нулевые сигналы, блокирующие счетчиккоманд, чем осуществляется остановгенератора,Таким образом, при работе генератора выполняются следующие операции.Двухадресная команда выдачи А разряда 11 имитируемого регистра, хранящегося в ЗУПВ 21, на буферный регистр25 по адресу АБР без обращения к входу 2 сумматора 27. Данная командаимеет признак "О" в нулевом разрядеслова команды и выполняется в следующей последовательности.По синхроимпульсу СИ 1 на счетчике; 10 формируется адрес ЗУПВ 11 и выбираемая команда поступает на регистркоманд РК 12, который принимает слово команды по синхроимпульсу СИ 3.Блок управления 2 анализирует состояние регистра 12, Поскольку нулевойразряд регистра 12 содержит "0", ина выходе элемента ИЛИ 32 сигнал от-сутствует, то мультиплексор 38 вырабатывает иа первой группе выходовследующие сигналы: У 1=1, У 2-У 4=0,У 5=1. Сигналы У 1, У 2 разрешают прибавление единицы в счетчике 10, сигнал УЗ.блокирует запись команд в память ЗУПВ 11. Комбинация сигналовУ 4=0, У 5=1 в данном случае несущественна, так как запись в ЗУПВ Ы неразрешена. Одновременно на второйгруппе выходов мультиплексора 38вырабатываются управляющие сигналыдля модификатора 3 Уб-У 12. СигналыУ 6, У 7=1 снимают блокировку регистра 13 адреса блоков памяти ЗУПВ 14и,15 и регистра 16 данных блока памяти ЗУНВ 15, По сигналу У 8=0 входныемультиплексоры подключают входы регистра 53 к выходам 4-11 разрядоврегистра 12, а входы регистра 55 квторым выходам формирователя 18 адреса. При этом сигнал УП=О устанавливает в "0" старшие разряды регистраадреса, соединенные соответственно с1133589 2если А+Мс, либо 5 З=А+В+М-, еслиА+М., что позволяет провести модификацию адреса за время, равное прохожцению сигналов через два сумматора и мультиплексор,.Одновременно с выработкой кода исполнительного адреса на выходах сумматора 60 5 3 блок 2 управления формирует на третьих выходах мульти- иО плексора 38 управляющие сигналы У 13==У 22=1, по которым разрешается приемкодов на регистр 66 регистра 20 адреса и триггер 68 регистра 22 данных.При этом управляющие сигналы У 14=15 У 16=У 17=0 и У 15=1, которые поступают на управляющие входы мультиплексора 62,разрешают прохождение кода исполнительного адреса с выхода сумма,х тора 60 на вход регистра со входныммультиплексором 66. Поскольку У 16==У 17=0, то на выходе схемы ИЛИ 63вырабатывается управляющий сигнал,который, поступая на управляющий,вход регистра 83, разрешает выборку25 с выходов мультиплексора 62. 4-7 разрядами регистра 12, а сигналУ 12=0 устанавливает в "0" регистрданньх. Кроме того, сигналы У 9=У 10=0запрещают запись в блоки памяти.В устройстве максимальное числоразличных регистров, имитируемых вЗУПВ 21, принято равным 16, поэтомуномера этих регистров имеют в блокахпамяти последовательную адресацию с0 по 15, Это приводит к необходимостустанавливать старшие разряды адресав регистре 13 адреса в "О" при выполненни данной команды.Таким образом, при выполнениикоманды на регистре 13 адреса последующему синхроимпульсу СИ 1 устанавливается код номера имитируемогорегистра, записанньй в 8-11 разрядах регистра 12, по которому с первьвыходов блока 14 памяти выдаетсякод числа разрядов имитируемого регистра , с вторых .выходов блока 14выдается код начального адреса, скоторого размещается имитируемьй регистр в блоке 21, а с выхода блока15 выдается текущее значение модифи-.катора адреса данного имитируемогорегистра, Указанные коды поступаютсоответственно на первые, вторые итретьи входы буферного регистра 17 30и по заднему фронту синхроимпульсаСИ 3 принимаются на него. Одновременно на конвейерный регистр 4 принимается код относительно адреса А Гразряда имитируемого регистра и код З 5номера разряда регистра 25, кудаследует записать значение выбираемого разряда имитируемого регистра.Коды относительного адреса А,длины , начального адреса В и модиФикатора М поступают соответственно на первые, вторые, третьи и четвертые входы формирователя 18 адреса. Сумматор 56 5 1 формирователя навыходе 5 вырабатывает сумму 5 =А ++ М в , и сигнал переноса на выходеС, если А+М в ,О. Сумматор 57 б 2вырабатывает сумму б =А + М -,. Поуправляющему сигналу переноса, соединенному с управляющим входом Ч 3, мультиплексор 59 разрешает прохождениекода с выхода сумматора 56 либо с выхода сумматора 57 на второй входсумматора 60 5 3, первые входы которого соединены с вторыми выходами В 55,регистра 17.Таким образом, на выходе суммато-.ра 60 реализуется функция 53=А+В+М,По переднему фронту следующего синхроимпульса.СИ.1 регистр 66 принимает код испалнительного адреса, и на выходе ЗУПВ 21 появляется значение выбранного разряда имитируемого регистра, При этом с выхода формирователя 38 блока 2 управления поступают сигналы У 25=У 26=0,а также сигналы У 23=1,и У 24=0 если значение разряда знака в 1 слове команды было ноль, или У 24=1 и У 23=0 в обратном случае. Таким образом, на выходе мультиплексора 23 формируется значение выбранного разряда имитируемого регистра ДРВ, которое поступает на 1) -входы триггеров регистра 25. Принятьй по прошедшему синхроимпульсу СИ 3 на конвейерный регистр 4 код АБР номера разряда регистра 25 поступает с.третьего выхода регистра 4 на вход дешифратора 24, выходы которого соединены с управляющими входами триггеров соответствующих разрядов регистра 25. При этом с четвертых выходов мультиплексора 38 блока 2 управления поступают управляющие сигналы У 27=1, У 28=У 29=0. Управляющий сигнал У 27 подается на стробирующий вход С дешифратора 24, и на выходе дешифратора , соответствующем коду АБР, появляется сигнал, разрешающий запись данных на выходе мультиплексора 23 в соответствующий триггер14 ют соответственно на входы Х 14 иХ 15 мультиплексора 38. Поскольку режим ввода внешних данных закончен,и сигнал "Пуск" уже прошел, то навходах ХЗ, Х 4 и Х 31 мультиплексора38 присутствует логический "0". Сигналы на входах Х 9 и Х 10 равны нулю,.так как сигнал на стробирующем входедешифратора 31 также. равен нулю. Та-.ким образом, на выходах схем И-ИЛИ 40и 41 вырабатываются сигналы У 1 У 2 О,являющиеся выходными сигналами мультиплексора 38, которые блокируютсчетчик 10 адреса.Аналогично на первом регистре адреса но СИ 1 формируется адрес бло-.ков 14 и 15 памяти.По следующемуСИ 3 на выходе регистра 36 появляется задержанный сигнал 25 МЗ, по которому выход мультиплексора У 1 устанавливается в единицу, разрешая выдачуследующей команды счетчиком команд,а на выходе У 6 вырабатывается нулевой сигнал блокировки первого регистра адресаПо сигналу У 8=0 мультиплексор 55 принимает код с сумматора 61, на разрядах которого ОР 55 -7 Р 55 сформирован код М+1, Одновременно сумматор 54 58 вырабатывает сигнал переноса П 4, если М+1-1,=0, покоторому на выходе мультиплексора 38появляется сигнал У 12=0, что приводит к установке мультиплексора 55в ноль. В отсутствие П 54 У 12=1, чтоприводит к приему на мультиплексор55 кода в 0-7 разрядах 55,Тем самым реализуется в алгоритм счета модиФикатора М по модулю 1 .,На сумматоре 60 формируется адресблока 21, который поступает нарегистр 13 адреса. В то же времяна выходе У 10 мультиплексора.ЗУ вы-.рабатывается сигнал, по которому разрешается запись в блок 15 по следующему синхроимпульсу СИ 2. Далее последующему СИ 3 блок управления формирует У 13=0, по которому блокируетсярегистр 20 адреса. В этот момент со-. адресу записывается в мпадший разрядвторого буферного регистра, соединенный с входом 2 сумматора, и на еговыходе вырабатывается сигнал обратной связи один такт 5 МОС, после чегосигналом У 27=0 второй буферный 13 1133589буферного регистра 25, которая происходит по заднему фронту следующегосинхроимпульса СИ 3. Поскольку управляющий сигнал У 29=0, то выходнойрегистр 7 при этом заблокирован.Аналогичным образом заполняются теразряды регистра 25, которые используются для формирования входного набора при испытании .данного логического узла. При этом для заполнения К 10разрядов требуется К команд в блокеЗУПВ 11, При выполнении узлов предлагаемого генератора на элементной базе ИС 100 можно выбрать длительностьСИ 1, СИ З,равную 8 нс, расстояние 15между ними ЗО нс, что обеспечиваетдлительность такта выполнения команды 60 нс. При проверке многовыводныхлогических узлов, имеющих число входов порядка 100,время заполнения реги-, 20стра 25 будет порядка 6 мкс,что вполнеприемлемо в устройствах функциональ-;,ного контроля.При выполнении сдвига в имитиру- .емом регистре с подачей на его вход 25заданной функции обратной связи происходит заполнение младших разрядоврегистра 25, соединенных с входамиА,В,С,Э сумматора 27 по модулю два.При обращении к входу сумматора на 3 Овходы элемента ИПИ 32 блока 2 управления поступает код, соответствую-щйй всем нулям в 13-20 разрядах регистра 12, и на инверсном выходеэлемента ИЛИ 32 возникает сигнал.Поскольку при прохождении этой команды в нулевом разряде регистра 12записан ноль, то на выходе элементаИ 33 появляется сигнал, являющийся.признаком обращения к 2 -входу сумматора 27, который служит сигналом дляувеличения М на единицу и для записи нового значения М во второй блок15 памяти, а значение с выхода сумматора 27 поступает в блок ЗУПВ 21по тем адресам, которые устанавливаются при прохождении команды. Поэтому сигнал с выхода элемента И 33задерживается на триггерах регистров36 и 37 (фиг. 2).держимое блока 21 по установленномуТак как при этом необходима задержка в один такт для выполнениязаписи в блоки 15 и 21 памяти,тоусловием блокировки счетчика командбудет наличие сигнала на выходе 55элемента И 33 и отсутствие задержанного сигнала 25 МЗ на триггере регист- . регистр блокируется на один такт, Кра 36. Отмеченные сигналы поступа- ,приходу следующего синхроимпульса

СмотретьЗаявка

3568241, 25.03.1983

ПРЕДПРИЯТИЕ ПЯ А-3162

ТЮПИН ВАЛЕРИЙ ПЕТРОВИЧ, ГРОМАКОВСКИЙ ВИТАЛИЙ АЛЕКСАНДРОВИЧ, ЛЕВИНА ЕЛЕНА ЛЕОНТЬЕВНА

МПК / Метки

МПК: G06F 1/04

Метки: генератор, испытательных, многоразрядный, последовательностей

Опубликовано: 07.01.1985

Код ссылки

<a href="https://patents.su/20-1133589-mnogorazryadnyjj-generator-ispytatelnykh-posledovatelnostejj.html" target="_blank" rel="follow" title="База патентов СССР">Многоразрядный генератор испытательных последовательностей</a>

Предыдущий патент: Двухполярный стабилизатор постоянного напряжения

Следующий патент: Устройство для сопряжения датчика информации с электронной вычислительной машиной

Случайный патент: Система для измерения распределения давления на поверхности модели летательногоаппарата