Устройство для декодирования с исправлением ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1797165

Автор: Карпухин

Текст

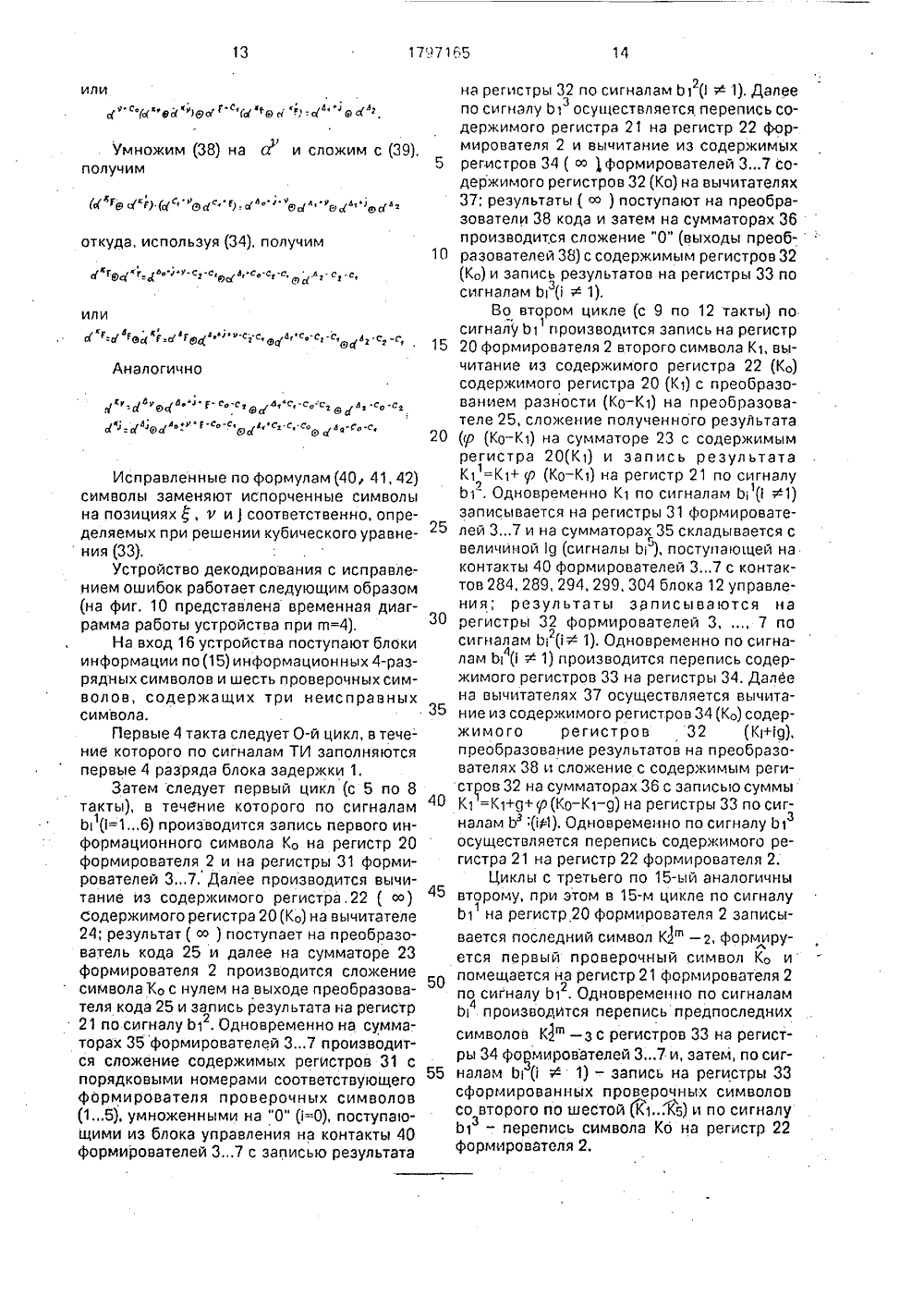

(51) 5 ГОСУДАРСТВЕННОЕ ПАТЕ ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИ ость трех ок 1 роч- оши- ения бьединени кл,006 Г ю СССР1986.ДИ РОВА к вычислитель- пользование в и исправления по.ли АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(54) УСТРОЙСТВО ДЛЯ ДЕКС ИСПРАВЛЕНИЕМ ОШИБ(57) Изобретение относитсяной технике и связи. Его иустройствах обнаружения ошибок позволяет повысить достоверн декодирования за счет исправления до пачек ошибок. Устройство содержит бл задержки, формирователи" 2.5 прове ных символов, блок 10 определения бочных позиций, блок 11 исправл ошибок, блок 12 управления, элемент и элемент ИЛИ 15. Благодаря введе формирователей 6, 7 проверочных си лов, арифметического блока 8, блока 9 числения коэффициентов и элемента И устройстве обеспечивается решение и зательного уравнения третьей степени ле ОР (2 ), что и позволяет достичь ц изобретения. 7 з, и. ф-лы, 9 ил.первого вычитателя подключены к входам вычитаемого шестого, седьмого, восьмого и девятого вычитателей, выходы второго вы,читателя подключены к входам вычитаемого десятого, одиннадцатого вычитателей, к входам уменьшаемого шестого вычитателя и входам первого слагаемого первого, второго и третьего сумматоров и к входам первого умножителя на два, выходы третьего вычитателя подключены к входам уменьшаемого восьмого и одиннадцатого вычитателей, к входам вычитаемого тринадцатого и четырнадцатого вычитателей, к входам первого слагаемого четвертого, пятого, шестого и седьмого сумматоров. к входам второго слагаемого первого сумматора и к входам второго умножителя на два, выходы четвертого вычитателя подключены к входам уменьшаемого седьмого, десятого и тринадцатого вычитателей, к входам первого слагаемого восьмого и девятого сумматоров и к входам второго слагаемого четвертого сумматора, выходы пятого вычитателя подключены к входам уменьшаемого двенадцатого и четырнадцатого вычитателей, выходы десятого вычитателя подключены к входам уменьшаемого девятого вычитателя и к входам первого преобразователя кода, выходы шестого, седьмого, восьмого, одиннадцатого, двенадцатого, тринадцатого и четырнадцатого вычитателей подключены к входам второго, третьего, четвертого, пятого, шестого, седьмого и восьмого преобразователя кода, выходы второго преобразователя кода подключены к входам уменьшаемого пятнадцатого и шестнадцатого вычитателей и к входам вычитаемого семнадцатого и восемнадцатого вычитателей, выходы третьего преобразователя кода подключены к входам второго слагаемого пятого сумматора и первого слагаемого десятого сумматора, выходы четвертого преобразователя кода подключены к входам второго слагаемого второго сумматора и к входам вычитаемого девятнадцатого вычитателя, выходы первого преобразователя кода подключены к входам второго слагаемого третьего сумматора, к входам второго слагаемого седьмого сумматора и к входам вычитаемого двенадцатого вычитателя, выходы первого сумматора подключены к входам второго слагаемого десятого сумматора, выходы пя.того преобразователя кода подключены к входам первого слагаемого одиннадцатого сумматора, к входам вычитаемого двадцать первого, двадцать второго и двадцать третьего вычитателей и к входам уменьшаемого двадцать четвертого и двадцать пятого вычитателей, выходы четвертого сумматора соединены с входами первого слагаемого двенадцатого сумматора, выходы шестого преобразователя кода подключены к входам первого слагаемого тринадцатого сумматора и к входам вычитаемого двадцать шестого вычитателя, выходы седьмого преобразователя кода подключены к входам второго слагаемого двенадцатого и восьмого сумматоров, выходы восьмого преобразователя кода подключены к входам второго слагаемого девятого сумматора, выходы девятого вычитателя подключены к входам девятого преобразователя кода, выходы которого подключены к входам второго слагаемого шестого сумматора, выходы первого умножителя на два подключены к входам второго слагаемого одиннадцатого сумматора, выходы которого подключены к входам вычитаемого пятнадцатого вычитателя, выходы пятого сумматора подключены к входам уменьшаемого девятнадцатого вычитателя, выходы второго сумматора подключены к входам вычитаемого шестнадцатого вычитателя и к входам уменьшаемого семнадцатого вычитателя, выходы третьего сумматора подключены к входам уменьшаемого двадцать первого вычитателя, выходы шестого сумматора подключены к входам вычитаемого двадцать четвертого вычитателя, выходы десятого сумматора подключены к входам уменьшаемого восемнадцатого вычитателя, выходы двенадцатого сумматора подключены к входам уменьшаемого двадцать второго вычитателя, выходы седьмого сумматора подключены к входам уменьшаемого двадцать третьего вычитателя, выходы восьмого сумматора подключены к входам уменьшаемого двадцатого сумматора, выходы девятого сумматора подключены к входам уменьшаемого двадцать шестого вычитателя, выходы второго умножителя на два подключены к вторым входам тринадцатого сумматора, выходы которого подключены к входам вычитаемого двадцать пятого вычитателя, выходы восемнадцатого, двадцать первого, двадцатого, шестнадцатого, двадцать второго, семнадцатого, двадцать третьего, девятнадцатого, двадцать пятого, двадцать четвертого, двадцать шестого и пятнадцатого вычитателей являются соответственно - двенадцатыми выходами блока,5. Устройство и. 1, о т л и ч а ю щ е е ся тем, что блок вычисления коэффициентов выполнен на вычитателях, сумматорах, преобразователях кода и регистрах, входы уменьшаемого )-го вычитателя Д=1,6) являются соответственно (2)-1)-ми входами блока, входы вычитаемого 1-го вычитателя объединены с входами первого слагаемого1-го сумматора и являются (2)-ми входами блока, выходы /-го вычитателя через одноименный преобразователь кода соединены с входами второго слагаемого одноименного сумматора, выходы пероого, третьего и пятого сумматоров подключены к входам уменьшаемого седьмого, восьмого и девятого вычитэтелей соответственно, выходы второго, четвертого шестого сумматоров подключены к входам вычитаемого седьмого, восьмого, девятого вычитателей соответственно, выходы седьмого вычитателя соединены с входами уменьшаемого десятого вычитателя, выходы которого подключены к информационным входам первого регистра, выходы восьмого вычитателя соединены с входами вычитаемого десятого вычитателя и входами умен ьшаемого одиннадцатого вычитателя, выходы которого подключены к информационным входам второго регистра, выходы девятого вычитателя соединены с входами вычитаемого одиннадцатого вычитателя и информационными входами третьего регистра, управляющие входы всех регистров объединены и являются управляющим входом блока, выходы первого-третьего регистров являются одноименными выходами блока.б. Устройство по п. 1, о т л и ч а ю щ е ес я тем, что блок определения ошибочных позиций выполнен на вычитателях, сумматорах, преобразователях кода, элементе сравнения, счетчике, сдвиговых регистрах, вентильных элементах и элементе ИЛИ, входы вычитаемого первого вычитателя являются первой группой первых информационных входов блока, входы уменьшаемого первого и второго вычитателей объединены и являются второй группой первых информационных входов блока, входы вычитаемого второго вычигэтеля являют,ся третьей груп пой первых информационных входов блока, информационные входы первого-третьего сдвиговых регистров являются вторыми информационными входами блока, выходы первого вычитателя подключены к входам вычитаемого третьего вычитателя, входы уменьшаемого которого обнулены, к первым входам первого сумматора и к входам первого преобразователя кода, входы которого подключены к вторым входам первого сумматора, выходы которого подключены к входам аычитаемого четвертого вычитателя, входы уменьшаемого которого подключены к выходам второго вычитателя, а выходы через второй преобразователь кода подключены к первым входам второго сумматора, вторые входы которого через третий преобразователь кода подключены к выходам третьего вычитателя, выходы второго сумматора подключены к информационным входам первого-третьего вентильных элементов и к первым входам элемента сравнения, вторые входы которого являются первыми управляющими входами блока, выход элемента сравнения соединен счетным входом счетчика, первый-третий выходы которогоподключены к управляющим входам соответственно первого-третьего вентильных элементов и к входам разрешения считывания соответственно первого-третьего сдвиговых регистров, выходы которых подключены к входам элемента ИЛИ, выход которого является последовательным выходом блока, выходы первого вентильного элемента подключены к входам вычитаемого пятого и шестого вычитателей, входам первого слагаемого третьего и четвертого сумматоров и являются первой группой первых параллельных выходов блока, выходы второго вентильного элемента подключены к входам уменьшаемого пятого вычитателя, к входам вычитаемого седьмого вычитателя, входам первого слагаемого пятого сумматора и являются второй группой первых параллельных выходов блока, выходы третьего вычитателя элементов подключены к входам уменьшаемого шестого и седьмого вычитателей и являются третьей группой первых параллельных выходов блока, выходы пятого-седьмого вычитателей соответственно четвертый-шестой преобразователи кода соединены с входами второго слагаемого соответственно третьего-пятого сумматоров, выходы которых являются вторыми параллельными выходами блока, управляющих вход счетчика является вторым управляющим входом блока.7, Устройство по и, 1, о т л и ч а ю щ е ес я тем, что блок исправления ошибок выполнен на первом-третьем узлах, каждый из которых содержит первый-восьмой сумматоры, перцый-третий вычитатели и пероыйтретий преобразователи кода, выходы первого сумматора соединены с первыми входами шестого сумматора и входами вычитаемого первого вычитателя, выходы которого через первый преобразователь кода подключены к вторым входам шестого сумматора, выходы которого соединены с входами уменьшаемого второго вычитателя, выходы второго сумматора соединены с первыми входами четвертого сумматора, выходы которого подключены к первым входам седьмого сумматора и входам вычитаемого второго нычитателя, выходы которого через второй преобразователь кода подключены к вторым входам седьмого сумматора, выходы которого соединены с входами8 14 10 О 0 г о 1 о 7 4 8 5 4 1 3 11 114 1 г 1 г 13 14 9 13 1 О 7 14 212 вычитаемого третьего вычитателя, выходы которого через третий преобразователь кода подключены к первым входам восьмого сумматора, выходы третьего сумматора соединены с первыми входами пятого сумматора, выходы которого подключены к входам уменьшаемого третьего вычитателя, входы уменьшаемого первого вычитателя и первые входы первого и второго сумматоров во всех узлах являются первыми входами блока, вторые входы второго и четвертого и объединенные входы второго пятого и восьмого сумматоров во всех узлах являются вторыми входами блока, вторые входы пер-, вого и первые и вторые входы третьего сумматоров во всех узлах являются третьими входами блока, выходы восьмого сумматора во всех узлах являются выходами блока,8,Устройствопоп,1,отл ича ющеес я тем, что блок управления содержит счетчик, дешифратор, первый-седьмой элементы И, первый-двадцатый элементы ИЛИ, первый.-третий элементы сравнения, первые входы которых являются информационными входами блока, первый и второй входы первого элемента И являются тактовь 1 ми входом и входом Пуск" блока, выход первого элемента И подключен к первым входам второго-седьмого элементов И, входу счетчика и является первым выходом блока, выходы счетчика соединены с входами дешифратора, первый, второй и третий выходы которого подключены к первым входам соответственно первого-шестого, седьмого-двенадцатого и тринадцатого-восемнадцатого элементов ИЛИ, выходы первой-третьей. групп дешифратора соединены с вторыми входами соответственно первого-восемнадцатого элементов ИЛИ, выходы первого, седьмого и тринадцатого элементов ИЛИ являются первой группой выходов блока, выходы (бК+)-го элемента ИЛИ (К=О, 1, 2; 1=2,6) и (1-1)-е разряды выходов четвертой и пятой групп дешифратора являются 1-ми группами выходов блока, соединены с вторыми входами соответственно первого- третьего элементов сравнения, выходы "Равно" которых подключены к вторым входам соответственно второго-четвертого элементов И, выходы которых соединены с входами девятнадцатого элемента ИЛИ, выход которого является вторым выходом блока, выходы "Не равно" первого-третьего элементовсравнения подключены к вторым входам соответственно пятого-седьмого элементов И выходы которых соединены с входами двадцатого элемента ИЛИ, выход которого является третьим выходом блока; седьмой-девятый выходы дешифратора являются соответственно четвертым-шестым выходами блока.1797165 ЪеЬЪ 1 С% ЧЪ чм Корректор С, Патрушев едактор Заказ 656 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж, Раушская наб 4/5 оизводственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина с ч Ъ ставитель А. Кар хред М,МоргенталИзобретение относится к вычислительной технике и связи и может быть использовано в устройствах обнаружения иисправления до трех пачек ошибок, возникающих при хранении или передаче дискретной информации.Известно устройство для декодирования с коррекцией ошибок, содержащее блоки данных Д 1Дп, каждый из которыхимеет 8 бит (байт) плюс два контрольныхбайта.Недостатком этого устройства являетсябольшое оборудование и излишняя избыточность при обработке 2"-разрядных слов.Из известных устройств для декодирования с коррекцией ошибок наиболее близким по технической сущности являетсяустройство для декодирования с исправлением ошибок, которое содержит входнойсдвиговый регистр, четыре формирователяпроверочных символов, блок исправленияошибок, блок управления, два элемента И иэлемент ИЛИ,Недостатком этого устройства являетсяневозможность исправления трех пачекошибок, что приводит к снижению достоверности при передаче информации,Целью изобретения является повышение достоверности декодирования за счетисправления до трех пачек ошибок.На фиг. 1 представлена структурнаясхема устройства для декодирования с исправлением ошибок; на фиг, 2, 3 - функциональные схемы формирователейпроверочных символов; на фиг, 4 - функциональная схема арифметического блока; нафиг,5 - функциональная схема блока вычисления коэффициентов; на фиг, 6 - функциональная схема блока определенияошибочных позиций; на фиг. 7 - функциональная схема блока исправления ошибок;на фиг, 8 - функциональная схема блокауправления; на фиг, 9 - временная диаграмма работы устройства,Устройство для декодирования с исправлением ошибок содержит блок задержки1 (фиг. 1), выполненный на сдвиговых регистрах, шесть формирователе проверочныхсимволов 2, , 7, арифметический блок 8,блок вычисления коэффициентов 9, блок определения ошибочных позиций 10, блок исправления ошибок 11, блок управления 12,два элемента И 13 и 14, элемент ИЛИ 15,информационный вход 16, тактовый вход ивход ПУСК 17 и 18 и выход 19,Блок задержки 1 содержит (2 +5) вразрядов, где в - степень неприводимогомногочлена в поле б Ц 2 ). имеет последовательный информационный вход и вход тактовых импульсов (ТИ), группу параллельныхщ выходов (с первого по а-й) и последовательный выход. Далее принимаем в=4, В этом случае блок задержки 1 будет иметь 84 разряда.Формирователи 27 служат для формирования соответственно с первого по шестой проверочных символов, Первый из формирователей 2 включает в себя (фиг, 2) с первого по третий буферные регистры 20, 21, 22, сумматор 23, вычитатель 24 и преобразователь кода 25. На фиг, 2 обозначены также информационный вход 26, управляющие входы 27, 28, 29 с первого по третий и выход 30 формирователя,Другие формирователи (3 - 7) включают в себя (фиг. 3) с первого по четвертый буферные регистры 31, ., 34, первый и второй сумматоры 35, 36, вычитатель 37 и преобразователь кода 38. На фиг, 3 обозначень 1 также информационный вход 39, группа управляющих входов 40, управляющие входы 41;, 44 с первого по четвертый соответственно и выход 45 формирователя.Арифметический блок 8 включает в себя (фиг, 4) с первого по двадцать шестой вычитатели 4671, с первого по тринадцатый сумматоры 7284, первый и второй умножители на 2 85 и 86 и с первого по девятый преобразователи кода 87.95, На фиг. 4 обозначены также с первого по шестой информационные входы 96,101 и с первого по двенадцать 1 й выходы 102 .113.Блок 9 вычисления коэффициентов включает в себя (фиг. 5) с первого по одиннадцатый вычитатели 114124, с первого по шестой сумматоры 125130, с первого по шестой преобразователи кода 131136 и первый, второй и третий регистры 137, 138, 139. На фиг. 5 обозначены также с первого по двенадцатый информационные входы 140,151, с первого по третий выходы 152, 153, 154 и управляющий вход 155.Блок 10 определения ошибочных позиций (фиг. 6) включает в себя с первого по 50 55 5 10 15 20 25 30 35 40 пятый сумматоры 156160, с первого по седьмой вычитатели 161167, с первого по шестой преобразователи кода 168173, схему сравнения 174, с первого по третий регистры 175, 176, 177, схему ИЛИ 178 счетчик 179 и с первого по третий вентили 180, 181, 182, На фиг. б обозначены также первые информационные входы 183 - 185; управляющие входы 186, 187, вторые информационные входы 188190, первые выходы191193, вторые выходы 194196,Блок 11 исправления ошибок включает в себя (фиг, 7) три узла по числу исправляемых ошибок, каждый из которых содержит с первого по восьмой сумматоры 198,205, первый, второй и третий вычитатели 206,207, 208, первый второй и третий преобразователи кода 209, 210, 211, На фиг. 7 обозначены также с первого по девятый входы212221 и выход 221 первого узла, с первого по девятый входы 2222.230 и выход 231. второго узла и с первого по девятый входы232,240 и выход 241 третьего узла,Блок 12 управления (фиг. 8) включает всебя первый элемент И 242 на два входа,счетчик 243, дешифратор 244, с первого повосемнадцатый элементы ИЛИ 245262.первый, второй и третий элементы сравнения 263, 264, 265, со второго по седьмойэлементы И 266271, девятнадцатый идвадцатый элементы ИЛИ 272, 273 на тривхода каждая, На фиг. 8 обозначены такжетактовый вход 274, вход 275 сигнала "ПУСК"и первый выход 276 сигналов ТИ, перваягруппа выходов 277279, вторая группа выходов 280284, третья группа выходов285,289, четвертая группа выходов290294, пятая группа выходов 295299,шестая группа выходов 300304, второйшестой выходы 305 - 309, информационныеВходы 310.312.Сумматоры 23, 35, 36, 7284, 125130,156160, 198205, соответствующих блоков работают по модулю 2-1. Если выходырегистров 20 и (или) 32 имеют во всех разрядах единицы ( со), то передача суммы с сумматоров 23 и (или) 36 на регистры 21 и (или)33 запрещается, для чего регистры 20 и(или) 32 имеют специальный выход, закрывающий входные вентили регистров 21 и(или) 33,Вычитатели 24, 37, 4671, 114124,161, 167. 206, 207, 208 соответствующихблоков работают по модулю 2-1. Входуменьшаемого вычитателя 166 принудительно обнулен.Преобразователи кода 25, 38, 8795,131,136, 168173, 209, 210, 211 осуществляют над входной величиной г преобразован ие сР = 1 О+ а, где а С О Г(2 ), е -суммирование в поле ОГ(2").На фиг.9 изображены тактовые импульсы ТИ по циклам и соответствующие управляющие сигналы. При совпадениивычисленных значений ошибочных позицийР 4 со значениями счетчика из блока управления ю, блок 11 выдает позиции ошибочных символов ( 1 ъ,ш), соответствующиепримеру, приведенному в описании принципа действия устройства.Принцип действия устройства декодирования с исправлением трех пачек ошибокзаключается в следующем,Кодовые слова, поступающие на входустройства, содержат по (2-1) гп-разрядных информационных символов К(=0,1,2 -2) и шесть проверочных символов К(9=05), формируемых в кодирующем устройстве по формулам5ия )ф яе фст)и передаваемых в декодирующее устройство после информационных символов. Здесь 10 знак означает суммирование в полеОГ(2), примитивный элемент а которого является корнем неприводимого многочлена 1(х) степени гп; т(х)=х +х+1, "+" - сложение в кольце по модулю (2" - 1)15 Если в информационной части кодовогослова при передаче или хранении информации возникли ошибки в трех символах, то акц - сформированные в декодере проверочные символы - определяются по формуле: " г-а1. ; . м; ; , 13аООи,1 (ггде д 1, др. и д - величины ошибок на -й, 1 "й, -й позициях соответственно,в - сложение в поле ОГ(2").Формирование проверочных символовв соответствии с формулой (1) можно записать так:Обозначим сумму первых, двух членова , сумму ас третьим членом - ак и т.д.Тогда:у (0 г+ф к,фЯ 1 Рс-к,-ф 40илиК 1 К 1+9+ (Р(КО К 1 9)где сУ =1 ю сР (3)и операции сложение "+" и вычитание "-"производятся по модулю (2"-1).В общем случае будем иметь;К =К+1 9+ Р(К 1-1 -К 1- 9).Очевидно, что Ко 1=Ко, и50 Кя= Кг -1+ Р - Л)9 +СР(КЗ - 3 -- Кгф-г - (2-2) 9).По проверочным символам К и К формируют синдромы ошибокФц =а 9 ав, (4)откуда:179 (165 Аналогично: ЬгЬг Ь гь, агг(а аг).9 а -а ) ьь Ьгг ьг ььг ь,Из сравнения (18) иния, между а) и Ьаг =Ьг,(а.а,-а;)-а, 1, Получим ьь г(а,-а,) Ч(аг-а,)-аг Ч(а .айь зуем но ал г Ч(ав-аг).Ч(а,-о,а,-а,)-Ч(о; подставля уравне степени 0 Д оУ а 2 Р отк 352 гг сг 2 гг(Й о-гг с( г-О ли, умножая на,а" 2 г 2 а 2,В, д 5 г Оо в виде ли, умножая на сР обе части: Представим уравнени2(с(2"О ( Я Раскрывая скобки, получим Згг 2 д.ФЬ, гггРь Рг, ФА Ю,с( (В с( г яа аг(Ь) - Ьо + Ьо - У + ф (Ьо -Р = О. (25)Обозначим Ьо=ю=у, Ь)-Ьо=Ь, -(Ьг-Ь 1)=с, тогда (25) примет видЬ "+у+ фЬ "+у+ фу=с. (26)Формула (26) позволяет представить уравнениетретьей степени(26) как функцию двух аргументов Ь и с, т,е. у=Ь, с).Составим таблицу, в которой с=1(Ь, у) образуют замкнутые кольца по модулю 15. Для удобства далее начало кольца будем счита.ть в ячейке с Ь=0.Кольцо с началом в ячейке(0,0) обладает свойствому=с (26,1) Кольца с началом в ячейках (0,5) и (0,10) обладают свойствомс),)= ф-Ь)+). (27) Остальные кольца обладают свойством:фс-бк)+ б=-ЬО, (28) где А - величина, на которую нужно уменьшить содержимое ячейки (Ь", у), т.е. с. чтобы кольцо имело такую же последовательность элементов, как и функция фг);Умножим (38) нэ а и сложим с (39)получимоткуда, используя (34), получимилиВ сг ": 8, "г.,(г д "с,.ев,с.-с,-с, ь . А ЭЯ (уф 2 2 АналогичноИсправленные по формулам (40, 41, 42) символы заменяют испорченные символы на позициях ф, ю и) соответственно, определяемых при решении кубического уравнения (33).Устройство декодирования с исправлением ошибок работает следующим образом (на фиг. 10 представлена временная диаграмма работы устройства при гп=4),Нэ вход 16 устройства поступают блоки информации по (15) информационных 4-разрядных символов и шесть проверочных символов, содержащих три неисправных символа.Первые 4 такта следует О-й цикл, в течение которого по сигналам ТИ заполняются первые 4 разряда блока задержки 1.Затем следует первый цикл (с 5 по 8 такты), в течение которого по сигналам Ь (И 6) производится запись первого информационного символа К 0 на регистр 20 формирователя 2 и на регистры 31 формирователей 37. Далее производится вычитание из содеркимого регистра,22 ( с 0) содержимого регистра 20 (К 0) на вычитателе 24; результат ( с 0 ) поступает на преобразователь кода 25 и далее на сумматоре 23 формирователя 2 производится сложение символа Ко с нулем на выходе преобразователя кода 25 и запись результата на регистр 21 по сигналу Ь 1 . Одновременно на суммагторах 35 формирователей 37 производится сложение содержимых регистров 31 с порядковыми номерами соответствующего формирователя проверочных символов (15), умноженными на "0" (=0), поступающими из блока управления на контакты 40 формирователей 3,7 с записью результата нэ регистры 32 по сигналам Ь 1 (1). Далеепо сигналу Ь 1 осуществляется перепись создержимого регистра 21 на регистр 22 формирователя 2 и вычитание из содержимых5 регистров 34 ( О 1 формирователей 37 содержимого регистров 32 (Ко) на вычитателях37; результаты ( оо ) поступают на преобразователи 38 кода и затем на сумматорах 36производится сложение "0" (выходы преоб 10 разователей 38) с содержимым регистров 32(К 0) и запись результатов на регистры 33 посигналам Ь ( 1).Во втором цикле (с 9 по 12 такты) посигналу Ь 1 производится запись на регистр15 20 формирователя 2 второго символа К 1, вычитание иэ содержимого регистра 22 (Ко)содержимого регистра 20 (К 1) с преобразованием разности (Ко - К 1) нэ преобразователе 25, сложение полученного резуЛьтата20 (р (Ко-К 1) на сумматоре 23 с содеркимымрегистра 20(К 1) и запись результатаК 1 =К 1+ р (Ко-К 1) на регистр 21 по сигналу2Ь 1 . Одновременно К 1 по сигналам Ь (1 1)записывается на регистры 31 формировате 25 лей 37 и на сумматорах 35 складывается свеличиной д (сигналы Ь;"), поступающей нэконтакты 40 формирователей 37 с контактов 284, 289, 294, 299, 304 блока 12 управления; результаты записываются на30 регистры 32 формирователей 37 посигналам Ь (11). Одновременно по сигна 2лам Ь (31) производится перепись содержимого регистров 33 на регистры 34. Далеена вычитателях 37 осуществляется вычита 35 ние из содержимого регистров 34 (Ко) содержи мо го регистров 32 (КО+19),преобразование результатов на преобразователях 38 и сложение с содержимым регистров 32 на сумматорах 36 с эапись 1 о суммы40 К 1 =К 1+д+ р(Ко-К 1-д) на регистры 33 по сигналам Ь (И). Одновременно по сигналу Ь 1осуществляется перепись содержимого регистра 21 на регистр 22 формирователя 2.Циклы с третьего по 15-ый аналогичнывторому, при этом в 15-м цикле по сигналуЬ 1 на регистр 20 формирователя 2 записывается последний символ К 21 П - 2, формируется первый проверочный символ Ко ипомещается на регистр 21 формирователя 2по сигналу Ь 1 . Одновременно по сигналамЬ производится перепись предпоследнихсимволов К 3 п - з с регистров 33 на регистры 34 фооэмирователей 37 и, затем, по сиг 55 налам Ь ( Ф 1) - запись на регистры 33сформированных проверочных символовсо второго по шестой (К 1 К 5) и по сигналуЬ 1 - перепись символа Ко на регистр 223форл 1 ировэтеля 2,1797165 10 15 20 25 30 45 50 В следующем 16-м цикле на регистр 20формирователя 2 по сигналу Ь 1 записывается первый принятый проверочный символКо производится формирование первогосиндрома ошибки и по сигналу Ь 1 запись2результате ( Ьо=Ко+ р(Ко-Ко на регистр 21формирователя 2. Одновременно, по сигналам Ь 1 производится перепись провероч 4ных символов К( Ф 1) с.регистров 33 нарегистр 34 формирователей 37,В 17-м цикле на 1 оегистр 31 формирователя 3 по сигналу Ь 2 записывается второйпринятый проверочный символ К 1, на сумматоре 35 производится его сложение с "нулем (Ь =О) с записью результата К 1 нарегистр 32 по сигналу Ьи затем формирогвание второго синдрому ошибки с записьюрезультата Ь 1=К 1+ р(К 1-К 1) на регистр 33формирователя З.по сигналу Ь 2 з.Аналогично в циклах с 18 по 21 по сигналам Ь (1=3, 4, 5, 6) на регистры 33 формирователей 4, 5, 6, 7 записываютсясформированные на них с третьего по шестой синдромы ошибок Ьй соответственно.Сформированные таким образом синдромы ошибок поступают на входы 96101арифметического блока 8, с выходов 104,109, 111, 105,.106, 102, 108, 107, 112, 103, 110и 113, которых поступают на входы 140.151блока 9 вычисления коэффициентов соответственно, где сформированные коэффициенты Ьо, Ь 1 и Ь 2 записываются нарегистры 137, 138 и 139 соответственно посигналу Ь 1, поступающему на вход 155 блока, С выходов регистров 137, 138 и 139 значения коэффициентов Ьо, Ь 1 и Ь 2 поступаютна выходы 152, 153 и 154 блока соответственно и далее на входы 183, 184 и 185 блока10 определения ошибочных позиций, где поформуле (32) вычисляется иь 4 - номер очередной позиции и сравнивается с с 4, поступающей на входы 186 блока 10 с выходов308 блока 12 управления,При равенстве ть 4 и ю,4 элемент сравнения 174 выдает импульсы на счетчик 179,Формула изобретения 1, Устройство для декодирования с исправлением ошибок. содержащее блок задержки, первый вход которого является информационным входом устройства, первые в параллельных выходов подключены к соответствующим информационным входам первого, второго, третьего и четвертого формирователей проверочных символов, а соответствующий вьход которого разрешает выдачу номера позиции неисправного символа с сумматора 160 через соответствующий вентиль 180, 181 или 182 на выходы 5 193, 192 или 191 блока соответственно и далее на входы 310, 311, 312 блока управления 12, и на разрешение записи исправленных в блоке 11 символов на регистры 175;176 и 177 и на формирование символов со, с 1 и с 2, поступающих на выходы 194, 195 и 196 блока соответственно. Исправленные символы последовательно поступают на элемент ИЛИ 178 и далее с контакта 197 - на первый вход элемента И 14 устройства, откуда в сопровождении ТИ 2 через элемент ИЛИ 15 - на выход 19 устройства.С входов 310, 311 и 312 блска управления 12 номера ф, ю и ) неисправных символов поступают на первые входы элементов сравнения 263, 264 и 265, на вторые входы которых с дешифратора 244 поступают номера четверок импульсов, При совпадении их с номерами позиций элементы сравнения разрешают выдачу ТИ 2 через элементы И 269, 270, 271, ИЛ И 272 на выход 305 блока для стробирования исправления символов,а при несравнении разрешают выдачу сигналов ТИ 1 через элементы И 266, 267, 268 и ИЛИ 273 на выход 306 блока (сигналы ТИ 1).С выходов 306 блока управления сигналы ТИ 1 поступают на вторые входы элемента И 13 (фиг, 1), а с выходов 305 сигналы ТИ 2 поступают на вторые входы элемента И 14,Таким образом, применение пятого и шестого формирователей проверочных символов, арифметического блока, блока вычисления коэффициентов, блока определения ошибочных позиций, решающих совместно показательное уравнение третьей степени в40 поле ОГ(2"), позволяет определить ошибки в трех любых ошибочных символах и с помощью блоков управления, определения ошибочнь 1 х позиций и блока исправленияошибок исправить их, что повышает надежность канала связи. последовательный выход подключен к первому входу первого элемента И, выход которого подключен к первому входу элемента ИЛИ, выход которого является выходом устройства, блок управления, тактовый вход и вход "Пуск" которого являются одновременными входами устройства, первый и второй выходь 1 блока управления подключены соответственно к тактовому входу блоказадержки и второму входу первого элемента И, блок исправления ошибок и блок вычисления ошибочных позиций, о т л и ч аю Щ и й с я тем, что, с целью повышения достоверности декодирования за счет исправления до трех пачек ошибок, в устройство введены блок вычисления коэффициентов, арифметический блок, второй элемент И и пятый, шестой формирователи проверочных символов, информационные входы которых подключены к первым п параллельным выходам блока задержки, выходы всех формирователей проверочных символов соединены с соответствующими первыми входами блока исправления ошибок и входами арифметического блока, выходы которого подключены к информационным входам блока вычисления коэффициентов, выходы которого подключены к первым информационным входам блока определения ошибочньх позиций, первые параллельные выходы которого подключены к вторым входам блока исправления ошибок и информационным входам блока управления, вторые выходы блока определения ошибочных позиций соединены с третьими входами блока исправления ошибок, выходы которого подключены к вторым информационным входам блока определения ошибочных позиций, последовательный выход которого подключен к первому входу второго элемента И, третий выход блока управления соединен с вторым входом второго элемента И, выход которого подключен к второму входу элемента ИЛИ, выходы первой-шестой групп выходов блока управления подключены к соответствующим управляющим входам первого-шестого формирователей проверочных символов, четвертый, пятый и шестой выходы подключены соответственно к управляющему входу блока вычисления коэффициентов и первым и второму управляющим входам блока определения ошибочных позиций.2. Устройство по и. 1, о т л и ч а ю щ е ес я тем, что первый формирователь проверочных символов выполнен на буферных регистрах, вы читателе, сумматоре и преобразователе кода, информационные входы первого буферного регистра являются информационными входами формирователя, первые выходы первого буферного регистра подключены к входам вычитаемого вычитателя и к первым входам сумматора, выходы которого подключены к информационным входам второго буферного регистра, выходы которого подключены к входам третьего буферного регистра и являются выходами формирователя, выходы третьего буферного регистра подключены к входам уменьшаемого вычитателя, выходы которого через преобразователь кода подключены к вторым входам сумматора. управляющийвход первого буферного регистра, первыйуправляющий вход второго буферного регистра и управляющий вход третьего буферного регистра являются соответственно первым, вторым и третьим управляющими входами формирователя, второй выход первого буферного регистра подключен к второму управляющему входу второго буферного регистра,3,Устройство по и. 1, отл ич а ю щеес я тем, что каждый иэ второго-шестого формирователей проверочных символов выполнен на буферных регистрах, сумматорах, вычитателе и преобразователе кода, информационные входы первого буферного регистра являются информационными входами формирователя, выходы первого буферного регистра подключены к первым входам первого сумматора, выходы которого подключены к информационным входам второго буферного регистра, первые выходы которого подключены к входам вычитаемого вычотателя и к первым входам второго сумматора, выходы которого подключены к информационным входам третьего буферного регистра, выходы которого подключены к информационным входам четвертого буферного регистра и являются выходами формирователя, выходы четвертого буферного регистра подключены к входам уменьшаемого вычитателя, выходы которого через преобразователь кода подключены к вторым входам второго сумматора, управляощие входы первого и второго буферных регистров, первый управляющий входтретьего буферного регистра и управляющий вход четвертого буферного регистра являются соответственно первым, вторым, третьим и четвертым управляющими входами формирователя, вторые входы первогосумматора являются первыми управляощими входами формирователя, второй выход второго буферного регистра подключен к второму управляющему входу третьего буферного регистра.4. Устройство поп.1,отл ича ю щеес я тем, что первый арифметический блок выполнен на вычитателях, сумматорах, умножителях на два и преобразователях кода, входы вычитаемого первого вычитателя являются первыми входами блока, входы уменьшаемого 1-го вычитателя 1=1,43 обьединены с входами вычитаемого (1+1)-го вь- читателя и являются (1+1)-ми входами блока, входы уменьшаемого пятого вычитателя являются шестыми входами блока, выходы

СмотретьЗаявка

4819741, 28.04.1990

НАУЧНО-ПРОИЗВОДСТВЕННОЕ ОБЪЕДИНЕНИЕ "ЭЛАС"

КАРПУХИН АНАТОЛИЙ ИВАНОВИЧ

МПК / Метки

МПК: H03M 13/02

Метки: декодирования, исправлением, ошибок

Опубликовано: 23.02.1993

Код ссылки

<a href="https://patents.su/18-1797165-ustrojjstvo-dlya-dekodirovaniya-s-ispravleniem-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для декодирования с исправлением ошибок</a>

Предыдущий патент: Декодер кода нордстрома-робинсона

Следующий патент: Устройство защиты от импульсных помех

Случайный патент: Способ получения многополюсных постоянных магнитов