Модульная многоуровневая система коммутации процессоров

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1249524

Автор: Горбачев

Текст

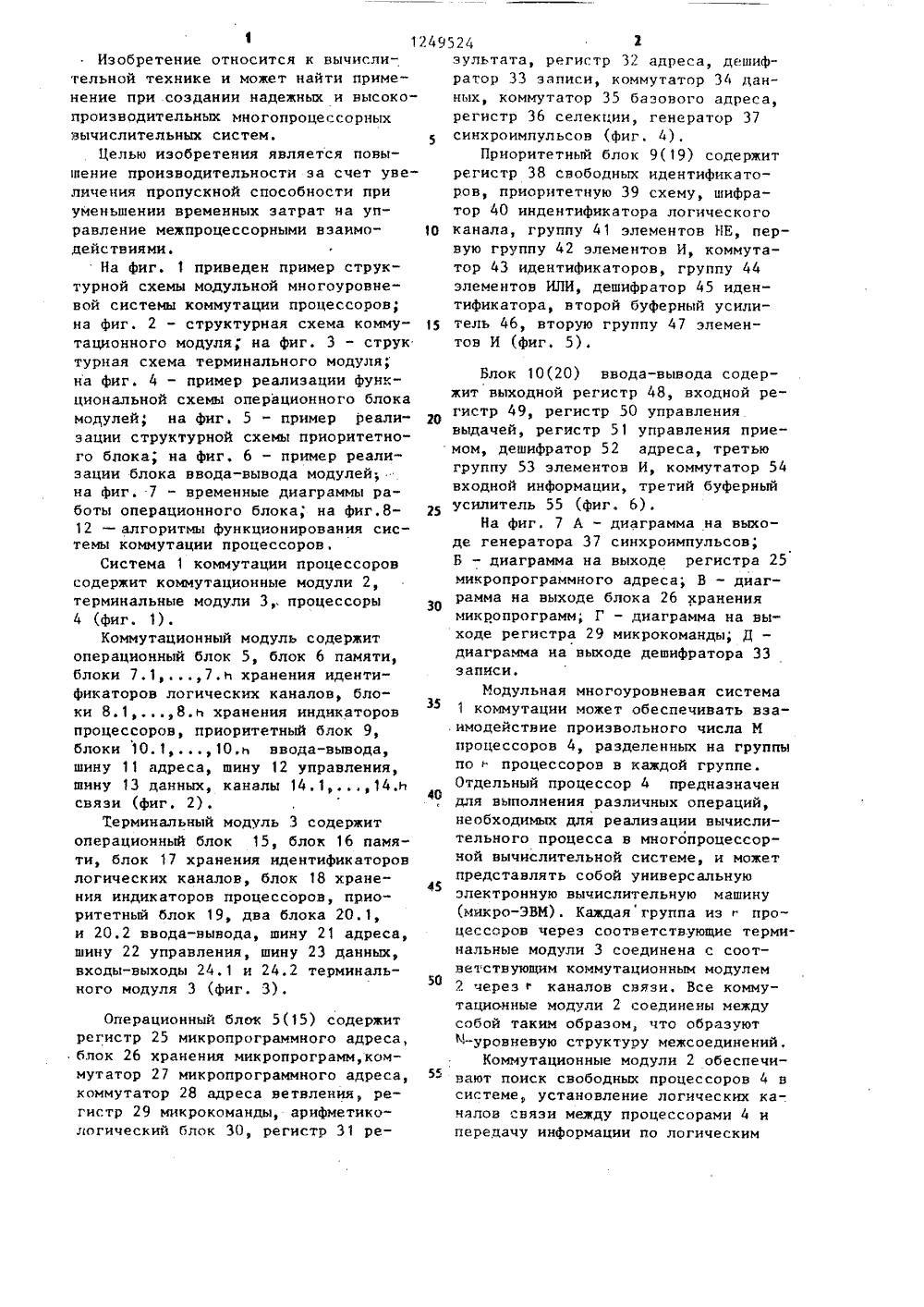

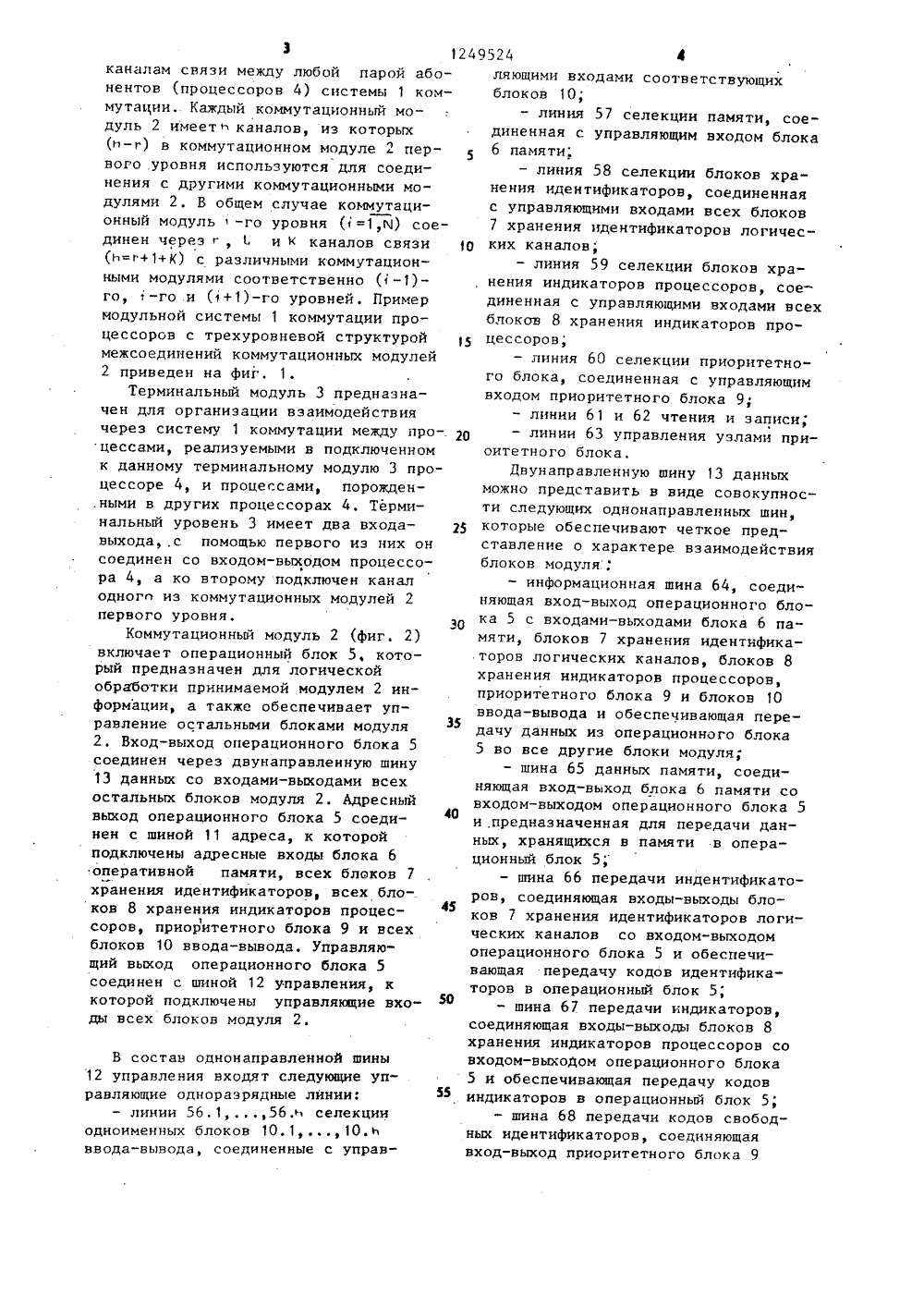

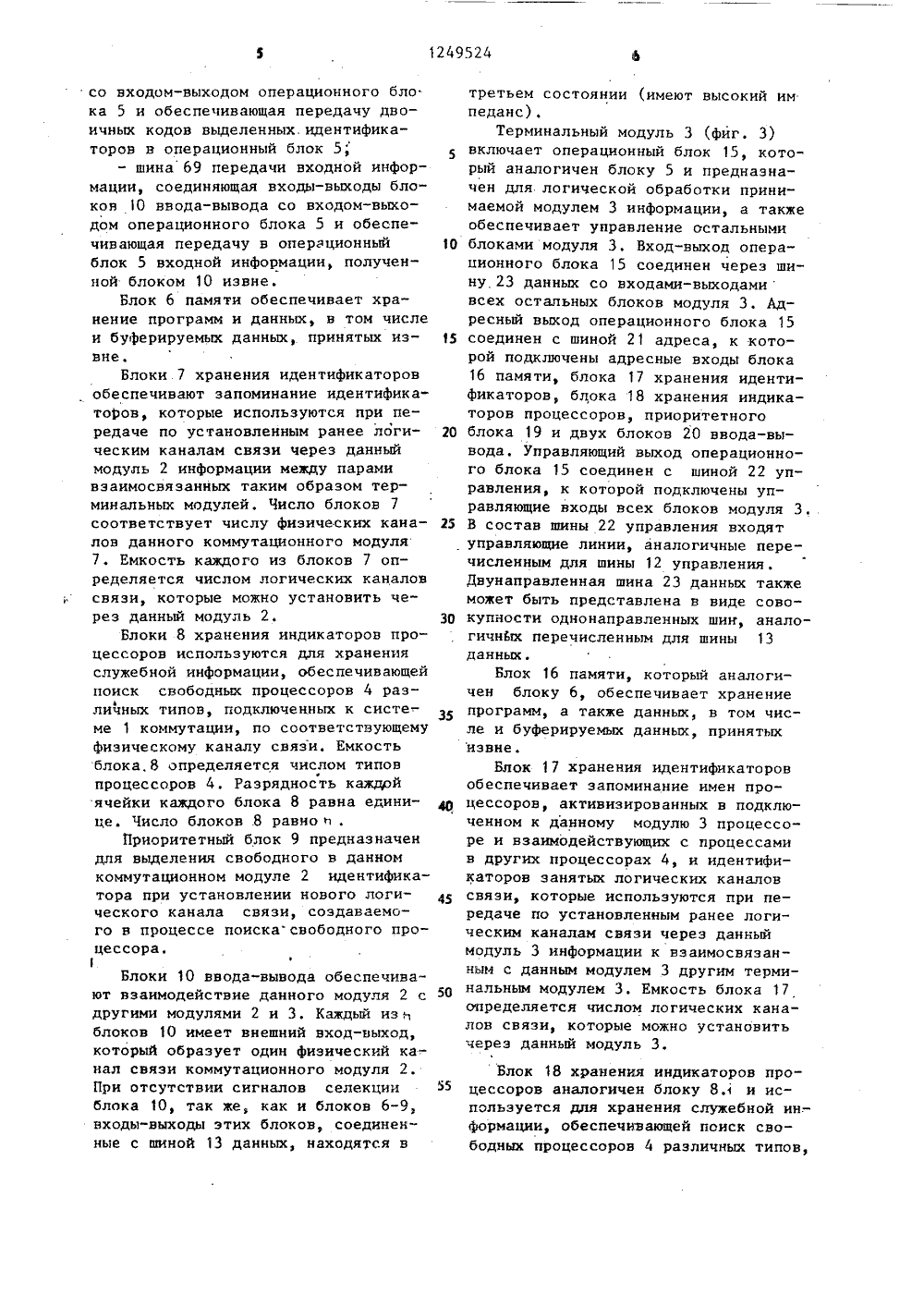

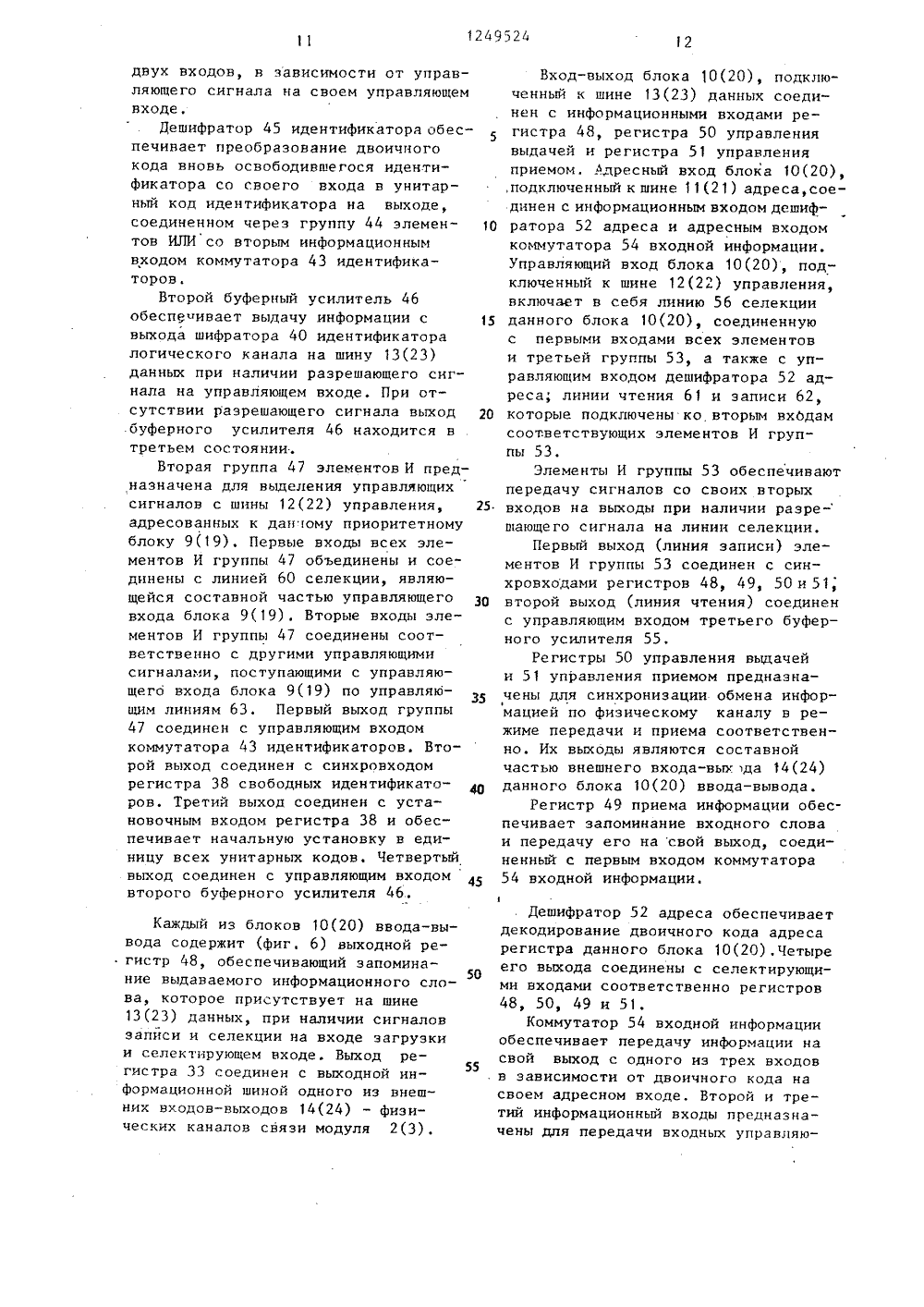

(19) (11) 9524 А я) 4 С 06 Р 15/1 ГОСУДАРСТВЕННЫ ПО ДЕЛАМ ИЗОБРЕ ОМИТЕТ СССРНИЙ И ОТКРЫТИЙ 4 1 ф) я 4р ОПИСАНИЕ ИЗОБРЕТЕН ВТОРСКОМУ СВИ ЛЬСТВУ итут авиации Стецюра Г.И мы, М.: "Науво СССР16, 1982.во СССР16, 1982,(54) МОДУЛЬНАЯ МА КОММУТАЦИИ (57) Изобретен лительной техн тить временные МНОГОУРОВНЕВАЯ СИСТЕРОЦЕССОРОВе относится к вычиске и позволяет сокраатраты при поиск(7 1) Ленинградский инсонного приборостроения(56) Прангишвилли И.В.Микропроцессорные систка", 1980, с, 194.Авторское свидетельУ 9837 14, кл. С 06 Г 1Авторское свидетель1(я 962965, кл. С 06 Г 15 свободного процессора в многопроцессорной вычислительной системе. Система 1 коммутации процессоров состоит из совокупности коммутационных модулей 2, расположенных на несколькихуровнях, и терминальных модулей 3,предназначенных для организации взаимодействия через систему 1 междупроцессами, реализуемыми в процессоре 4 данного терминального модуля 3,и процессами в других процессорах.Поиск свободного процессора и одновременное установление логическогоканала к нему осуществляется децентрализованно коммутационными модулями 2 на,.основании служебной информации, имеющейся в каждом из них и динамически отображающей наличие в текущий момент свободных процессоров.1 з.п., ф-лы, 12 ил.сигнала записи из операционного блока 5 на синхровход регистра 38 в нем запоминается новая суперпозиция кодов. Двоичный код выделенного иден- Этификатора с выхода шифратора 40 через второй буферный усилитель 46 считывается в операционный блок 5.Для установления логического канала через данный модуль 2 принятый 10 с командой и вновь выделенный идентификаторы запоминаются в соответствующих блоках 7 хранения идентификаторов. При этом в блок 7., в первую половину ячейки по адресу, оп ределяемому двоичным кодом принятого идентификатора, записывается двоичный код вновь занятого идентификатора и код выходного физического канала 5, а в блоке 7. во вторую поло вину ячейки по адресу, определяемому двоичным кодом вновь выделенного идентификатора, записывается код принятого идентификатора и код входного физического канала. Затем в 25 команду на место принятого идентификатора подставляется выделенный в данном модуле 2 идентификатор, и команда выдается в определенный ранее выходной физический канал эче реэ блок 10. 5 ввода-вывода.Обрабатываемая таким образом в коммутационных модулях 2 эта коммутационная команда обеспечивает поиск ближайшего свободного процессора требуемого типа и одновременное установление с ним двустороннего логического канала связи, При поступлении в найденный свободный процессор 4 коммутационной команды "Установка 40 виртуального каналаон переходит в активное состояние в нем порождается необходимый процесс, имя порта которого он сообщает своему терминальному модулю 3. Это имя порта за писывается в блок 17 хранения идентификаторов, в первую половину ячейки по адресу, равному коду принятого идентификатора. Кроме того, во вторую половину ячейки блока 17 по ад ресу, определяемому именем порта, записывается код принятого идентификатора, После этого модуль 3 выдаетв систему 1 коммутации коммутационную команду "Сброс индикатора с-го 55 типа". Описанная процедура установления логического канала связи при поиске свободных процессоров может выполняться одновременно в различных модулях системы 1 коммутации процессоров, что обеспечивает возможность параллельной обработки запросов на свободные ресурсы различных типов, которые независимо поступают в терминальные модули 3.После логического связывания процессоры 4, являющиеся абонентами одного логического канала, могут обмениваться информацией по существующему между ними двустороннему логическому каналу (алгоритм на фиг. 10). Для этого передаваемое сообщение из процессора 4 должно поступить через соответствующий блок 20 ввода-вывода в блок 16 памяти терминального модуля 3. Это сообщение в терминальном модуле разбивается на отдельные пакеты, которые последовательно передаются через коммутационные модули 2 по созданному логическому каналу связи терминальному модулю 3, получателю сообщения. Для этого используются коммутационные команды "Передача по прямому (обратному) логическому каналу".Каждая из этих команд содержит в заголовке кроме кода команды еще и идентификатор, соответствующий используемому логическому каналу. Тело команды составляет пакет информации. При прохождении этих команд через модули 2 осуществляется замена принимаемого идентификатора. на хранящийся идентификатор в соответствующем блоке 7, Номер выходного физическоГо канала также считывается из соответствующей ячейки блока 7.Терминальный модуль 3, получатель информации, последовательно принимает отдельные пакеты, собирает их в целое сообщение, подтверждая этот факт терминальному модулю 3, отправителю сообщения. После этого принятое сообщение выводится в процессор 4 приемник информации,1После окончанкя взаимодействия процессоров 4 через логический канал связывающий их, этот канал может быть разрушен путем выдачи из терминального модуля 3, инициатора его установления, коммутационной команды "Разрушение виртуального канала , которая сопровождается идентификатором данного канала, Эта команда следует через модули 2 пс установленному ранее логическому каналу, уничтожая его, Для этого в каждом модуле 2 стирается служебная информация в блоках 7 хранения идентификаторов. Унитарный код освобождаемого идентификатора восстанавливается в регистре 38 свободных идентификаторов приоритетного блока 9, после чего он может быть снова ис О польэован в данном модуле 2 для установления новых логических каналов.Таким образом, в предлагаемом устройстве за счет децентрализованного и параллельного выпопнения раз личными терминальными и коммутационными модулями процедур поиска сво-. бодных процессоров 4 и одновременного установления логических каналов связи между ними достигается по срав нению с известным устройством уменьшение времени формирования логической связи между процессорами. Использование терминальных модулей 3 для организации межпроцессорных вза имодействий существенно снижает загрузку процессоров, связанную с распараллеливанием вычислительного процесса на множестве подключенных к системе 1 коммутации процессоров. ЗО Все это способствует повышению производительности вычислительной системы в целом.1Сравнение процедур установления логических каналов показывает следующее. При волновом алгоритме поиска пути к свободным процессорам вре" менные затраты всех коммутационных модулей, необходимые для установления одного логического канала, пропорциональны числу процессоров в системе, поскольку распространение одной "волны" поиска пути, по сути дела, означает попытку установления Млогического канала от процессора- инициатора ко всем остальным Мпроцессорам системы. В то же время, в предлагаемом устройстве эти временные затраты определяются усредненной длиной пути между процессорами. Это следует из того, что при поиске свободного процессора всегда устанавливается только один логический канал к ближайшему свободному вычислительному модулю на основе анализа индикаторов процессоров, имеющихся в каждом коммутационном модуле. Это сравнение также свидетельствуе об уменьшении загрузки многоуровневой структуры системы коммутации процес соров и, следовательно, об увеличении ее пропускной способности.,Формула изобретения1. Модульная многоуровневая сис-тема коммутации процессоров, содержащая М уровней коммутационных модулей, входы-выходы которых через каналы связи подключены к входам-выходамкоммутационных модулей своего и вышерасположенного уровней, причем каждый коммутационный модуль содержит операционный блок, блок памяти, приоритетный блок и П, блоков ввода- вывода, где рь - число каналов связи, входы-выходы которых являются входами-выходами обмена коммутационных модулей, адресный выход и выход,управления операционного блока подключены через шину адреса и шину управления к адресным входам и входам управления блока памяти, приоритетного. блока и блоков ввода-вывода соответственно, информационный вход-выход операционного блока подключен через шину данных к информационным входам-выходам блока памяти, приоритетного блока и блоков ввода-вывода, входы-выходы обмена которых являются входами-выходами обмена коммутационных модулей, о т л и - ч а ю щ а я с я тем, что, с целью повышения производительности путем увеличения пропускной способности при уменьшении временных затрат на управление межпроцессорными взаимодействиями, в нее введены М терминальных модулей, где М - число процессоров, подключенных к системе, разбитых на группы потерминальных модулей в каждой группе, первый вход- выход обмена каждого терминальногомодуля является соответствующим входом-выходом сопряжения системы коммутации, вторые входы-выходы обмена .терминальных модулей одной группы соединены через г соответствующих каналов связи свходами-выходами обмена одноГо иэ коммутационных модулей первого уровня, каждый из которых соединен соответственно по крайней мере одним каналом связи с расположенными на том же и более высоком уровнях коммутационными мо1249524 21 2. Система по п. 1, о т л и ч аю щ а я с я тем, что терминальный модуль содержит операционный блок,Входы схемы 39Т Т Выходы схемы 391 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 О 0 0 0 0 1 О. 0 0 0 0 0 1 Х 0 0 0 0 0 О 1 0 0 0 0 0 0 1 Х Х 0 0 0 0 0 1 0 0 0 0 0 О 1 Х Х Х 0 0 0 0 1 0 0 0 0 О 1 0 0 0 0 0 .0 0 1 Х Х Х Х О. О 1 0 0 0 О 0 0 0 1 Х Х Х Х Х 0 1 О. 0 0 0 0 0 0 1 Х Х Х Х Х Х 0 0 О 0 0 О О 0 1 Х Х Х Х Х Х Х 1 Х - безразличное состояние,дулями, каждый из которых дополнительно содержит И блоков храненияидентификаторов логических каналови и. блоков хранения индикаторов процессоров, входы"выходы которых соединены через шину данных с входамивыходами блоков хранения идентификаторов логических каналов, управляющие входы которых соединены через шину управления с управляющимивходами всех блоков хранения индикаторов процессоров, адресные входыкоторых соединены через шину адресас адресными входами всех блоковхранения идентификаторов логическихканалов. блок памяти, блок хранения идентификаторов логических каналов, блокхранения идентификаторов логическихканалов, блок хранения индикаторовпроцессоров, приоритетный блок идва блока ввода-вывода, адресныйвыход, выход управления и информационный вход-выход операционного бло 1 п ка подключены через шины адреса,управления, данных к адресным входам, входам управления и информационным входам-выходам блока памяти,приоритетного блока, блока храненияидентификаторов процессоров, блокахранения индикаторов процессоров ипервого и второго блоков ввода-вывода, входы-выходы первого и второгоблоков ввода в выво являются первыми вторым входами-выходами обмена терминальногомодуля,нкаторов цессоров индывторо аэд Зэка и тарулей Са в системекозачутацим логическив каналОВ гензн наказу продессорамн ла запросам, поступамаю одновременно иезависию от РамеНЫ ВКТМЭЗЙМ процессора 1 э П 1 ГНг:ЗНТЛЗВыслча нз процессораТГРМННЗЛЪцй НОДУ 1 Ь запроса нэ ресуРсопределенного типа ь сааба ни т формирование н вмпачз з терминального модуле источника, э гневный коммутационный мОдуль команды Понсэ побопного процссора требуемого типа"станонл кзналв лог сно Скати ЧЕРезонный нопультермннальнопечнику/, кПОДКЛЕЧЕНЛРОЦе ССОРго типа оммутацнблиеайаенуалулп /пр 3 отарань Ободный тпгбтен о рмнрованне н выдачсообиснметерминального модул РНЕЧННКВ, Э ПРОЦЕССО атргбомнин его ргг и Ивмцыалм зацыйсистезе Выдача кавльвзтермннальньазкоманды "Устиклмкатора" установка индсвободина прв тэблмцакПРОЦЕССОРОВвомиутацновнонниэльного н 1249524 Активациэ найденного процессоранэ ектнвированногпроцессора в егомннальимй надулкнэ Процессор ованне н выдач ернннального мод приемника, в омеутадионазй модул кандгб ннднкаторан,лрн дог тр кат источ Полт устаиОэйимт И Выдачдального надулемвнка, лооеянаму лагнчесплу сэкзиертвтиал зизак модиик сообдеинкеркденпеВЛЕННЭ СЕЭЗН Ворнмраэе терминал источник сообвеин ресурсВ ее юноа ело т тифропессорое ао лотн ескмн каналамОередйчаОдтотовневюого сообМана аз лропфссаоаисточппке зго тйрапалва мппьлв длн носледьпвед доставки через сне темь ковегутапнн Оропессорь иРазбиение всего сообаепнл ма Оакетм Выделанна очерваного ОО порлдку пакета а ОВормлевса егоэнде юаФорнепновнОГО кадреВвеча мнВормапнонкогокедра из терюпзлвпогоНОДУЛВ й Смтапв ациопнв но лвьбермзепме прмаетого кадраблоке ланнтюОвйтутапюонпого модулю 1249524 Занйнйконмттедноином модулапдеатнрнкзтора логвческфго каналаэ заголовке прнннтогоадра ва нкентнбнквтор,аранввнйсюа Гоответствунмйд кчтокеленатн блока храасннв,юдентнрнкзтороэ,онер которогоолределестсе понеронКОДНОГО ФНЗНЧВСКОГОкана Опрслтлсннг номеравмодного Физического кзнвлзВыдача бусч ннрозвнногокедра нт блока лзннтнп 09 утацноннггоМОДУЛН ЧСРЕЗ бЛОКЭОЛВ-ВНЭОДС, Нанзркоторого соответствуетнонерт еыколногоВнзнчегкого ванйлс Взлр поступилтернннллыа нодулввеление пакета иэпгюннтого кадрааввпюе егособираемоесфобпепла э блокенавмтп т вногвнсд умапрвскроэаее и ендйча иэ тереналвмого вздулаобрат вон Заправивп по доги ческсму каавлу водтверпдеиа о Ораеилвнснс приема очерфдаого пюбмр маюсо иного вадра нlмПолучениеп опт вфрзд алийсерлзелвпомсточамке сообпе Всф сообпевзм аередаао Рвффоэелна и передачавз гавеллевоговдула, поточзмна,провфссорзсточкпеевзнал фф оноечеваерааачм сообайнмн 33 арпдви мз тарвйвпйл влаге нпдьз 3 З в воетефбрамюоге сфобпаам 3 парей соетватствузмз. Юпбп вволю взесн 3 в ЗВОПЕСС ОФ Щпевпэвв1249524 Перестроение логнЧеских каналов мекду процессорани н соответствии среализуемьач еьг числит ельньач процессом при ре венин э ачи Вычислительный процесс,соответствующий денной задаче заверфенукОНЕД НВТ Составитель А.ушаков Редактор Н,Егорова Техред О.Гортвай КорректорА.ЗимокосовЗаказ 4326/50 Тираж 671 ПодписноеВНИИПИ Государственного комитета СССРпо делам изобретений и открытий.113035, Москва, Ж, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектиая, 4 Треоуютск дополнительные свободные процессоры длл расцараллелнваинк вычислительного процесса 1Создание в системе коммутации логических каналов мсхду процессорамипо запросамактиепыхпроцессоров Заверненовыполнение ветен алгоритма вы" числительного процессами Раэрунение логического канала кэакончнваим свою работу процессорам путем выдачи пологическому каналунз терминального модуле, инициатора соединении, команды "Разруненне канала" Деэактиеацих процессоров, у которых разрунен последний логический каналФормирование ивьдача иэтерминальныхмодулей, чьипроцессоры сталисвободньаи команды5105 1 1Изобретение относится к вычислительной технике и может найти применение при создании надежных и высокопроизводительных многопроцессорныхвычислительных систем.Целью изобретения является повышение производительности эа счет увеличения пропускной способности приуменьшении временных затрат на управление межпроцессорными взаимодействиями.На фиг. 1 приведен пример структурной схемы модульной многоуровневой системы коммутации процессоров;на фиг, 2 - структурная схема коммутационного модуля," на Фиг. 3 - структурная схема терминального модуляна фиг. 4 - пример реализации Функциональной схемы операционного блокамодулей, на Фиг, 5 " пример реали"эации структурной схемы приоритетного блока; на фиг. 6 - пример реализации блока ввода-вывода модулей;на фиг. 7 - временные диаграммы работы операционного блока, на фиг.812 - алгоритмы функционирования системы коммутации процессоров,Система 1 коммутации процессоровсодержит коммутационные модули 2,терминальные модули 3 процессоры4 (фиг. 1).Коммутационный модуль содержитоперационный блок 5, блок 6 памяти,блоки 7.17.п хранения идентиФикаторов логических каналов, блоки 8.18. хранения индикаторовпроцессоров, приоритетный блок 9,блоки 10.1, ,10, ввода-вывода,шину 11 адреса, шину 2 управления,шину 13 данных, каналы 14 . 1 14.исвязи (фиг, 2).Терминальный модуль 3 содержитоперационный блок 15, блок 16 памяти, блок 17 хранения идентификаторовлогических каналов, блок 18 хранения индикаторов процессоров, приоритетный блок 19, два блока 20.1,и 20.2 ввода-вывода, шину 21 адреса,шину 22 управления, шину 23 данных,входы-выходы 24.1 и 24.2 терминального модуля 3 (фиг. 3). Операционный блок 5(15) содержит регистр 25 микропрограммного адреса, блок 26 хранения микропрограмм,коммутатор 27 микропрограммного адреса, коммутатор 28 адреса ветвления, регистр 29 микрокоманды, арифметикологический блок 30, регистр 31 ре 249524 2 эультата, регистр 32 адреса, дешифратор 33 записи, коммутатор 34 данных, коммутатор 35 базового адреса, регистр 36 селекции, генератор 37 синхроимпульсон (фиг. 4).Приоритетный блок 9(19) содержит регистр 38 свободных идентификаторов, приоритетную 39 схему, шифратор 40 индентификатора логического канала, группу 41 элементов НЕ, первую группу 42 элементов И, коммутатор 43 идентификаторов, группу 44 элементов ИЛИ, дешифратор 45 идентификатора, второй буферный усилитель 46, вторую группу 47 элементов И (Фиг. 5). Блок 10(20) ввода-вывода содержит выходной регистр 48, входной регистр 49, регистр 50 управлениявыдачей, регистр 51 управления приемом, дешифратор 52 адреса, третьюгруппу 53 элементов И, коммутатор 54входной информации, третий буферныйусилитель 55 (Фиг. 6).На фиг. 7 А - диаграмма на выходе генератора 37 синхроимпульсов;Б - диаграмма на выходе регистра 25микропрограммного адреса; В - диаграмма на выходе блока 26 хранениямикропрограмм; Г - диаграмма на выходе регистра 29 микрокоманды; Д -диаграмма на выходе дешифратора 33записи,Модульная многоуровневая система1 коммутации может обеспечивать вза.имодействие произвольного числа Мпроцессоров 4, разделенных на группыпопроцессоров в каждой группе.Отдельный процессор 4 предназначендля выполнения различных операцийнеобходимых для реализации вычислительного процесса в многопроцессорчой вычислительной системе, и можетпредставлять собой универсальнуюэлектронную вычислительную машину(микро-ЭВИ). Каждая группа из г процессоров через соответствующие терминальные модули 3 соединена с соотнетствующим коммутационным модулем2 черезканалов связи, Все коммутационные модули 2 соединены междусобой таким образом, что образуютМ-уровневую структуру межсоединений,Коммутационные модули 2 обеспечи 55 нают поиск свободных процессоров 4 нсистеме, установление логических ка-.чалов связи между процессорами 4 иперецачу информации по логическим9524 3 124 каналам связи между любой парой абонентов (процессоров 4) системы 1 коммутации, Каждый коммутационный модуль 2 имеет г каналов, из которых (и-г) в коммутационном модуле 2 первого .уровня используются для соединения с другими коммутационными модулями 2, В общем случае коммутационный модуль 1 -го уровня ( =1,К) соединен через г, 1 иканалов связи 1 О (и=г+1+К) с различными коммутационными модулями соответственно (1-1) - го, 1 -го и (1+ 1)-го уровней . Пример модульной системы 1 коммутации процессоров с трехуровневой структурой 15 межсоедииений коммутационных модулей 2 приведен на фиг. 1.Терминальный модуль 3 предназначен для органиэации взаимодействия через систему 1 коммутации между про-. 20 цессами, реализуемыми в подключенном к данному терминальному модулю 3 процессоре 4, и процессами, порожден.ными в других процессорах 4. Терминальный уровень 3 имеет два входа выходас помощью первого иэ них он соединен со входом-выходом процессора 4, а ко второму подключен канал одного из коммутационных модулей 2 первого уровня. 30Коммутационный модуль 2 (фиг2) включает операционный блок 5, который предназначен для логической обработки принимаемой модулем 2 информации, а также обеспечивает управление остальными блоками модуля 2. Вход-выход операционного блока 5 соединен через двунаправленную шину 13 данных со входами-выходами всех остальных блоков модуля 2. Адресный выход операционного блока 5 соединен с шиной 11 адреса, к которой подключены адресные входы блока 6 оперативной памяти, всех блоков 7 хранения идентификаторов, всех бло-. ков 8 хранения индикаторов процессоров, приоритетного блока 9 и всех блоков 10 ввода-вывода. Управляющий выход операционного блока 5 соединен с шиной 12 управления, к которой подключены управляющие входы всех блоков модуля 2. В состав однонаправленной шины 12 управления входят следующие управляющие одноразрядные линии:- линии 56.15 б.п 1 селекции одноименных блоков 10. 1, , 10. и ввода-вывода, соединенные с управляющими входами соответствующихблоков 10;- линия 57 селекции памяти, соединенная с управляющим входом блока6 памяти- линия 58 селекции блоков хранения идентификаторов, соединеннаяс управляющими входами всех блоков7 хранения идентификаторов логических каналов;- линия 59 селекции блоков хранения индикаторов процессоров, соединенная с управляющими входами всех блоков 8 хранения индикаторов процессоров;- линия 60 селекции приоритетного блока, соединенная с управляющим входом приоритетного блока 9;- линии 61 и 62 чтения и записи,- линии 63 управления узлами приоитетного блока.Двунаправленную шину 13 данных можно представить в виде совокупности следующих однонаправленных шин, которые обеспечивают четкое представление о характере взаимодействияблоков модуля- информационная шина 64, соединяющая вход-выход операционного бло" ка 5 с входами-выходами блока 6 памяти, блоков 7 хранения идентифика.торов логических каналов, блоков 8 хранения индикаторов процессоров, приоритетного блока 9 и блоков 1 О ввода-вывода и обеспечивающая передачу данных из операционного блока 5 во все другие блоки модуля;- шина 65 данньж памяти, соединяющая вход-вьход блока 6 памяти со входом-выходом операционного блока 5 и,предназначенная для передачи данных, хранящихся в памяти в операционный блок 5- шина бб передачи индентификаторов, соединяющая входы-выходы блоков 7 хранения идентификаторов логических каналов со входом-выходом операционного блока 5 и обеспечивающая передачу кодов идентификаторов в операционный блок 5;- шина 67 передачи индикаторов, соединяющая входы-выходы блоков 8 хранения индикаторов процессоров со входом-вьжодом операционного блока 5 и обеспечивающая передачу кодов индикаторов в операционный блок 5,- шина 68 передачи кодов свободных идентификаторов, соединяющая вход-выход приоритетного блока 9со входом-выходом операционного блока 5 и обеспечивающая передачу двоичных кодов выделенных.идентификаторов в операционный блок 5;5- шина 69 передачи входной информации, соединяющая входы-выходы блоков 10 ввода-вывода со входом-выходом операционного блока 5 и обеспечивающая передачу в операционный 1 О блок 5 входной информации, полученной блоком 10 извне.Блок 6 памяти обеспечивает хранение программ и данных, в том числе и буферируемьк данных, принятых из вне.Блоки 7 хранения идентификаторов обеспечивают запоминание идентификаторов, которые используются при передаче по установленным ранее логи О ческим каналам связи через данный модуль 2 информации между парами взаимосвязанных таким образом терминальных модулей. Число блоков 7 соответствует числу физических кана лов данного коммутационного модуля 7. Емкость каждого из блоков 7 определяется числом логических каналов связи, которые можно установить через данный модуль 2. ЗОБлоки 8 хранения индикаторов процессоров используются для хранения служебной информации, обеспечивающей поиск свободньк процессоров 4 различных типов, подключенных к системе 1 коммутации, по соответствующему Физическому каналу связи, Емкость блока, 8 определяется числом типов процессоров 4. Разрядность кажррй ячейки каждого блока 8 равна единице. Число блоков .8 равно л .Приоритетный блок 9 предназначен для выделения свободного в данном коммутационном модуле 2 идентификатора при установлении нового логического канала связи, создаваемого в процессе поискасвободного процессора,1Блоки 10 ввода-вывода обеспечивают взаимодействие данного модуля 2 с другими модулями 2 и 3. Каждый из блоков 10 имеет внешний вход-выход, который образует один физический канал связи коммутационного модуля 2.При отсутствии сигналов селекции 55 блока 1 О, так же, как и блоков 6-9, входы"выходы этих блоков, соединенные с шиной 13 данных, находятся в третьем состоянии (имеют высокий им педанс),Терминальный модуль 3 (фиг. 3) включает операционный блок 15, который аналогичен блоку 5 и предназначен для логической обработки принимаемой модулем 3 информации, а также обеспечивает управление остальными блоками модуля 3, Вход-выход операционного блока 15 соединен через шину 23 данных со входами-выходами всех остальных блоков модуля 3, Адресный выход операционного блока 15 соединен с шиной 2 1 адреса, к которой подключены адресные входы блока 16 памяти, блока 17 хранения идентиФикаторов, блока 18 хранения индикаторов процессоров, приоритетного блока 19 и двух блоков 20 ввода-вывода. Управляющий выход операционного блока 15 соединен с шиной 22 управления, к которой подключены управляющие входы всех блоков модуля 3. В состав шины 22 управления входят управляющие линии, аналогичные перечисленным для шины 12 управления . Двунаправленная шина 23 данных также может быть представлена в виде совокупности однонаправленных шик, аналогичньк перечисленным для шины 13 данньк.Блох 16 памяти, который аналогичен блоку 6, обеспечивает хранение программ, а также данных, в том числе и буферируемых данньк, принятых извне.Блок 17 хранения идентификаторов обеспечивает запоминание имен процессоров, активизированных в подключенном к данному модулю 3 процессоре и взаимодействующих с процессами в других процессорах 4, и идентификаторов занятых логических каналов связи, которые используются при передаче по установленным ранее логическим каналам связи через данный модуль 3 информации к взаимосвязанным с данным модулем 3 другим терминальным модулем 3. Емкость блока 17 определяется числом логических каналов связи, которые можно установить через данный модуль 3. Блок 18 хранения индикаторов процессоров аналогичен блоку 8, и используется для хранения служебной ин. - Формации, обеспечивающей поиск свободных процессоров 4 различных типов, 12495241 О подключенных к системе 1 коммутации, Емкость блока 18, так же, как и блоков 8, .определяется числом типов процессоров 4. Разрядность каждой ячейки блока 18 равна единице.Приоритетный блок 19 аналогичен блоку 9 и предназначен для формирования свободного в данном терминальном модуле 3 идентификатора при установлении нового логического канала связи, создаваемого в процессе поискасвободного процессора.Два блока 20 ввода-вывода обеспечивают взаимодействие данного модуля3 с процессором 4 и одним иэ коммутационных модулей 2 первого уровня,Каждый из двух блоков 20 имеет внешний вход-выход, который образуетодин иэ двух входов-выходов терминального модуля 3. При отсутствиисигналов селекции блока 20, так жекак и блоков 16 - 19, входы-выходыэтих блоков, соединенные с шиной 23данных, находятся в третьем состоянии (имеют высок:й импеданс),Каждый из операционных блоков 5и 15 (фиг. 4) содержит регистр 25микропрограммного адреса, которыйпредназначен для запоминания на одинмикрокомандный цикл текущего микропрограммного адреса. Его выход соединен с адресным входом блока 26 храненйя микропрограмм, обеспечивающегопри этом выдачу соответствующей мик- Зрокоманды на свои выходы. Первый выход блока 26 (поле формирования следующего адреса микрокоманды) соединен с первыми входами коммутатора 27микропрограммного адреса и коммутатора 28 адреса ветвления. Второй выход блока 26 (поле задания либо альтернативного микропрограммного адре,са, либо кода базового адреса) сое- .динен с первым входом коммутатора 4535 базового адреса и со вторымвходомкоммутатора 28 адреса ветвления,Третий выход блока 26 соединен синформационным входом регистра 29микрокоманды. 501 Коммутатор 27 микропрограммного адреса обеспечивает передачу кода адреса на свой выход, соединенный с информационным входом регистра 25, 55 с одного из двух входов, в зависимости от управляющего сигнала на своем управляющем входе. Коммутатор 28 адреса ветвленияобеспечивает передачу кода адреса на свой .выход, соединенный со вторым входом коммутатора 27, с одного из двух входов, в зависимости от сигнала переноса на своем управляющем входе.Регистр 29 микрокоманды обеспечивает запоминание на цикл некоторых полей текущей микрокоманды.Первый выход регистра 29 (поле управления типом микропрограммного перехода) соединен с управляющим входом коммутатора 27. Второй выход регистра 29 (поле кода операции) соединен с управляющим входом арифметико-логического блока 30. Третий выход регистра 29 (поле адреса результата операции) соединен с информационным входом дешифратора 33 записи, Четвертый выход регистра 29 (поле управления режимом шины 13/23 данных) соединен с управляющим входом первого буферного усилителя 34.Пятый выход регистра 29 (поле выбора базового адреса) соединен с управляющим входом коммутатора 35 базового адреса. Шестой выход регистра 29 (поле загрузки) соединен с управляющим входом регистра 36 селекции. Седьмой выход регистра 29 (поле управления периферийными блоками модуля 2(3) является составной частью управляющего выхода блока 5(15), который соединен с шиной 12 (22) управления. С седьмым выходом регистра 29 микрокоманды соединены линии 6 1 и 62 чтения и записи и линии 63 управления узлами приоритетного блока 9(19).Арифметико-логический блок 30 предназначен для арифметико-логической обработки информации, поступающей на два его входа, в соот етствии с кодом операции на его управляющем входе. Результат операции появляется на информационном выходе блока 30, соединенном с информационными входами регистров 31 и 32; признак результата операции формируется на выходе сигнала переноса блока 30, соединенном с управляющим входом коммутатора 28. Регистр 31 результата обеспечивает запоминание результата текущей операции блока 30 при наличии сигнала записи на его управляющем входе.Выход регистра 31 соединен с первымвходом блока 30 и информационнымвходом первого буферного усилителя 34,5Регистр 32 адреса обеспечиваетзапоминание результата текущей операции блока 30 при наличии сигналазаписи на его управляющем входе. Выход регистра 32 является адреснымвыходом операционного блока 5(15),который соединен с шиной 11(21) адресаДешифратор 33 записи обеспечивает формирование на одном из своихвыходов сигнала записи в зависимостиот двоичного кода на информационномвходе при наличии синхросигнала на управляющем входе. Первый выход дешифратора 33 соединен с управляющим 2 р входом регистра 31, а второй выход - с управляющим входом регистра 32.Первый буферный усилитель 34 обеспечивает передачу кода операнда на СВОЙ ВыхОД ЯвлЯющийсЯ ВхОДОм-Выхо дом операционного блока 5(15) и соединенный со вторым входом коммутатора 35 базового адреса, со своего информационного входа В зависимости от разрешающего сигнала на своем управляющем входе. При отсутствии разрешающего сигнала выход усилителя 34 находится в третьем состоянии.Коммутатор 35 базового адреса обеспечивает передачу унитарного кодаЗ 5 адреса на свой выход, соединенный с информационным входом регистра Зб селекции, с одного иэ двух входов, в зависимости от сигнала на своем управляющем входе, 40Регистр 36 селекции обеспечивает запоминание унитарногокода адреса при наличии сигнала загрузки на его управляющем входе. Выход регистра 36 является составной частью управляющего выхода блока 5(15). Единичный сигнал в одном из разрядов регистра 36 обеспечивает выбор соответствующего блока модуля 2(3) для текущей с ним работы (выполнение цикла записи или чтения), С выходом регистра 36 селекции соединены линии 56 селекции блоков 10(20) Ввода-Вывода, линия 57 селекции блоков 6(16) памяти, линия 58 селекции блоков 55 7(17) хранения индификаторов логических каналов, линия 59 селекции блоков 8(18) хранения индикаторов процессоров, линия 60 селекции приоритетного блока 9(19).Генератор 37 синхроимпульсов обес пе ивает выработку непрерывной последовательности синхроимпульсов на своем выходе, который соединен с управляющими входами регистра 25, регистра 29, дешифратора 33. Период следования синхроснгналов определяет микрокомандный цикл блока 5(15).Приоритетный блок 9(19) содержит (Фиг. 5) регистр 38 свободных идентификаторов, предназначенный для хранения суперпозиции унитарных кодов свободных идентификаторов, когорые используются для маркировки вновь устанавливаемых через данный модуль 2(3) логических каналов. Выход регистра 38 соединен со входом приоритетной схемы 39, с первым входом первой группы 42 элементов И и с первым Входом группы 44 элементов ИЛИ.Приоритетная схема 39 обеспечивает формирование на выходе, соединенном со входом шифратора 40 идентификатора логического канала и через группу 41 элементов НЕ со вторым входом первой группы 42 элементов И, унитарного кода старшего единичного разряда из суперпозиции унитарных кодов, присутствующей на ее входе. В таблице показано правило Функционирования восьмиразрядной приоритетной схемы 39.Шифратор 40 идентификатора логического канала обеспечивает преобразование унитарного кода со своего входа в двоичный код на выходе соединенном с информационным входом второго буферного усилителя 46.Первая группа 42 элементов И предназначена для формирования пос" ле очередного выделения унитарного кода свободного идентификатора логического канала новой, скорректированной суперпозиции унитарных кодов, в которой выделенный унитарный код погашен, Выход группы 42 элементов И соединен с первым информационньм входом коммутатора 43 идентификаторов.Коммутатор 43 идентификаторов обеспечивает передачу информации на свой выход, соединенный с информационным Входом регистра 38 свободных идентификаторов, с одного издвух входов, в зависимости от управляющего сигнала на своем управляющем входе.Дешифратор 45 идентификатора обеспечивает преобразование двоичного кода вновь освободившегося идентификатора со своего входа в унитарный код идентификатора на выходе, соединенном через группу 44 элемен тов ИЛИ со вторым информационным входом коммутатора 43 идентификаторов.Второй буферный усилитель 46 обеспюивает выдачу информации с 15 выхода шифратора 40 идентификатора логического канала на шину 13(23) данных при наличии разрешающего сигнала на управляющем входе. При отсутствии разрешающего сигнала выход 20 .буферного усилителя 46 находится в третьем состоянии.Вторая группа 47 элементов И предназначена для выделения управляющих сигналов с шины 12(22) управления, 25. адресованных к дан ому приоритетному блоку 9(19), Первые входы всех элементов И группы 47 объединены и соединены с линией 60 селекции, являющейся составной частью управляющего входа блока 9(19). Вторые входы элементов И группы 47 соединены соответственно с другими управляющими сигналами, поступающими с управляющего входа блока 9(19) по Управляющим линиям 63. Первый выход группы 47 соединен с управляющим входом коммутатора 43 идентификаторов. Второй выход соединен с синхровходом регистра 38 свободных идентификаторов. Третий выход соединен с установочным входом регистра 38 и обеспечивает начальную установку в единицу всех унитарных кодов. Четвертый выход соединен с управляющим входом 45 второго буферного усилителя 46. Каждый из блоков 10(20) ввода-вывода содержит (фиг6) выходной регистр 48, обеспечивающий запомина 50 ние выдаваемого информационного слова, которое присутствует на шине 13(23) данных, при наличии сигналов записи и селекции на входе загрузки и селектирующем входе. Выход ре 55 гистра 33 соединен с выходной информационной шиной одного из внешних входов-выходов 14(24) - физических каналов связи модуля 2(3). Вход-выход блока 10(20), подключенный к шине 13(23) данных соединен с информационными входами регистра 48, регистра 50 управления выдачей и регистра 51 управления приемом. Адресный вход блока 10(20), ,подключенный к шине 11(21) адреса,соединен с информационным входом дешифратора 52 адреса и адресным входом коммутатора 54 входной информации.Управляющий вход блока 10(20), подключенный к шине 12(22) управления, включает в себя линию 56 селекции данного блока 0(20), соединенную с первыми входами всех элементов и третьей группы 53, а также с управляющим входом дешифратора 52 адреса, линии чтения 6 1 и записи 62, которые подключены ко вторым вхбдам соответствующих элементов И группы 53.Элементы И группы 53 обеспечивают передачу сигналов со своих вторых входов на выходы при наличии разре- шающего сигнала на линии селекции.Первый выход (линия записи) элементов И группы 53 соединен с синхровходами регистров 48, 49, 50 и 51; второй выход (линия чтения) соединен с управляющим входом третьего буферного усилителя 55.Регистры 50 управления выдачей и 5 1 управления приемом предназначены для синхронизации обмена информацией по физическому каналу в режиме передачи и приема соответственно. Их выходы являются составной частью внешнего входа-вых 1 да 14(24) данного блока 10(20) ввода-вывода.Регистр 49 приема информации обеспечивает запоминание входного слова и передачу его на свой выход, соединенный с первым входом коммутатора 54 входной информации.Дешифратор 52 адреса обеспечивает декодирование двоичного кода адреса регистра данного блока 10(20).Четыре его выхода соединены с селектирующими входами соответственно регистров 48, 50, 49 и 51.Коммутатор 54 входной информации обеспечивает передачу информации на свой выход с одного из трех входов в зависимости от двоичного кода на своем адресном входе. Второй и третий информационный входы предназначены для передачи входных управляю 13 1249524щих сигналов иэ физического канала связи и соединены с линиями, образующими часть линий внешнего входавьгхода 14(24) блока 10(20) ввода- вывода. Выход коммутатора 54 соеди-. нен с информационным входом третьего буферного усилителя 55.Третий буферный усилитель 55 обеспечивает передачу информации на свой выход для последующего ее анализа в блоке 5(15) со своего информационного входа в зависимости от присутствия разрешающего сигнала чтения на своем управляющем входе. В про тивном случае выход буферного усили, теля 55 находится в третьем состоянии. Внешний вход-выход 14(24) блока 10(20) ввода-вывода образует один физический канал связи модуля 2(3). Физический канал связи составляют следующие линии и шины:- выходная информационная шина 70;" выходная линия 71 запроса наг 5 сеанс связи;- выходная линия 72 установки выдаваемого слова;входная информационная шина 73;- выходная линия 74 разрешения сеанса связи;- выходная линия 75 квитирования принятого слова;- входная линия 76 запроса на сеанс связи, 35- входная линия 77 установки входного слова;- входная линия 78 разрешения сеанса связи;- входная линия 79 квитирования 40 выданного слова.Блоки 6-8, 16-18 могут быть реализованы на микросхемах оперативного запоминающего устройства. Коммутаторы 27, 28, 35, 43 и 54 - на микро схемах мультиплексоров. Дешифраторы 33, 45 и 52, а также шифратор 40 - на соответствующих микросхемах. Приоритетную схему 39 можно реализовать с помощью элементов И-НЕ. В ка честве другого варианта реализации приоритетной схемы 39 и шифратора 40 можно использовать микросхему приоритетного шифратора. Регистры 25, 31, 32, 36 и 38 могут быть реа лизованы на соответствующих микросхемах, блок 26 хранения микропрограмм - на микросхемах ПЗУ, блок 30 - на микросхемах АЛУ, Для реализации генератора 37 может быть использована микросхема одновибратора.Регистры 48-51 могут быть реализованы на соответствующих микросхемах.В качестве другого примера реализации блока ввода-вывода 10(20) можноиспользовать БИС программируемогопараллельно интерфейса. Буферныеусилители 34, 46 и 55 могут бытьреализованы на микросхемах шинныхформирователей, а элементы И, ИЛИ,НЕ - на соответствующих микросхемах.Система работает следующим образом,Каждый процессор 4, подключенныйк терминальному модулю 3 системы 1коммутации, может находиться в свободном (пассивном) или в активном(занятом) состоянии, Свободные процессоры 4 переходят в активное состояние по коммутационным командамот других активных процессоров 4при установлении между ними логических каналов связиПоиск свободногопроцессора 4 осуществляется в техслучаях, когда. любому активному процессору 4, выполняющему некотороезадание, становится необходим, например, дополнительный ресурс памятиили дополнительный процессор 4 (вычислительный ресурс) определенноготипа для непосредственного распарал"леливания вычислительного процесса.Поиск свободного процессора 4 иодновременное установление логического канала к нему осуществляетсядецентрализованно коммутационнымимодулями 2 на основании служебнойинформации (индикаторов), имеющейсяв каждом иэ них и динамически отображающей наличие в текущий момент свободных процессоров из числа процессоров 4, подключенных к системе 1.Первоначально состояние индикаторов всех типов в блоках 8 и 18 хранения индикаторов процессоров каждого коммутационного модуля 2 и кажгдого терминального модуля 3 соответственно устанавливается при ини-.циализации системы, а затем постоянно корректируется в процессе работысистемы путем выдачи каждым терминальным модулем 3 после изменениясостояния своего процессора соответствующей коммутационной команды (алгоритмы на фиг. 8-11). Когда любойО 15 20 процессор 4 типа о становится свободным, он выдает об этом сообщение всвой терминальный модуль 3, которыйформирует коммутационную команду"Установка индикатора ц -го типа,Онараспространяется по всем коммутационным модулям 2 и воспринимаетсявсеми другими терминальными модулями 3. Принимая по 1 -му физическомуканалу связи эту команду, каждыйкоммутационный модуль 2 проверяетсостояние индикатора в ,1 -м разрядеячейкиблока 8 хранения индикаторов маршрутов. Если индикатор равенединице, то команда блокируется. Впротивном случае устанавливается вединичное состояние соответствующийиндикатор в блоке 8, а команда выдается в остальные физические каналысвязи кроме д -го канала в соответствии со слсдующим правилом.Если команда поступила в модуль 2с более низкого ( -1)-го уровня по-му физическому каналу связи из 25числа г физических каналов связи,то команда передается во все физические каналы связи, ведущие на более высокий ипи тот же уровни структуры при условии, что индикаторы типапо другим физическим каналамиз числа г, кроме 1 -го физическогоканала, равны нулю (условие А). Команда должна выдаваться в каждый физический канал из числа г , не рав 35ный , если индикаторы типаповсем другим физическим каналам изчисла ь, кроме данного, равны нулю(условие Б) .Если команда поступила с болеевысокого или того же уровней по некоторому физическому каналу 1 изчисла (Ь+К) каналов модуля 2, тоона выдается в любой другой физический канал, если выполняется условие Б,Когда любой процессор 4 типастановится занятым, он выдает в свойтерминальный модуль 3 соответствующее сообщение. По этому сообщению вмодуле формируется и выдается в смеж 50ный коммутационный модуль 2 коммутационная команда "Сброс индикатора-го типа", по которой каждый модуль2, принимая ее по-му физическомуканалу, устанавливает в нуль-й индикатор в строке ) блока 8. Условиявыдачи этой команды в другие физические каналы аналогичны описанным,При необходимости поискадопол 1 нительного ресурса свободного процессора 4) типалюбой активный процессор 4 выдает в свой терминальный модуль 3 соответствующцй запрос и сообщает при этом имя порта процесса - инициатора запроса. Из регистра 38 свободных идентификаторов приоритетного блока 19 в данном модуле 3 выделяется код свободногоидентификатора, который после этогосчитается занятым, что фиксируетсяв соответствующем разряде регистра38 данного модуля 3. Затем в модуле 3 производится взаимная привязкаимени порта и вновь занятого идентификатора, что и означает установление логического канала связи черезданный модуль 3. Для этого осуществляется запись кода выделенногоидентификатора в блок 17 храненияидентификаторов в первую половинуячейки по адресу, определяемому именем порта, а также запись имени порта во вторую половину ячейки блока17 по адресу, равному коду выбранного идентификатора. После этогомодуль 3 формирует и выдает коммутационную команду "Установка логического канала к свободному процессору типа", Эта команда сопровождается следующими параметрами:идентификатором, соответствующимданному логическому каналу и индикатором . При получении этой команды по-му физическому каналу через, -й блок 10 ввода-вывода каждый коммутационный модуль 2 проверяет наличиеиндикаторов в строке о блока 8 индикаторов процессоров. Если они есть,то из них вьщеляется наиболее предпочтительный индикатор, соотв"тствующий физическому каналу Ь из числа г , кроме физического канала зИэ регистра 38 свободных идентифи-каторов (фиг, 5) выделяется унитарный код наиболее приоритетного свободного идентификатора. В соответствии с правилом функционирования приоритетной схемы 39 (см. таблицу),это будет старший по номеру идентификатор. Первая группа элементов И42 формирует новую суперпоэицию унитарных кодов, в которой вьщеленный унитарный код вновь занимаемогоидентификатора погашен. При подаче

СмотретьЗаявка

3786222, 24.08.1984

ЛЕНИНГРАДСКИЙ ИНСТИТУТ АВИАЦИОННОГО ПРИБОРОСТРОЕНИЯ

ГОРБАЧЕВ СЕРГЕЙ ВЛАДИМИРОВИЧ

МПК / Метки

МПК: G06F 15/163

Метки: коммутации, многоуровневая, модульная, процессоров

Опубликовано: 07.08.1986

Код ссылки

<a href="https://patents.su/18-1249524-modulnaya-mnogourovnevaya-sistema-kommutacii-processorov.html" target="_blank" rel="follow" title="База патентов СССР">Модульная многоуровневая система коммутации процессоров</a>

Предыдущий патент: Устройство для сопряжения двух электронных вычислительных машин

Следующий патент: Устройство для сопряжения процессоров в вычислительных сетях

Случайный патент: Дозатор сыпучих кормов