Процессор быстрого преобразования уолша-адамара

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1795471

Авторы: Гнатив, Коссов, Ширмовский

Текст

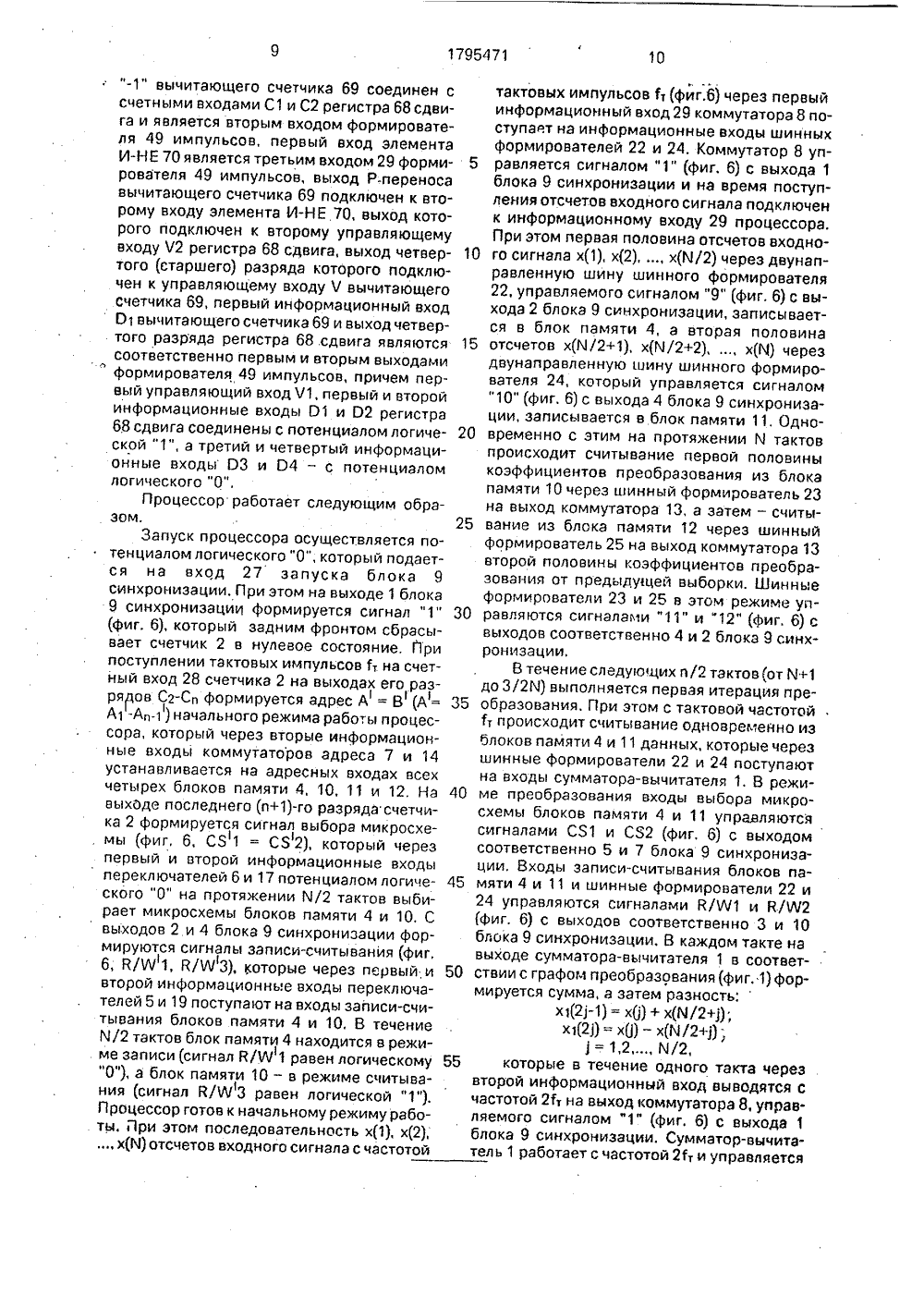

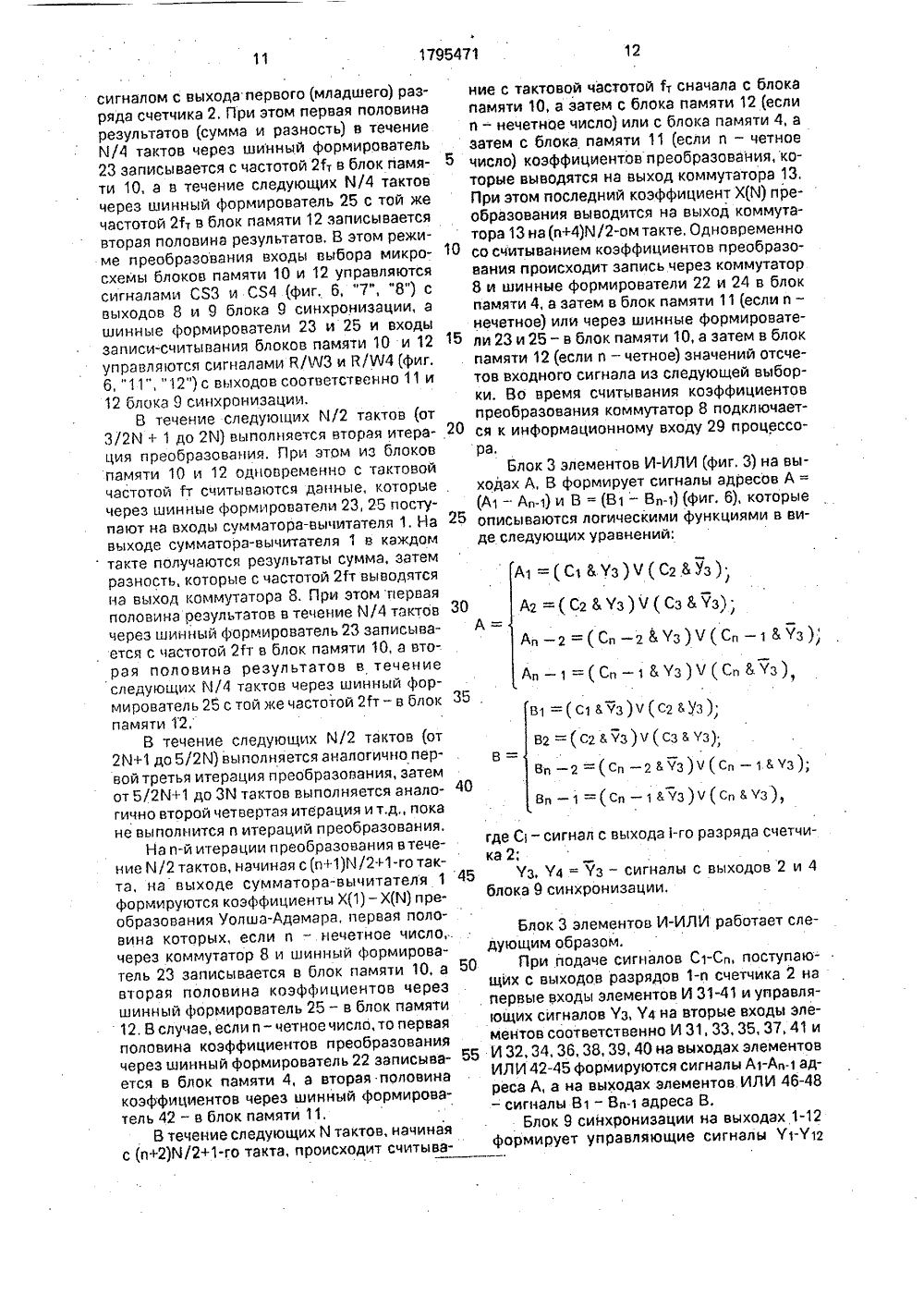

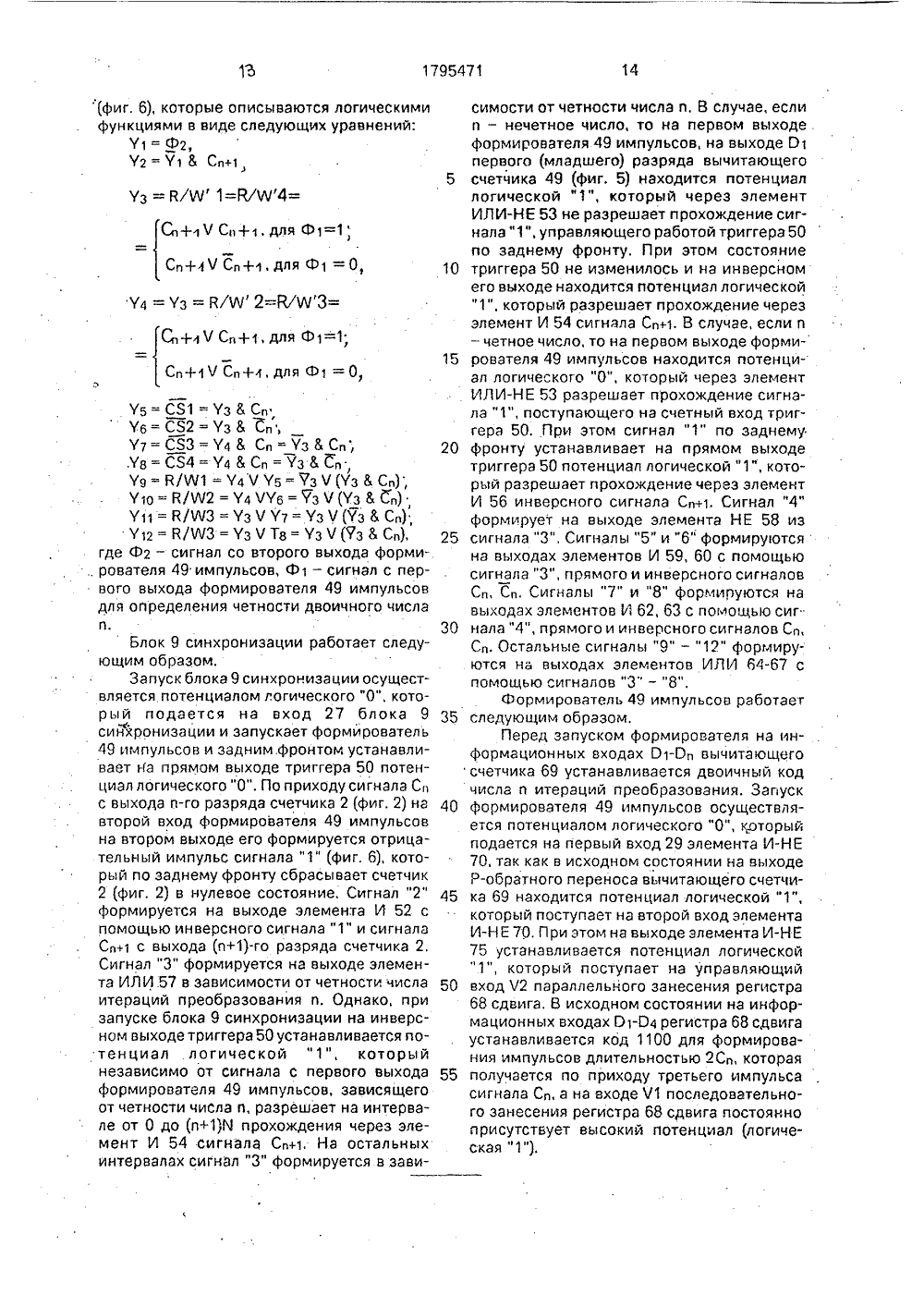

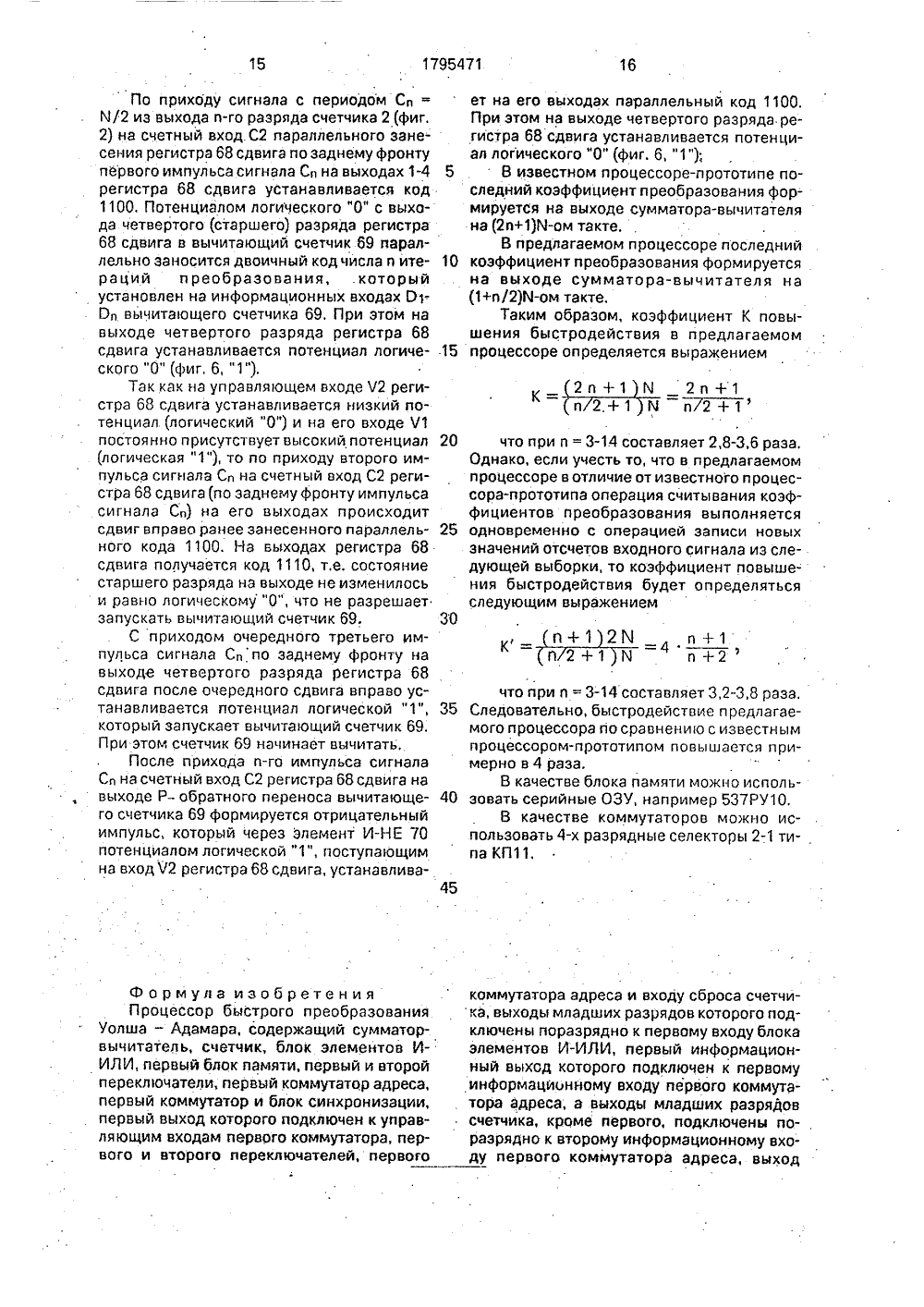

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 795471 А 1 1)5 6 06 Р 15/332 ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕВЕДОМСТВО СССР(ГОСПАТЕНТ СССР) ПИСАНИЕ ИЗОБРЕТЕНИ ВТОРСКОУУ С ТЕЛЬС В, М. Глуш ко- .А.Гнатив и ики Коссо тельство15/332, 444653 982кл.О(54) ПРОЦЕССОР БЪС ВАНИЯ УОЛША - АДА (57) Изобретение отно вычислительной техни польэовано для обраб ТРОГО ПМАРАсится к аке и можотки циф РЕОБ томатике и т быть исвых сигнд(21) 4795393/24(56) Авторское свидеМ 951320, кл, О 06 ГПатент США М15/332, 1984. Изобретение относится к области автоматики и вычислительной техники и может быть использовано для обработки изображений; для спектрального и корреляцион ного анализа, цифровой фильтрации, сжатия информации, в системах связи и т,д,Известно устройство ортогонального преобразователя цифровых си налов по Уолшу - Адамару, содержащее блок Фоомирования временных интервалов, 2 М (й=2"- размерность преобразования) блоков элементов И, И блоков элементов ИЛИ, М регистров и М сумматоров-вычитателей.Недостатком такого устройства является его сложность из-за большого числа регистров и сумматоров-вычитателей.Известно устройство, содержащее шесть коммутаторов, три регистра сдвига,лов, в системах обработки иэображений, для спектрального и корреляционного анализа, цифровой фильтрации, сжатия информации, в системахсвязи и т.д, Целью изобретения является повышение быстродействия процессора. Процессор дополнительно содержит три блока памяти, второй коммутатор, второй коммутатор адреса, шесть переключателей, элемент НЕ и четыре шинных формирователя. Это позволяет распараллелить работу блоков памяти в режиме считывания данных, поступающих на сумматор-вычитатель и совместить считывание коэффициентов преобразования и запись новых входных данных, что повышает быстродействие процессора примерно в четыре раза. 6 ил,сумматор-вычитатель и блок синхронизации.Недостатком этого устройства является низкое быстродействие и его сложность из- О за наличия многокаскадных регистров сдви- И3 ь. га.Наиболее близким по технической сущности является процессор быстрого преобразования Уолша - Адамара, содержащий сумматор-вычитатель, счетчик, первый и второй регистры, блок элементов И-ИЛИ, блок памяти, первый и второй переключатели, коммутатор адреса, коммутатор, две ячейки хранения промежуточных данных (ЯХПД), схему модификации адреса, триггер, четыре элемента И и блок синхронизации, первый выход которого подключен к управляющим входам коммутатора, первого1795471 Иванова акт орректор А.Козориз каз 432 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж, Раушская наб 4/5 Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101 Аз 4 Составитель Л.ГнативТехред М.Моргентали второго переключателей, коммутатора адреса, ЯХПД, входам сброса счетчика, первого и второго регистров и триггера, выходы младших разрядов счетчика и выходы регистров подключены поразрядно к первому входу блока элементов И-ИЛИ, первый информационный выход которогоподключен к первому информационному входу коммутатора адреса, а выходы младших разрядов счетчика, кроме первого, и выходы схемы модификации адреса подключены к второму информационному входу коммутатора адреса, выход которого подключен к адресному входу блока памяти, входы управления записью/считыванием и выбора микросхемы которого подключены к выходам соответственно первого и второго переключателей, выход и-го разряда счетчика подключен к входу сброса блока синхронизации, второй выход которого подключен к второму входу блока элементов И-ИЛИ и первому информационному входу первого переключателя, второй информационный вход которого подключен к третьему входу блока синхронизации и к выходу первого элемента И, второй вход которого соединен с шестым выходом блока синхронизации, четвертый выход которого подключен к третьему входу блока элементов И-ИЛИ, выход (и+1)-го разряда счетчика подклочен к входу окончания итерации блока синхронизации и первому информационному входу второго переключателя, второй информационный вход которого. подключен к пятому выходу блока синхронизации, вход размера преобразования и вход запуска которого являются соответственно входом размера преобразования и входом запуска устройства, тактовым и информационным входами которого являются соответственно счетный вход счетчика и первый информационный вход коммутатора, второй информационный вход которого подключен к выходу сумматора-вычитателя, тактовый вход которого подключен к выходу первого разряда счетчика, выход второго регистра подключен к второму входу третьего элемента И, выход коммутатора подключен к информационному входу блока памяти, выход которого является выходом процессора и через ЯХПД подключен к информационным входам сумматора-вычитателя, первые входы второго, третьего и четвертого элементов И и второй вход триггера подключены к третьему выходу блока синхронизации, четвертый выход которого подключен к управляющим входам сумматора-вычитателя и блока элементов И-ИЛИ,Недостатком этого процессора является низкое быстродействие из-за последова 50 55 ции, второй выход которого подключен к второму информационному входу восьмого переключателя, управляющий вход которого соединен с управляющими входами третьего, четвертого, пятого, шестого и седьмого переключателей, второго коммутатора адреса и подключен к первому выходу блока синхронизации, четвертый выход которого подключен к вторым информационным входам третьего и седьмого переключателей, выход(п+1)-го разряда счетчика тельного считывания и записи промежуточных данных в блок памяти, При этом все коэффициенты преобразования считываются из блока памяти за 2 й(п+1) тактов.5 Цель изобретения - повышение быстродействия процессора за счет распараллеливания работы блоков памяти в режиме считывания данных, поступающих на сумматор-вычитатель, и совмещения режима 1 О считывания коэффициентов преобразования и записи новых входных данных.Это достигается тем, что в процессорвведены три блока памяти, второй коммутатор, второй коммутатор адреса, шесть пере ключателей, элемент НЕ и четыре шинныхформирователя, причем выход первого коммутатора подключен к информационным входам первого, второго, третьего и четвертого шинных формирователей, информаци онные входы-выходы которых подключены кинформационным выходам-входам соответственно первого, второго, третьего и четвертого блоков памяти, выходы первого., и второго шинных формирователей подклю чены к первым информационным входамсумматора-вычитателя и второго коммутатора, выход которого является информационным выходом устройства, выходы третьего и четвертого шинных формирователей под- ЗО ключены к вторым информационным входам сумматора-вычитателя и второго коммутатора, управляющий вход которогогподключен к шестому выходу блока синхронизации, седьмой, восьмой и девятый выхоЗ 5 ды которого подключены к первыминформационным входам соответственно четвертого, пятого и шестого переключателей, выходы которых подключень 1 к входам выбора микросхемы соответственно третье го, второго и четвертого блоков памяти, входы разрешения записи-считывания которых соединены с управляющими входами соответственно третьего, второго и четвертого шинныхформирователей и подключены к 45 выходам соответственно третьего, седьмогои восьмого переключателей, первые информационные входь 1 которых подключены соответственно к десятому, одиннадцатому и двенадцатому выходам блока синхронизаподключен к второму информационному входу пятого переключателя и входу элемента НЕ, выход которого подключен к вторым информационным входам четвертого и шестого переключателей, второй информационный выход блока элементов И-ИЛИ и выходы младших разрядов счетчика подключены соответственно к первому и второму информационным входам второго коммутатора адреса, выход которого подключен к адресным входам второго и чет 10 вертого блоков памяти, выход первого коммутатора адреса подключен к адресному входу третьего блока памяти, а выход 15 преобразования Уолша-Адамара; на фиг. 2 - функциональная схема процессора, на фиг. 3 - схема блока элементов И-ИЛИ; на фиг. 4 - схема блока синхронизации, на фиг.5- схема формирователя импульсов; на фиг.6 - временная диаграмма работы процессора для М = 16 (И = 2"-размерность преобразования).Процессор содержит сумматор-вычитатель 1, счетчик 2, блок элементов И-ИЛИ 3, первый блок памяти 4, первый и второй переключатели 5 и 6, первый коммутатор адреса 7, первый коммутатор 8, блок синхронизации 9, три блока памяти 10-12, второй коммутатор 13, второй коммутатор адреса 14, шесть переключателей 15-20, элемент НЕ 21 и четыре шинных Формирователя 22-25, причем первый выход блока синхронизации 9 подключен к управляющим входам первого коммутатора 8, первого и второго переключателей 5 и 6, первого коммутэтора адреса 7 и входу сброса счетчика 2, выходы младших разрядов 1-и которого подключены поразрядно к первому входу блока элементов И-.ИЛИ 3, первый информационный выход которого подключен к первому информационному входу А первого коммутатора адреса 7, а выходы младших разрядов 2-и счетчика 2, кроме первого, подключены поразрядно к второму информационному входу А первого коммутатора адреса 7, выход которого подключен к адресному входу первого блока памяти 4, выходы управления записью/считыванием й/61 и выбора микросхемы СЯ 1 которого подключены к выходам соответственно первого и второго переключателей 5 и 6, выход 55 и-го разряда счетчика 2 подключен к входу сброса блока синхронизации 9, второй выход которого подключен к второму входу блока элементов И-ИЛИ 3 и первому информационному входу первого переключателя первого переключателя подключен к управляющему входу первого шинного формирователя,Нэ фиг. 1 представлен граф быстрого 20 25 30 35 40 45 50 5, второй информационный вход которого подключен к третьему выходу В/Ю 1 блока синхронизации 9, четвертый выход которого подключен к третьему входу блока элементов И-ИЛИ 3, выход п+1)-го разряда счетчика 2 подключен к входу окончания итерации блока синхронизации 9 и первому информационному входу второго переключателя 6, второй информационный вход которого подключен к пятому выходу СЯ 1 блока синхронизации 9, вход 26 размера преобразования и вход 27 запуска которого являются соответственно входом размера преобразования и входом запуска устройства, тактовым и информационным входами которого являются соответственно счетный вход 28 счетчика 2 и первый информационный вход 29 первого коммутатора 8, второй информационный вход которого подключен к выходу сумматора-вычитателя 1, тактовый вход которого подключен к выходу первого разряда счетчика 2, выход первого коммутатора 8 подключен к информационным входам первого, второго, третьего и четвертого шинных формирователей 22-25, информационные входы-выходы которых подключены к информационнь м выходам-входам соответственно первого, второго, третьего и четвертого блоков памяти 4, 10, 11 и 12, выходы первого и второго шинных формирователей 22, 23 подключены к первым информационным входам сумматора-вычитателя 1 и второго коммутатора 13, выход 30 которого является информационным выходом устройства, выходы третьего и четвертого шинных формирователей 24, 25 подключены к вторым информационным входам сумматора-вычитателя 1 и второго коммутатора 13, управляющий вход которого подключен к шестому выходу блока синхронизации 9, седьмой, восьмой и девятый выходы СЯ 2-СЯ 4 которого подключены к первым информационным входам соответственно четвертого, пятого и шестого перекл ючателей 16-18, выходы которых подключены к входам выбора микросхемы соответственно третьего, второго и четверто о блоков памяти 11, 10 и 12, входы разрешения записи-считывания которых соединены с управляющими входами соответственно третьего, второго и четвертого шинных формирователей 24, 23, 25 и подключены к выходам соответственно третьего, седьмого и восьмого переключателей 15, 19 и 20, первые информационные входы ко- . торых подключены соответственно к десятому, одиннадцатому и двенадцатому выходам Я/й/2 - В/И/4 блока синхронизации 9, второй выход которого подключен к второму информационному входу восьмогопереключателя 20, управляющий вход которого соединен с управляющими входами третьего, четвертого, пятого, шестого и седьмого переключателей 15-19, второго коммутатора адреса 14 и подключен к первому выходу блока синхронизации 9, четвертый выход которого подключен к вторым информационным входам третьего и седьмого переключателей 15 и 19, выход (и+1)-го разряда счетчика 2 подключен к второму информационному входу пятого переключателя 17 и к входу элемента НЕ 21, выход которого подключен к вторым информационным входам четвертого и шестого переключателей 16 и 18, второй информационный выход блока элементов И-ИЛИ 3 и выходы младших разрядов 2-и счетчика 2 подключены соответственно к первому и второму информационным входам В и В второго коммутатора адреса 14, выход которого подключен к адресным входам второго и четвертого блоков памяти 10 и 12, выход первого коммутатора адреса 7 подключен к адресному входу третьего блока памяти 11, а выход первого переключателя 5 подключен к управляющему входу первого шинного формирователя 22,Счетчик 2 является (и+1)-разрядным двоичным счетчиком,Все блоки памяти 4, 10, 11 и 12 емкостью МЛа бит, где в - число разрядов одного отсчета входного сигнала.Блок 3 элементов И-ИЛИ (фиг,З) содеркит элементы И 31-41 и элементы ИЛИ 42- 48, причем первые входы элементов И 31-41 являются входами С 1-С 2 блока элементов И-ИЛИ 3, первый управляющий вход которого соединен с вторыми входами элементов И 31, 33, 35, 37 и 41, а второй управляющий вход соединен с вторыми входами элементов И 32, 34, 36, 38-40, выходы элементов И 31-38 попарно подключены к входам элементов ИЛИ 42-45, выходы А 1-Апкоторых представляют адрес А и являются первым выходом А блока 3 элементов ИИЛИ, выходы элементов И ЗЗ и 39 подключены к входам элемента ИЛИ 46, выходы элементов И 37 и 40 подключены к входам элемента ИЛИ 47, выходы элементов И 36 и 41 подключены к входам элемента ИЛИ 48, выходы В 1-В- элементов ИЛИ 46-48 представляют адрес В и являются вторым выходом В блока 3 элементов И-ИЛИ.Блок 9 синхронизации (фиг. 4) содержит формирователь 49 импульсов, триггер 50, элемент НЕ 51, элемент И 52, элемент ИЛИНЕ 53, элемент И 54, элемент НЕ 55, элемент И 56, элемент ИЛИ 57, элемент НЕ 58, элемент И 59,60, элемент НЕ 61, элементы И 62, 63 и элементы ИЛИ 64-67, причем45 ется выходом 10 блока 9 синхронизации,5055 5 10 15203035 40 первый вход 26 формирователя 49 импульсов является входом задания размера преобразования, второй вход формирователя 49 импульсов является входом сброса блока 9 синхронизации и соединен с вторыми входами элементов И 59, 62 и с входом элемента НЕ 61, выход которого подключен к вторым входам элементов И 60, 63, третий вход 27 формирователя 49 импульсов является входом запуска блока 9 синхронизации и соединен с входом сброса триггера 50, счетный вход которого соединен с выходом элемента ИЛИ-НЕ 53, первьй выход формирователя 49 импульсов подключен к второму входу элемента ИЛИ-НЕ 53, второйвыход формирователя 49 импульсов является выходом 1 блока 9 синхронизации и через элемент НЕ 51 подключен к первым входам элементов И 52 и ИЛИ-НЕ 53, второй входэлементаИ 52 является входом окончанияитерации блока 9 синхронизации и соединен с вторь 1 м входом элемента И 54 и через элемент НЕ 55 соединен с вторым входом элемента И 56, инверсный и прямой выходы триггера 50 подключены к первым входам элементов И соответственно 54 и 56, выходы котОрых подключены к входам элемента ИЛИ 57, выход элемента И 52 является выходом 6 блока 9 синхронизации, выход злемента ИЛИ 57 является выходом 2 блока 9 синхронизации и подключен к элементу НЕ 58, к первым входам элементов И 59, 60 и к первым входам элементов ИЛИ 66, 67, выход элемента НЕ 58 является выходом 4блока 9 синхронизации и подключен к первым входам элементов И 62, 63 и к первым входам элементов ИЛИ 64, 65, выход элемента И 59 является выходом 5 блока 9 син хронизации и подключен к второму входу элемента ИЛИ 64, выход которого является выходом 3 блока 9 синхронизации, выход элемента И 60 является выходом 7 блока 9 синхронизации и подключен к второму входу элемента ИЛИ 65, выход которого являвыход элемента И 62 является выходом 8 блока 9 синхронизации и подключен к второму входу элемента ИЛИ 66, выход которого является выходом 11 блока 9 синхронизации, выход элемента И 63 является выходом 9 блока 9 синхронизации и подключен к второму входу элемента ИЛИ 67, выход которого является выходом 12 блока 9 синхронизации.Формирователь 49 импульсов фиг. 5) содержит регистр 68 сдвига, вычитающий счетчик 49 и элемент И-НЕ 70, причем информационные входы 01-О вычитающего счетчика 69 являются первым входом 28 формирователя 49 импульсов, счетный вход"-1" вычитающего счетчика 69 соединен с счетными входами С 1 и С 2 регистра 68 сдвига и является вторым входом формирователя 49 импульсов, первый вход элемента И-НЕ 70 является третьим входам 29 формирователя 49 импульсов, выход Р-переноса вычитающего счетчика 69 подключен к второму входу элемента И-НЕ 70, выход которого подключен к второму управляющему входу Ч 2 регистра 68 сдвига, выход четвертого (старшего) разряда которого подключен к управляющему входу Ч вычитающего счетчика 69, первый информационный вход 01 вычитающего счетчика 69 и выход четвертого разряда регистра 68.сдвига являются соответственно первым и вторым выходами формирователя 49 импульсов, причем первый управляющий вход Ч 1, первый и второй информационные входы 01 и 02 регистра 68 сдвига соединены с потенциалом логической "1", а третий и четвертый информационные входы 03 и 04 - с потенциалом логического "0",Процессор работает следующим образом.Запуск процессора осуществляется потенциалом логического "0", который подается на вход 27 запуска блока 9 синхронизации. При этом на выходе 1 блока 9 синхронизации формируется сигнал "1" (фиг. 6), который задним фронтом сбрасывает счетчик 2 в нулевое состояние. При поступлении тактовых импульсов 1 на счетный вход 28 счетчика 2 на выходах его разря 1 ов С 2-Сп формируется адрес А = В (А= А 1-Ап) начального режима работы процессора, который через вторые информационные входы коммутаторов адреса 7 и 14 устанавливается на адресных входах всех четырех блоков памяти 4, 10, 11 и 12. На выходе последнего (и+1)-го разряда счетчика 2 формируется сигнал выбора микросхе. мы (фиг, 6, СЯ 1 = С 52), который через первый и второй информационные входы переключателей 6 и 17 потенциалом логического "О" на протяжении М/2 тактов выбирает микросхемы блоков памяти 4 и 10. С выходов 2 и 4 блока 9 синхронизации формируются сигналы записи-считывания (фиг, б, й/Ю 1, Я/В/3), которые через первый и1второй информационные входы переключателей 5 и 19 поступают на входы записи-считывания блоков памяти 4 и 10. В течение К/2 тактов блок памяти 4 находится в режиме записи (сигнал Вдб 1 равен логическому "0"), а блок памяти 10 - в режиме считывания (сигнал й/В/3 равен логической "1").1Процессор готов к начальному режиму рабо. ты. При этом последовательность х(1), х(2), , х(й) отсчетов входного сигнала с частотой тактовых импульсов 1 т (фиг,б) через первыйинформационный вход 29 коммутатора 8 поступает на информационные входы шинныхформирователей 22 и 24. Коммутатор 8 уп 5 равляется сигналом "1" (фиг, 6) с выхода 1блока 9 синхронизации и на время поступления отсчетов входного сигнала подключенк информационному входу 29 процессора.При этом первая половина отсчетов входно 10 го сигнала х(1), х(2)х(И/2) через двунаправленную шину шинного формирователя22, управляемого сигналом "9" (фиг, 6) с выхода 2 блока 9 синхронизации, записывается в блок памяти 4, а вторая половина15 отсчетов х(М/2+1), х(К/2+2), , х(М) черездвунаправленную шину шинного формирователя 24, который управляется сигналом"10" (фиг. 6) с выхода 4 блока 9 синхронизации, записывается в блок памяти 11. Одно 20 временно с этим на протяжении И тактовпроисходит считывание первой половиныкоэффициентов преобразования из блокапамяти 10 через шинный формирователь 23на выход коммутатора 13, а затем - считы 25 вание из блока памяти 12 через шинныйформирователь 25 на выход коммутатора 13второй половины коэффициентов преобразования от предыдущей выборки. Шинныеформирователи 23 и 25 в этом режиме уп 30 равляются сигналами "11" и "12" (фиг. 6) свыходов соответственно 4 и 2 блока 9 синхронизации,В течение следующих и/2 тактов(от 8+1до 3/2 К) выполняется первая итерация пре 35 образования. При этом с тактовой частотой,Г происходит считывание одновременно изблоков памяти 4 и 11 данных, которые черезшинные формирователи 22 и 24 поступаютна входы сумматора-вычитателя 1. В режи 40 ме преобразования входы выбора микросхемы блоков памяти 4 и 11 управляютсясигналами СЯ 1 и СЯ 2 (фиг, 6) с выходомсоответственно 5 и 7 блока 9 синхронизации. Входы записи-считывания блоков па 45 мяти 4 и 11 и шинные формирователи 22 и24 управляются сигналами й/Я 1 и И/О/2(фиг. 6) с выходов соответственно 3 и 10блока 9 синхронизации. В каждом такте навыходе сумматора-вычитателя 1 в соответ 50 ствии с графом преобразования (фиг, 1) формируется сумма, а затем разность;х 1(2)-1) = х + х(й/2+Д;хс(2 = х( - х(Й/2+;1=1,2 М 2,55 которые в течение одного такта черезвторой информационный вход выводятся счастотой 2 Гт на выход коммутатора 8, управ.ляемого сигналом "1" (фиг. 6) с выхода 1блока 9 синхронизации. Сумматор-вычитатель 1 работает с частотой 21 т и управляется30А=35 40 сигналом с выхода первого (младшего) разряда счетчика 2. При этом первая половина результатов (сумма и разность) в течение М 4 тактов через шинный формирователь 23 записывается с частотой 21 т в блок памяти 10, а в течение следующих й/4 тактов через шинный формирователь 25 с той же частотой 2 б в блок памяти 12 записывается вторая половина результатов, В этом режиме преобразования входы выбора микросхемы блоков памяти 10 и 12 управляются сигналами СЯЗ и СЯ 4 (фиг. 6, "7", "8") с выходов 8 и 9 блока 9 синхронизации, а шинные формирователи 23 и 25 и входы записи-считывания блоков памяти 10 и 12 управляются сигналами Р/ЮЗ и ЯЮ 4 (фиг, 6, "11", "12") с выходов соответственно 11 и 12 блока 9 синхронизации.В течение следующих М/2 тактов (от 3/2 й + 1 до 2 К) выполняется вторая итерация преобразования. При этом из блоков памяти 10 и 12 одновременно с тактовой частотой 1 т считываются данные, которые через шинные формирователи 23, 25 поступают на входы сумматора-вычитателя 1. На выходе сумматора-вычитателя 1 в каждом такте получаются результаты сумма, затем разность, которые с частотой 21 т выводятся на выход коммутатора 8. При этомпервая половина результатов в течение Й/4 тактов через шинный формирователь 23 записывается с частотой 21 т в блок памяти 10, а вторая половина результатов в течение следующих Й/4 тактов через шинный формирователь 25 с той же частотой 21 т- в блок памяти 12.В течение следующих й/2 тактов (от 2 й+1 до 5/2 И) выполняется аналогично первой третья итерация преобразования, затем от 5/28+1 до ЗМ тактов выполняется аналогично второй четвертая итерация и т.д., пока не выполнится и итераций преобразования На и-й итерации преобразования в течение М/2 тактов, начиная с(и+1)й/2+1-го такта, на выходе сумматора-вычитателя 1 формируются коэффициенты Х(1) - Х(М) преобразования Уолша-Адамара, первая половина которых, если и - нечетное число, через коммутатор 8 и шинный формирователь 23 записывается в блок памяти 10, а вторая половина коэффициентов через шинный формирователь 25 - в блок памяти 12, В случае, если и - четное число, то первая половина коэффициентов преобразования через шинный формирователь 22 эаписывается в блок памяти 4, а вторая половина коэффициентов через шинный формирователь 42 - в блок памяти 11,В течение следующих М тактов, начиная с (и+2)Й/2+1-го такта, происходит считывание с тактовой частотой бт сначала с блока памяти 10, а затем с блока памяти 12 (если и - нечетное число) или с блока памяти 4, а затем с блока памяти 11 (если и - четное 5 число) коэффициентов преобразования, которые выводятся на выход коммутатора 13, При этом последний коэффициент Х(М) преобразования выводится на выход коммутатора 13 на (и+4)И/2-ом такте, Одновременно "0 со считыванием коэффициентов преобразования происходит запись через коммутатор 8 и шинные формирователи 22 и 24 в блок памяти 4, а затем в блок памяти 11 (если и - нечетное) или через шинные формировате ли 23 и 25 - в блок памяти 10, а затем в блокпамяти 12 (если и - четное) значений отсчетов входного сигнала из следующей выборки. Во время считывания коэффициентов преобразования коммутатор 8 подключает ся к информационному входу 29 процессора.Блок 3 элементов И-ИЛИ (фиг. 3) на выходах А, В формирует сигналы адресов А = (А 1 - Ап) и В = (В 1 -Вп) (фиг, 6), которые 25 описываются логическими функциями в виде следующих уравнений: А 1 =(С аУЗ)ч(С 2 аУЗ);А 2 = ( С 2Уз ) ч ( СзУ 31А - 2 =(С - 2 ЬУз) ч (С - 1 8 Уз)А. - 1=(С. - 1 аУЗ) ч(с. ГАУЗ) в 1=(с 1 ачз)ч(С 2 ьУз);В 2 =- (С 2 8, ЧЗ ) Ч ( СЗ Ъ ЧЗ)Вп - 2 = (Сп - 2 Й ЧЗ )Ч (Сп - 1 Ь ЧЗ); Вп - 1=(С, - 1 аЧЗ)Ч(Сп аЧЗ),где С - сигнал с выхода 3-го разряда счетчика 2;45 УЗ, У 4 = Уз - сигналы с выходов 2 и 4 блока 9 синхронизации. Блок 3 элементов И-ИЛИ работает следующим образом.50 При подаче сигналов С 1-Сп, поступающйх с выходов разрядов 1-и счетчика 2 на первые входы элементов И 31-41 и управляющих сигналов Уз, У 4 на вторые входы элементов соответственно И 31, ЗЗ, 35, 37, 41 и 55 И 32, 34, 36, 38,39,40 на выходах элементовИЛИ 42-45 фарМИруатСя СИГНаЛЫ А 1-Ападреса А, а на выходах элементов ИЛИ 46-48 - СИГНаЛЫ В 1 - ВпадрЕСа В.Блок 9 синхронизации на выходах 1-12формирует управляющие сигналы У 1-У 12(фиг. 6), которые описываются логическимифункциями в виде следующих уравнений:У 1= Фг,Уг = У 1Сп+1,Сп+4 Ч Сп+1, дЛя Ф 1=1,Сп+4 Ч Сп+1, дЛя Ф 1 = О,У 4 = Уз = ЯЛВ 2=В/Ю 3= Сп+4 Ч Сп+1, ддя Ф 1=1;Сп+1 Ч Сп+4, для Ф 1 = О,У 5 = СЯ 1 = УЗ В СпУ 5 = С 52 = УЗ Ь СпУ 7 = С 3 = У 4 В Сп = УЗСп,У 8 = СЯ 4 = У 4 Ъ Сп = УЗ 8 Гп ,У 9 = В/Ю 1 = У 4 Ч У 5 = уз Ч (УЗ 8 Сп);У 10 = Й/И 2 = У 4 ЧУ 6 = 73 Ч (Уз( и)У 11 = К/И/3 = УЗ Ч У 7 = УЗ Ч (УЗСп);У 12 = Й/ЧЧЗ = Уз Ч Т 8 = Уз Ч (тз Рв Сп),где Ф 2 - сигнал со второго выхода форми. рователя 49 импульсов, Ф 1 - сигнал с перваго выхода формирователя 49 импульсовдля определения четности двоичного числаи.Блок 9 синхронизации работает следующим образом.Запуск блока 9 синхронизации осуществляется потенциалом логического "0", который подается на вход 27 блока 9сийхронизации и запускает формйрователь49 импульсов и задним. фронтом устанавливает на прямом выходе триггера 50 потенциал логического "0". По приходу сигнала Сс выхода и-го разряда счетчика 2 (фиг. 2) навторой вход формирователя 49 импульсовна втором выходе его формируется отрицательный импульс сигнала "1" (фиг. 6), который по заднему фронту сбрасывает счетчик2 (фиг. 2) в нулевое состояние. Сигнал "2"формируется на выходе элемента И 52 спомощью инверсного сигнала "1" и сигналаСп+1 с выхода (и+1)-го разряда счетчика 2,Сигнал "3" формируется на выходе элемента ИЛИ.57 в зависимости от четности числаитераций преобразования и. Однако, призапуске блока 9 синхронизации на инверсном выходе триггера 50 устанавливается потенциал логической "1", которыйнезависимо от сигнала с первого выходаформирователя 49 импульсов, зависящегоат четности числа и, разрешает на интервале от 0 до (и+1)й прохождения через элемент И 54 сигнала Сп+1, На остальныхинтервалах сигнал "3" формируется в зави 5 10 15 20 25 30 35 симости от четности числа и. В случае, если и - нечетное число, то на первом выходе . формирователя 49 импульсов, на выходе 01 первого (младшего) разряда вычитающего счетчика 49 (фиг. 5) находится потенциал логической "1", который через элемент ИЛИ-НЕ 53 не разрешает прохождение сигнала "1", управляющего работой триггера 50 по заднему фронту. При этом состояние тригера 50 не изменилось и на инверсном его выходе находится потенциал логической "1", который разрешает прохождение через элемент И 54 сигнала Сп+1, В случае, если и - четное число, то на первом выходе формирователя 49 импульсов находится потенциал логического "0", который через элемент ИЛИ-НЕ 53 разрешает прохождение сигнала "1", поступающего на счетный вход триггера 50. При этом сигнал "1" по заднему фронту устанавливает на прямом выходе триггера 50 потенциал логической "1", который разрешает прохождение через элемент И 56 инверсного сигнала Сп+1. Сигнал "4" формирует на выходе элемента НЕ 58 из сигнала "3", Сигналы "5" и "6" формируются на выходах элементов И 59, 60 с помощью сигнала "3", прямого и инверсного сигналов Сп, Сп. Сигналы "7" и "8" формипуются на выходах элементов И 62, 63 с помощью сигнала "4", прямого и инверсного сигналов Сп, Сп Остальные сигналы "9" - "12" формируются на выходах элементов ИЛИ 64-67 с помощью сигналов "3" - "8",Формирователь 49 импульсов работает следующим образом.Перед запускам формирователя на инфаРмаЦионных вхоДах Р 1-Рп вычитаюЩего счетчика 69 устанавливается двоичный код числа и итераций преобразования. Загуск формирователя 49 импульсов осуществляется потенциалом логического "0", который подается на первый вход 29 элемента И-НЕ 70, так как в исходном состоянии на выходе Р-обратного переноса вычитающего счетчика 69 находится потенциал логической "1", который поступает на второй вход элемента И-НЕ 70, При этом на выходе элемента И-НЕ 75 устанавливается потенциал логической 1", который поступает на управляющий вход Ч 2 параллельнога занесения регистра 68 сдвига. В исходном состоянии на информационных входах Р 1-Р 4 регистра 68 сдвига устанавливается код 1100 для формирования импульсов длительностью 2 Сп, которая получается по приходу третьего импульса сигнала Сп, а на входе Ч 1 последовательного занесения регистра 68 сдвига постоянно присутствует высокий потенциал (логическая "1").16 1795471 По приходу сигнала с периодом Сп =М/2 из выхода и-го разряда счетчика 2 (фиг.2) на счетный вход.С 2 параллельного занесения регистра 68 сдвига по заднему фронтупервого импульса сигнала Сп на выходах 1-4 5регистра 68 сдвига устанавливается код1100. Потенциалом логического "0" с выхода четвертого (старшего) разряда регистра68 сдвига в вычитающий счетчик 69 параллельно заносится двоичный код числа и итераций преобразования, .которыйустановлен на информационных входах ООп вычитающего счетчика 69. При этом навыходе четвертого разряда регистра 68сдвига устанавливается потенциал логиче- .15ского "О" (фиг, 6, "1"),Так как на управляющем входе Ч 2 регистра 68 сдвига устанавливается низкий потенциал (логический "0") и на его входе Ч 1постоянно присутствует высокий потенциал 2(логическая "1"), то по приходу второго импульса сигнала Сп на счетный вход С 2 регистра 68 сдвига (по заднему фронту импульсасигнала Сп) на его выходах происходитсдвиг вправо ранее занесенного параллельного кода 1100. На выходах регистра 68сдвига получается код 1110, т.е, состояниестаршего разряда на выходе не изменилосьи равно логическому "0", что не разрешаетзапускать вычитающий счетчик 69. 3С приходом очередного третьего импульса сигнала Сппо заднему Фронту навыходе четвертого разряда регистра 68сдвига после очередного сдвига вправо устанавливается потенциал логической "1", 35который запускает вычитающий счетчик 69.При этом счетчик 69 начинает вычитать,После прихода и-го импульса сигналаС на счетный вход С 2 регистра 68 сдвига навыходе Р- обратного переноса вычитающего счетчика 69 формируется отрицательныйимпульс, который через элемент И-НЕ 70потенциалом логической "1", поступающимна вход Ч 2 регистра 68 сдвига, устанавлива 45 2 и+1п 72;- 1О что при и = 3-14 составляет 2,8-3,6 раза,Однако, если учесть то, что в предлагаемом процессоре в отличие от известного процессора-прототипа операция считывания коэффициентов преобразования выполняется 5 одновременно с операцией записи новыхзначений отсчетов входного сигнала из следующей выборки, то коэффициент повышения быстродействия будет определяться следующим выражениемО К -и+1 и+2 3,2-3,8 раза. е предлагаес известным шается приожно испольер 537 РУ 10,в можно искторы 2-1 ти 0 Уолш вычит ИЛИ, перек первы первь ляющ вого ормула изобретения роцессор быстрого преобразования а - Адамара, содержащий сумматор- атель, счетчик, блок элементов И- первый блок памяти, первый и второй лючатели, первый коммутатор адреса, й коммутатор и блок синхронизации, й выход которого подключен к управим входам первого коммутатора, пери второго переключателей, первого ет на его выходах параллельный код 1100. При этом на выходе четвертого разряда регистра 68 сдвига устанавливается потенциал логического "0" (фиг. 6, "1");В известном процессоре-прототипе последний коэффициент преобразования формируется на выходе сумматора-вычитателя на (2 и+1)И-ом такте.В предлагаемом процессоре последний коэффициент преобразования формируется на выходе сумматора-вычитателя на (1+и/2)М-ом такте.Таким образом, коэффициент К повышения быстродействия в предлагаемом процессоре определяется выражением что при и = 3-14 составляе Следовательно, быстродейств мого процессора по сравнени процессором-прототипом пов мерно в 4 раза,В качестве блока памяти м зовать серийные ОЗУ, наприм 8 качестве коммутаторо пользовать 4-х разрядные селе па КП 11, коммутатора адреса и входу сброса счетчика, выходы младших разрядов которого подключены поразрядно к первому входу блока элементов И-ИЛИ, первый информационный выход которого подключен к первому информационному входу первого коммутатора адреса, а выходы младших разрядов счетчика, кроме первого, подключены поразрядно к второму информационному входу первого коммутатора адреса, выходкоторого подключен к адресному входу первого блока памяти, входы управления записью-считыванием и выбора микросхемы которого подключены к выходам соответственно первого и второго переключателей, 5 выход и-го разряда счетчика подключен к входу сброса блока синхронизации, второй выход которого подключен к второму входу блока элементов И-ИЛИ и первому информационному входу первого переключателя, 10 второй информационный вход второго подключен к третьему выходу блока синхронизации, четвертый выход которого подключен к третьему входу блока элементов И-ИЛИ, выход (и+1)-го разряда счетчика 15 подключен к входу окончания итерации блока синхронизации и первому информационному входу второго переключателя, второй информационный вход которого подключен к пятому выходу блока синхронизации, вход 20 размера преобразования и вход запуска которого являются одноименными входами процессора. тактовым и информационным входами которого являются соответственно счетный вход счетчика и первый информа ционный вход первого коммутатора, второй информационный вход которого подключен к выходу сумматора-вычитателя, тактовый вход которого подключен к выходу первого разряда счетчика, о т л и ч а ю щи й с я тем, ЗО что, с целью повышения быстродействия, в него введены три блока памяти, второй коммутатор, второй коммутатор адреса, шесть переключателей, элемент НЕ и четыре шинных формирователя, причем выход первого 35 коммутатора подключен к информационным входам с первого по четвертый шинных формирователей, информационные входы- выходы которых подключены к информационным выходам-входам соответственно с 40 первого по четвертый блоков памяти, выходы первого и второго шинных формирователей подключены к первым информационным входам сумматора-вычитателя и второго коммутатора, выход которого является 45 информационным выходом процессора, выходы третьего и четвертого шинных формирователей подключены к вторым информационным входам сумматора-вычитателя и второго коммутатора, управляющий вход которого подключен к шестому выходу блока синхронизации, седьмой, восьмой и девятый выходы которого подключены к первым информационным входам соответственно четвертого, пятого и шестого переключателей, выходы которых подключены к входам выбора микросхемы соответственно третьего, второго и четвертого блоков памяти, входы разрешения записи-считывания которых соединены с управляющим входами соответственно третьего, второго и четвертого шинных формирователей и подключены к выходам соответственно третьего, седьмого и восьмого переключателей, первые информационные входы которых подключены соответственно к десятому. одиннадцатому и двенадцатому выходам блока синхронизации, второй выход которого подключен к второму информационному входу восьмого переключателя, управляющий вход которого соединен с управляющими входами с третьего по седьмой переключателей, второго коммутатора адреса и подключен к первому выходу блока синхронизации, четвертый выход которого подключен к вторым информационным входам третьего и седьмого переключателей, выход (и+1-го разряда пятого счетчика подключен к второму информационному входу пятого переключателя и входу элемента НЕ, выход которого подключен к вторым информационным входам четвертого и шестого переключателей, второй информационный выход блока элементов И-ИЛИ и выходы младших разрядов счетчика подключены соответственно к первому и второму информационным входам второго коммутатора адреса, выход которого подключен к адресным входам второго и четвертого блоков памяти, выход первого коммутатора адреса подключен к адресному входу третьего блока памяти, выход первого переключателя - к управляющему входу первого шинного формирователя.

СмотретьЗаявка

4795393, 25.12.1989

ИНСТИТУТ КИБЕРНЕТИКИ ИМ. В. М. ГЛУШКОВА

ГНАТИВ ЛЕВ АЛЕКСЕЕВИЧ, КОССОВ ВЛАДИМИР ЕВГЕНЬЕВИЧ, ГНАТИВ МИРОН АЛЕКСЕЕВИЧ, ШИРМОВСКИЙ ГЕННАДИЙ ЯКОВЛЕВИЧ

МПК / Метки

МПК: G06F 15/332

Метки: быстрого, преобразования, процессор, уолша-адамара

Опубликовано: 15.02.1993

Код ссылки

<a href="https://patents.su/13-1795471-processor-bystrogo-preobrazovaniya-uolsha-adamara.html" target="_blank" rel="follow" title="База патентов СССР">Процессор быстрого преобразования уолша-адамара</a>

Предыдущий патент: Устройство для моделирования систем массового обслуживания

Следующий патент: Магнитооптическое устройство для реализации дискретного преобразования фурье

Случайный патент: Подставка для удилища